650 V高压型超结结构MOSFET器件设计与性能研究

摘要:功率MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)作为绝缘栅控制的开关型器件,因其功率大,驱动简单,应用越来越广泛。采用深槽刻蚀填充技术设计的650 V高压型超结结构MOSFET器件,主要应用于汽车充电桩等电源管理,力求在保持参数不变的前提下,优化导通电阻。通过工艺仿真技术测试功率MOSFET器件的性能,研究了槽偏移距离以及掺杂浓度对导通电阻和击穿电压的关系。结果表明,槽偏移会导致超结部分的电荷不平衡,槽偏移不论正负,只要是在同一水平位置,那么两者的总电荷数就是不同的。在柱宽不变的情况下,随着浓度的增加,其击穿电压和导通电阻都缓慢下降,并且导通电阻随着掺杂浓度的提高而降低。本研究对半导体领域器件设计优化和提升具有一定的参考意义。

关键词:超结MOSFET;工艺仿真;深槽刻蚀填充技术;半导体

中图分类号:TN386文献标识码:A文章编号: 1001-2443(2024)01-0027-06

引言

自从电被发现以来,人们在日常生活中已经离不开电了。电能应用中功率电子器件使用频繁,而半导体功率器件的使用率占据前端,并且半导体功率器件已经应用到生活的方方面面[1]。

导通损耗还有它处于关闭状态下的转换效率以及所能承受的最大反向电压,是半导体功率器件关注的重点问题,因此开发出功率MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor),其目的是逐步获得更高的器件功率和频率,但是它会存在击穿电压和导通电阻矛盾的问题,而超结MOSFET的出现解决了这个问题,超结MOSFET虽然已经有了很大的突破,但在实际应用中国内还缺少成熟设备与其匹配,所以研发一款超结结构MOSFET器件来适应国内主流市场是非常有必要的[2]。

为了更好的适应国内环境,本研究通过分析其工作原理,使用仿真工艺,设计出了650 V高压型超结结构MOSFET器件的基本模型,通过简单的测试验证了其可行性。

1 研究理论与方法

1.1 超结结构MOSFET的基本结构及制作工艺

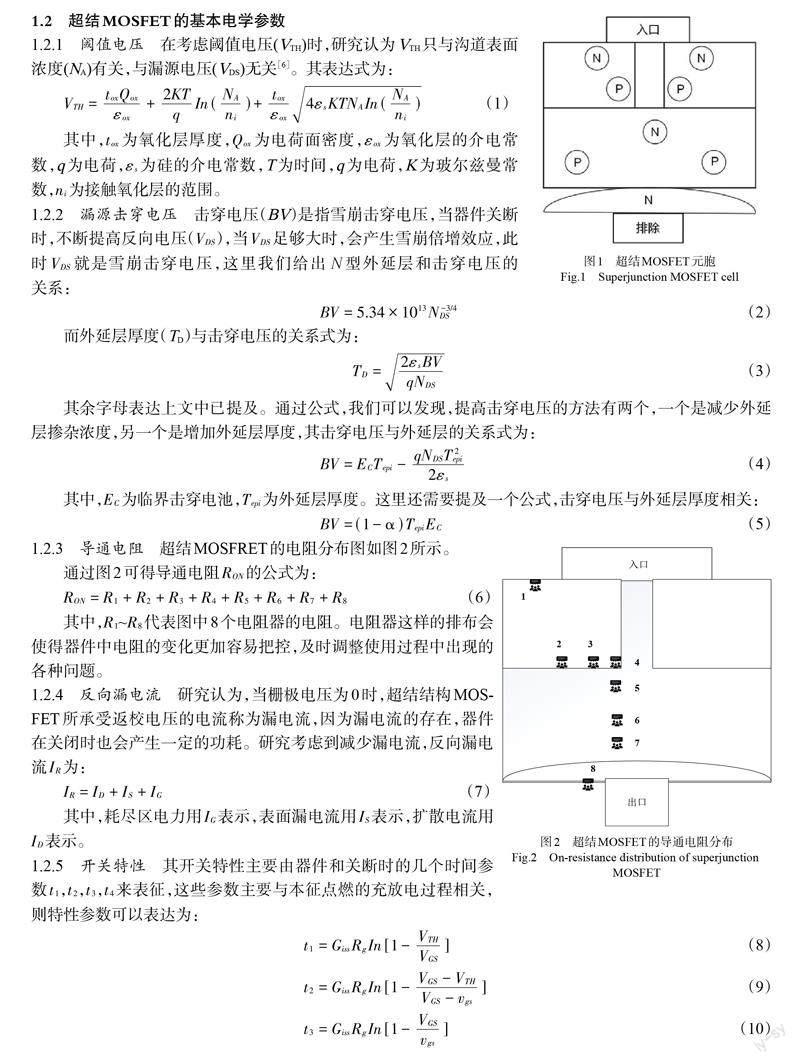

超结器件在承受反向电压时,利用电荷平衡的原理,这样会使得电场更均匀。其基本构造如图1所示。

半导体器件制造工艺主要有三种[3]:(1)多次外延技术,无论是制作工艺还是设备的要求都是很低,它是通过外延生长完指定厚度的外延层后,将晶圆从外延炉中取出并光刻,然后进行离子注入工艺,通过重复该操作,直到厚度满足设计要求[4]。(2)通过在n型外延层上直接进行深刻蚀,形成p型区所需要的槽,然后进行氮型外延回填刻蚀所形成的深槽,比起多次外延技术就不会存在超结结构不均匀的问题。(3)高能离子注入技术,它是对多次外延技术的优化,其优势是可以有效减少高温炉中退火的时间和光刻次数[5]。

1.2 超结MOSFET的基本电学参数

1.2.1 阈值电压 在考虑阈值电压(VTH)时,研究认为VTH只与沟道表面浓度(NA)有关,与漏源电压(VDS)无关[6]。其表达式为:

式中,[Giss]为输入电容,[Rg]为栅极电阻,[VTH]为阈值电压,[vgs]为内部栅源电压,[VGS]为总栅源电压。

1.3 超结MOSFET的数学模型

半导体器件领域,有一套适用任何半导体器件的数学模型[7]。在仿真模拟的过程中,任何通用的器件模拟器内部求解的方程都是相同的,这些方程都是根据统一的定律——麦克斯韦定律导出的,每一个方程都在发挥着自己的作用[8]。

1.4 超结MOSFET体二极管反向恢复原理

超结MOSFET器件体内有一个多子器件,即寄生体二极管,但是与传统半导体器件不同的是在超结MOSFET器件正向导通时,依然会存在载流子存储效应[9]。而在高频电路中应用器件时,会频繁的开启和关闭,所以器件体内的寄生体二极管会在关闭时产生反向恢复,对此它的反向恢复机制就对实验的研究起到相当重要的作用[10]。

当搭配感性负载电流给超结MOSFET器件,电路开启时会对电感进行充能,而当所给的感性负载电流停止突变时,电感就会向超结MOSFET器件释放能量,体二极管会正向导通。并且再次施加反向高压给器件时,P柱和N柱之间的耗尽区会快速展宽,超结MOSFET器件开始承受高压[11]。此时电场会施加一个作用力排出存储的电荷,那么就会导致反方向上的电流增大,进而达到反向峰值电流,这个时候会因为存储电荷的减少,反向电流不足以维持下去,并且在存储电荷被完全排除之前,電流会一直减少,之后反向恢复结束[12]。

2 结果与分析

2.1 槽刻蚀与填充工艺仿真

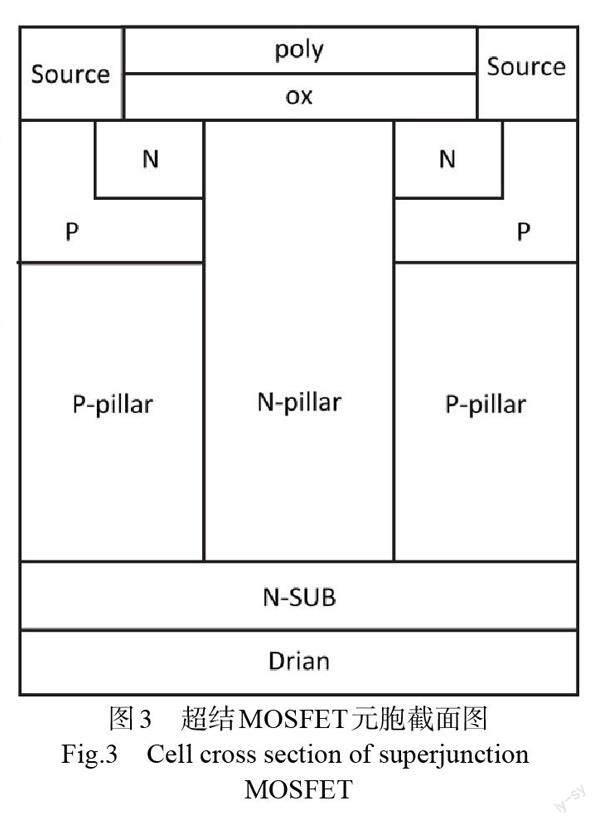

这里实验选取深槽刻蚀填充技术进行研究,通过模拟其对器件电学特性的影响,来判断该技术制造出超结器件的优良性,在器件的实际设计中,需留一定的电压余量,避免出现不可控的情况,导致器件损坏。因此研究选择留75 V的电压余量,实验所用击穿电压为725 V,综合参数计算,可以确定外延层厚度约46 μm,掺杂浓度为[3×1013cm-3],以及P柱和N柱的宽度为10 μm。图3为仿真设计的超结MOSFET器件元胞的基本结构,从图3可以发现我们在制得的超级结构基础中,对n离子区和n离子源区进行离子注入,使得其金属化,并且选择超结部分的某一水平位置进行切线,可以得到净掺杂浓度分布的一维图像。

通过图像来对超结结构中离子浓度的分布进行研究,结果如图4所示。可以发现不同位置的P柱和N柱的浓度是不一样的,P柱会在一定程度上影响超结结构的电荷平衡。并且,从图中也可以看到P柱的有效高度减小很多。

2.2 槽偏移对器件特性的影响

研究發现,槽刻蚀填充技术对比多次外延技术的优势就是更加方便,一次外延工艺就可以做到,消除了多次外延技术中光刻所带来的精准问题,可以承担更高的基础电场,该技术也有难点,就是需要很强的刻蚀高深宽比沟槽的能力,为了避免这些情况的出现,进一步探究槽偏移对器件基础电压和导通电阻的影响。如图5所示,研究给出了槽偏移不同距离的情况。从图5可以看到只要沟槽的偏移距离改变,那么器件内部的电荷平衡也会发生改变,进而会影响到器件的电学特征。这里我们选取了0,0.5,1三个距离,可以看出来器件的导通电阻都是逐渐增强,而后衰减,最大值出现在槽偏移为0的位置,并且它的正负偏移的图像是镜像的,0 ~ 4为正偏移图像,4 ~ 8为负偏移图像。

图6为槽偏移不同距离与超结MOSFET器件击穿电压与导通电阻间的关系。从图6来看,两者的变化都是先增后减,并且超结MOSFET器件在槽偏移为0的位置时,击穿电压和导通电阻是最大的。因为槽偏移会导致超结部分的电荷不平衡,所以会出现这种变化趋势。槽偏移不论正负,只要是在同一水平位置,那么两者的总电荷数就是不同的。

2.3 P柱与N柱掺杂浓度

综合上述实验,在保持总电荷相同时,不通过改变柱宽来持续增加两柱掺杂浓度来降低其导通电阻,这就是超结电荷平衡的原理。所以实验设定保持柱宽不变,对浓度进行调控。其掺杂浓度与器件击穿电压和导通电阻的关系见图7,图7中浓度编号1,2,3,4分别代表的浓度为[2×1015cm-3],[3×1015cm-3],[4×1015cm-3],[5×1015cm-3]。由上图可知,当P/N柱宽不变时,随着掺杂浓度的增加,超结MOSFET器件的击穿电压和导通电阻都是缓慢降低的,因此在增加P/N的浓度时,超结MOSFET器件的导通电阻会变低。

这里研究选取超结MOSFET器件漏电压150 V时,P柱与N柱在不同掺杂浓度下沿水平切线位置x方向上的电场强度分布的关系,因为需要验证超结MOSFET被过早击穿的原理,当P柱与N柱浓度过高时,总电场强度中y方向电场比重就会减小,当离子还没有被完全消耗时,x方向电场就会达到临界击穿电场。它们的关系具体见图8,其中编号1,2,3,4分别代表的浓度为[2×1015cm-3],[3×1015cm-3],[4×1015cm-3],[5×1015cm-3]。图8表明,导通电阻和击穿电压会随着浓度的增加而减少。

用该方法虽然可以解决掺杂浓度和电压的关系,但是这样会产生新的问题,如图9所示,而产生这些问题的主要原因是因为超结MOSFET结构柱宽变化使得离子注入,外延的难度增大,那么离子注入和外延的次数会随着深宽比的增大而变多,且P/N柱间的杂质横向扩散,因此这是下一步优化的目标。

3 结论

在相同功率下,超结功率MOSFET器件比传统的器件拥有更多的导通,所以在半导体功率器件领域成为了重点的研究对象。本次研究使用仿真模型设计了超结MOSFET器件,推导出超结结构MOSFET器件中击穿电压和导通电阻之间的关系。同时,使用数据仿真技术,设计出了650 V高压型的超结结构MOSFET器件,并实际制作出超结结构MOSFET器件,并对其特性进行了研究。我们更多的关注放在了器件的参数特性以及实际参数上,之后会对器件进行动态特性的测试分析和更具可靠性项目的全面测试,这样才能发现更多的问题,为后续650 V高压型超结MOSFET器件做出更多的优化。

参考文献

[1] 张倩. 基于文献计量的我国功率半导体器件研究状况分析[J]. 电子测量技术, 2020, 43(4):5.

[2] 曾文彬, 宋梁, 张西应,等. 基于Coffin-Manson模型功率半导体器件可靠性评估[J]. 电力电子技术, 2022, 56(7):3.

[3] 郑莹, 迟辛格. 功率MOSFET工艺仿真验证研究[J]. 电子技术与软件工程, 2021(7):2-3.

[4] 张子南, 李思坤, 王向朝,等. 极紫外光刻快速掩模优化方法[J]. 光学学报, 2022, 42(13):1305002-1305003.

[5] 梁加刚, 许昌庆, 王标,等. 高能离子刻蚀前处理对AlTiSiN涂层切削性能的影响[J]. 表面技术, 2019, 48(4):7-8.

[6] FIORENZA P, GIANNAZZO F, CASCINO S, et al. Identification of two trapping mechanisms responsible of the threshold voltage variation in SiO2/4H-SiC MOSFETs[J]. Applied Physics Letters, 2020, 117(10):103502-103503.

[7] LI R, HUANG M, ZHANG X, et al. Superjunction MOSFET with a trench contact on partly relatively lightly doped P-pillar for excellent reverse recovery[J]. Semiconductor Science and Technology, 2021, 36(10):105002-105003.

[8] ZHENG D, GUO Y, ZHANG M, et al. Anisotropic charge carrier transport of optoelectronic functional selenium ontaining organic semiconductor materials[J]. Journal of Computational Chemistry, 2020, 41(10):6-7.

[9] 吴晓华, 韦文生, 曲金星,等. 二极管反向恢复时间多档测试技术[J]. 实验室研究与探索, 2021, 40(9):6-7.

[10] 唐茂森, 刘东, 沈俊,等. 低米勒电容超结MOSFET开关过程及反向恢复性能仿真研究[J]. 机车电传动, 2021(5):9-10.

[11] 刘松. 理解MOSFET时间相关及能量相关输出电容Coss(tr)和Coss(er)[J]. 电子产品世界, 2019, 26(4):5-6.

[12] NAFIS B M, MAHMUD M, WANGS Z, et al. System and component level risk assessment for SiC MOSFET based inverter for traction application at high coolant temperatures and off-road mission profile[J]. Journal of Electronic Packaging: Transactions of the ASME, 2022, 9(2):144-152.

Design and Performance of 650 V High-Voltage Superjunction MOSFET

ZHAO Yong

(Jiangsu Jing Charging New Energy Technology Co., Ltd,Nanjing 210000, China)

Abstract: Power MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) is a switch-type device controlled by an insulated gate. It has been widely used due to its high power capability and simple drive requirements. In this study, a 650V high-voltage superjunction MOSFET device was designed using deep trench etching and filling techniques. The device is mainly applied in power management for applications such as electric vehicle charging stations. The goal is to optimize the on-resistance while maintaining the same device parameters. The functionality of the power MOSFET device was verified through process simulation techniques. The relationship between the trench offset distance, doping concentration, on-resistance, and breakdown voltage was investigated. The results showed that the trench offset could cause charge imbalance in the superjunction region. Regardless of its polarity, as long as the trench offset occurs at the same horizontal position, the total charge in the super junction region would be different. With a constant pillar width, increasing the doping concentration resulted in a gradual decrease in both breakdown voltage and on-resistance. Furthermore, the on-resistance decreased as the doping concentration increased. This study provides valuable insights for optimizing and improving device design in the field of semiconductors.

Key words: superjunction MOSFET; process simulation; deep trench etching and filling technology; semiconductor

(責任编辑:王海燕)

收稿日期:2022-09-22

基金项目:国网江苏省电力有限公司科技项目(J2020111).

作者简介:赵勇(1995—),男,江苏南京市人,硕士,工程师,主要研究方向为功率半导体分立器件.

引用格式:赵勇.650 V高压型超结结构MOSFET器件设计与性能研究[J].安徽师范大学学报(自然科学版),2024,47(1):27-32.