高速数字设计中的反射分析

刘 伟, 康 凯,钟子发

(电子工程学院,安徽 合肥 230037

0 引言

随着电子技术的不断发展,高速器件被广泛的应用,由此带来的高速电路设计中的信号完整性问题变得比较突出,解决好高速设计中的信号完整性问题有助于系统正常稳定地运行。高速数字系统的快斜率瞬变和工作频率的提高,以及电路密集度的增大,导致高速数字电路系统设计领域的信号完整性问题以及电磁兼容性问题日趋严重,破坏了信号完整性,导致信号失真、定时错误,产生不正确的数据、地址和控制信号。因此,信号完整性问题已经成为高速数字电路设计中的关键环节。

高速数字系统一般包括两方面的涵义:其一是指系统的工作频率高;其二是指信号的边沿(上升沿/下降沿)变化速率快。一般认为当系统的工作频率达到或者超过50MHz时,就称为高速数字系统。然而更为重要的是,如果信号上升沿/下降沿的变化速率很快,那么即使系统的工作频率很低也要看作是高速数字系统。通常约定,如果信号在信号线中传播延迟大于1/6信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应[1]。

信号完整性(signal integrity,简称SI)是指信号在信号线上的质量,是信号在电路中能以正确的时序和电压做出响应的能力。信号完整性的问题主要包括传输线效应,如反射、时延、振铃、信号的过冲与下冲以及信号之间的串扰等,涉及传输线上的信号质量及信号定时的准确性。

1 问题产生的机理

信号在传输线上传输时,当高速PCB上传输线的特性阻抗与信号的源端阻抗或负载阻抗不匹配时,信号会反射,使信号波形出现过冲、下冲和由此导致的振铃现象。所谓特性阻抗的定义为:当导线上流经有高频信号时,所呈现的电压与电流的比值。那么对于确定的传输线而言,其特征阻抗为一个常数。

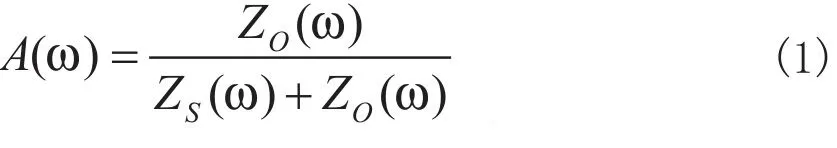

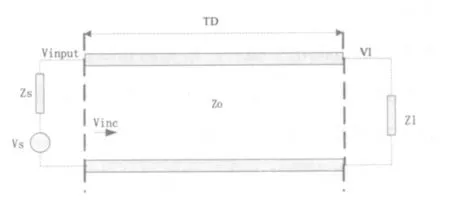

建立如图1所示的高速信号反射分析模型[2],VS为驱动器的源电压,ZS为等效源内阻,ZL为等效负载电阻,信号传输路径为特性阻抗为ZO的微带传输线。源的实际输出电压为Vinc,若负载阻抗ZL=ZO,则入射电压Vinc全部到达负载不会反射;否则,当入射电压到达负载时,一部分电压将被反射回来,并在传输路径上和入射电压叠加。但入射电压和反射电压互不干扰的独自传输,当反射电压到达源端时,若源内阻ZS和传输线的特性阻抗不匹配,将会产生第二次反射,这样,信号就会在源端和负载之间来回形成多次反射即反弹,直到达到稳态。具体数学推导如下:当一个信号施加在传输线一端时,全部源端电压的一部分沿线路向下传播。该部分是频率的一个函数,即输入接收函数,记为A(ω) ,其值由源端阻抗ZS和传输线阻抗以及输入接收式决定:

图1 高速信号反射分析模型

在电缆的远端,出现的是一个信号衰减后的部分振幅,它也是一个频率的函数,记为T(ω),其值由负载阻抗ZL和传输线阻抗以及输出传输式决定:

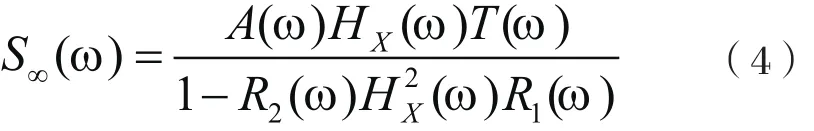

当传播信号的T(ω)部分出现在电缆远端时,一个反射信号R2(ω)也将沿着电缆向源端反向传播;当反射信号传播回源端时,再一次被HX(ω)衰减,并被源端阻抗第二次反射,源端的反射系数为R1(ω),如此将进入一个无止境的循环,这个信号的无限求和为:

2 问题的解决

当源内阻小于传输线特性阻抗时会出现振铃,称为过载传输线;当源内阻大于传输线特性阻抗时会将信号上升沿拉长,称为欠载传输线;当两者相等时,多次反射才不会发生[3]。

为改善因线路的阻抗不匹配而造成反射的现象,可以选择采用“布线拓扑”和“终端技巧”的办法[4]。利用适当的布线拓扑法来改善反射现象,通常不需要增添额外的电子组件。常见的布线拓扑法有4种,分别是点到点法、菊花链法、星形法和远端分支法。除了布线拓扑法,为克服反射现象的干扰,“终端技巧”是最有效的方法。传输线的特性阻抗一般是定值,终端技巧的目的旨在提供一个完全阻抗匹配的传输线环境以及保持电位的稳定。通常,根据传输线的特性阻抗在其驱动端串联电阻使源阻抗与传输线阻抗匹配,或者在接收端并联电阻使负载阻抗与传输线阻抗匹配,从而使源反射系数或者负载反射系数为零。常用的端接方式有:串联端接、简单的并联端接、戴维宁端接、RC网络端接和二极管端接等[5]。端接的位置对信号的反射有很大影响,一般串行端接的电阻应尽量靠近源端,总线结构的端接电阻应放置在总线结构的两个最远端等[6]。总之,信号的端接必须通过仿真来选择最佳方法,本文主要分析点到点拓扑结构的端接方式。

2.1 末端端接

这种方法主要包括并联端接、戴维宁端接、RC网络端接,理论是设定R2(ω)为零。式(4)化简后的结果是:

实际上,这消除了第一次反射,信号的能量进入电缆,传播到远端后流出,没有反射。使R2(ω)=0的方法很简单,只要使负载阻抗ZL等于电缆特性阻抗ZO。

2.2 源端端接

这种方法主要指串联端接,理论是设定R1(ω)为零。式(4)化简后的结果是:

实际上,这消除了第二次反射,而不是第一次。信号的能量进入电缆并传播到远端,而后退出电缆。反射能量返回到源端,但在该点不再反射(R1=0),不再有能量第二次反射回负载端。使R1(ω)=0的方法很容易,只要使源端阻抗ZS等于电缆的特性阻抗ZO。

通过反复不断的实验,可以得到信号质量满足要求的最大的末端布线长度,按照公式RS=ZO-ZS计算串联电阻的最优值。比较上述仿真波形,端接后的波形质量大大改善,因此端接是解决反射问题的好方法,其他匹配方案操作方法类似[8]。

通过以上两个实验,可以看出振荡并不明显,但上冲、下冲和传输延迟相当明显。当不进行端接时,响应曲线的上冲和下冲幅度明显增大,会超出器件所能容忍的范围,振荡现象也会变得明显,很容易造成误触发,但传输延迟减小了;当采取端接方案时,虽然振荡现象和上冲、下冲大大的削减了,但是却带来了很大的传输延迟,而且在选择端接电阻时会发现:随着端接电阻值的增大,上冲、下冲和振荡现象减弱,但传输延迟增大;反之,则上冲、下冲和振荡现象增强,但传输延迟减小。在这种情况下,应综合考虑系统对传输延迟、上冲、下冲和振荡幅值的要求。

4 结束语

本文分析了高速电路设计中的反射的形成及其影响,结合实例简单地仿真分析了解决反射的一些方案。实践证明,对信号反射问题的分析在高速电路设计中的作用举足轻重,只有解决好这个问题,高速系统才能准确、稳定的工作。本文对信号完整性问题中的典型传输线反射问题的研究对保证信号完整性是有效的,有助于提高电子系统性能,对于优化PCB的EMC设计具有很好的指导意义和一定的工程价值。当然,仅仅解决反射问题是远远不够的,实际工程中的高速数字设计还需要抑制接地反弹、解决串扰、差分线、电磁兼容等问题,以此来调整走线、布局,从而提高系统的性能指标。

[1]孙德玮.高速系统中的串扰分析[J]. 解放军电子工程学院学报, 2008.

[2]田广锟. 高速电路PCB设计与EMC技术分析[M].北京:电子工业出版社, 2008.

[3]张海风. Hyper Lynx仿真与PCB 设计[M]. 北京:机械工业出版社, 2006.

[4]Howard Johnson.沈力译.高速数字设计[M].北京:电子工业出版社,2009.

[5]江思敏.PCB和电磁兼容设计 [M].北京:机械工业出版社,2006.

[6]Eric Bogatin.李玉山译.信号完整性分析[M].北京:电子工业出版社,2005.

[7]肖汉波.高速PCB设计中信号完整性的仿真与分析[J].电讯技术,2006年(5).

[8]冯志宇.基于信号完整性分析的高速PCB设计[D].成都:电子科技大学,2004.