基于EPM7160S的IRIG-B(AC)码调制设计

李 亮,李杰然,张 烨

(92785部队 河北 秦皇岛 066000)

IRIG-B码是美国靶场仪器组设定的B型时间格式码。B码的主要特点是时帧速率为每秒一帧,携带信息量大,B码分为直流(DC)码和交流(AC)码[1-2]。直流码每个码元为脉冲信号,可以实现高精度授时(微秒级),但直流码只能采用电缆传输较近的用户。所以对于远距离用户必须采用经窄带信道传输的及AC码授时。

1 IRIG-B码结构特征分析

我国军标规定时间信息传递采用B码方式,主要参考美国靶场时间仪器组IRIG (Inter Range Instrumentation Grop)“IRIG标准仪器时间格式-B”而制定的。B码是一串连续发送的脉冲码,一帧B码共10组100位数据,每组数据周期为100 ms,每个码元占10 ms的宽度,脉冲周期不同表示不同信息,每个码元可以是 P脉冲、数字“1”、数字“0”,如图1所示。

图1 P 脉冲、数字“1”、数字“0”

位置标志P0-P9,第1组传送的是秒(seconds)信息,第2组传送的是分(minutes)信息,第 3组传送的是时(hours)信息,第4、5组传送的是天(days)信息,第6组传送的是修正量信息,第7、8、9、10组传送的是可发射信号数据信息。IRIG-B码格式如图2[3]所示。

图2 IRIG-B码格式

时、分、秒均用BCD码表示,低位在前,高位在后;个位在前,十位在后。IRIG-B码格式如下组传送的是天(days)信息,第6组传送的是修正量信息,第7、8、9、10组传送的是可发射信号数据信息。时、分、秒均用BCD码表示,低位在前,高位在后;个位在前,十位在后。

2 EPM7160S简介

EPM7160S属于高性能、高密度的CPLD,其制造工艺采用先进的CMOS EEPROM技术。该系列芯片采用第二代多阵列矩阵 (MAX)结构,通过了标准的JTAG接口 (IEEE Std.1149.1-1990),支持在系统可编程ISP (In System Programmable),集成密度为600~5 000个可用门,引脚到引脚之间的延时为6 ns,工作频率最高可达151.5 MHz,高性能的可编程连线阵列(PIA)提供一个高速的、延时可预测的互连网络资源,每个宏单元中可编程扩展乘积项(Product-Terms)可达32个,具有可编程保密位,可全面保护你的设计思想。

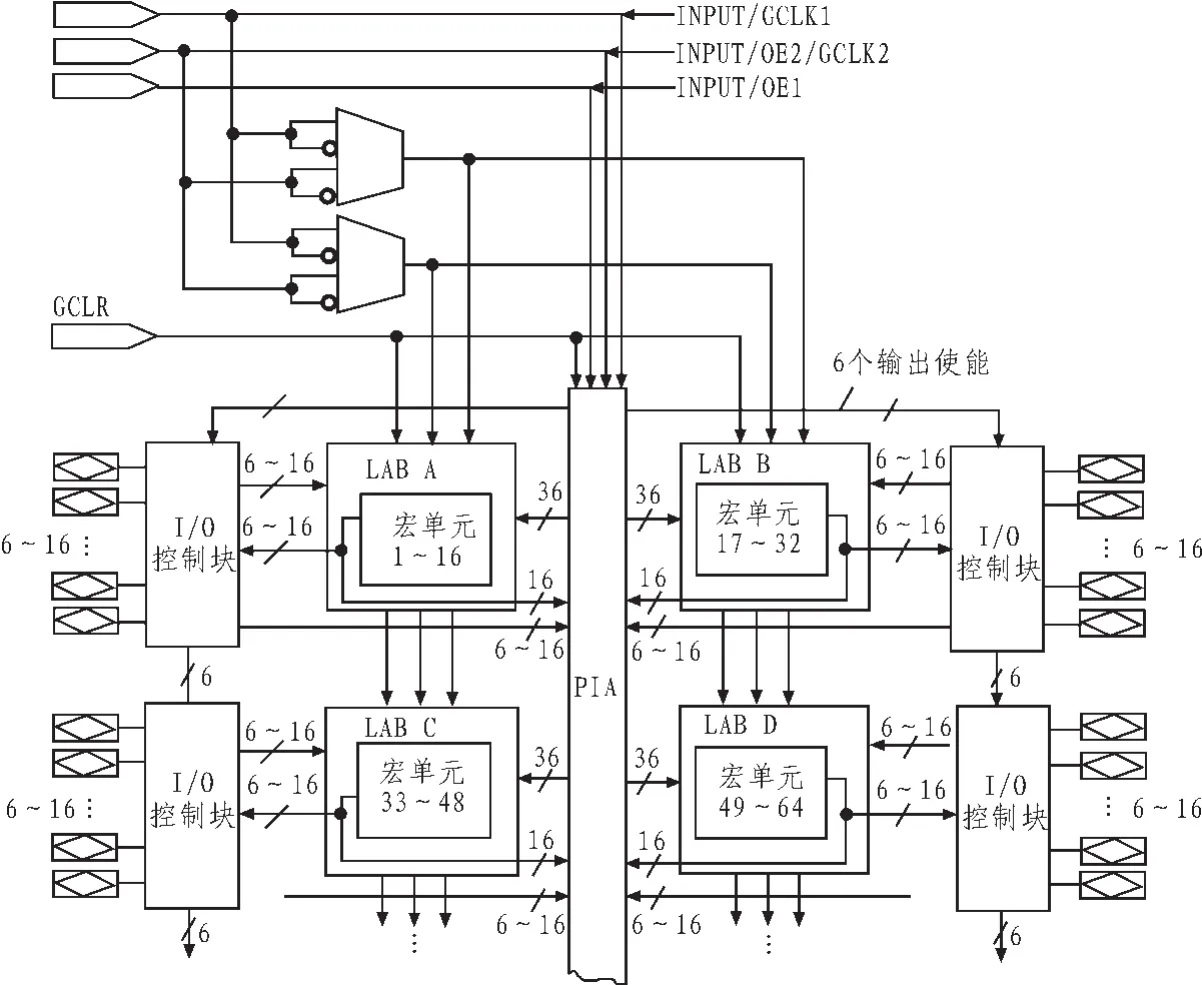

EPM7160S的内部结构如图3[4]所示。MAX 7160S在结构上包括逻辑阵列块LAB(Logic Array Blocks)、宏单元(Macrocells)、扩展乘积项(共享和并联) (Expender Product Terms)、可编程连线阵列PIA(Programmable Interconnect Array)和I/O控制块(I/O Control Blocks)。

图3 EPM7160S内部结构

每个LAB的输入信号包括:来自PIA的36个信号、全局控制信号 (用于宏单元内的寄存器实现辅助功能)和从I/O引脚到寄存器的直接输入信号。每个宏单元的寄存器可以单独地编程为具有可编程时钟控制的D、JK或SR触发器工作方式。如果需要的话,也可将寄存器旁路,以实现纯组合逻辑的输出。可编程连线阵列(PIA)是将各LAB相互连接,构成所需的逻辑布线通道。它能够把器件中任何信号源连到其目的地。所有MAX 7000的专用输入、I/O引脚和宏单元输出均馈送到PIA,PIA可把这些信号送到整个器件内的各个地方。

I/O控制块允许每个I/O引脚单独地配置为输入、输出和双向工作方式。I/O控制块有两个全局输出使能信号,它们由两个专用的、低电平有效的输出使能引脚OE1和OE2来驱动。图4所示为EPM7160S的信号时序。

3 硬件电路设计

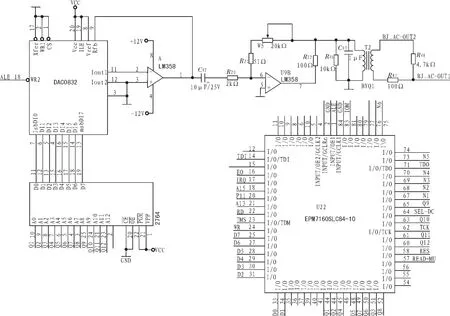

IRIG-B(AC)码调制产生的电路原理图如图5所示。主要由EPM7160S芯片和D/A转换电路组成。EPM7160S芯片由外部晶振提供10 MHz的频率信号,通芯片内部的分频电路产生1 kHz和100 kHz的正弦信号。产生的1 kHz的正弦信号由EPM7160S产生的DC码进行幅度调制,为了能够得到精确的时间信号,正弦信号的正交过零点必须与DC码的上升沿一致。

图4 EPM7160S的时序信号

产生的100 kHz的正弦信号提供给DAC0832数模转换芯片做同步控制信号与采样信号频率相同。数模转换器的输出电流建立时间需1 μs,转换AC码数据量的周期小于10 μs,可满足实际的需要[5]。

4 结论

图5 电路原理图

时统系统是现代化靶场试验的关键设备之一,随着科学技术的发展,对时统系统的功能、体积、精度、可靠性等技术指标提出越来越高的要求[6]。采用EPM7160S解调IRIG-B码(AC码),数据处理灵活方便,而且外围硬件电路简单,可以提高IRIG-B码解调的可靠性及B码解调的适应能力,保证解调精度[7]。

[1]马红皎,胡永辉.GPS&IRIG-B码时间系统分析[J].电子科技,2005(7):21-25.

[2]董宝润.时间统一系统[M].北京:国防工业出版社,2003.

[3]Timing committee telecommunications and timing group range commanders council[C].IRIG Serial Time Code Formats,1998.

[4]Altera.MAX 7000 orogrammable logic device family data sheet[DB/OL].2005.http://www.altera.com.cn/literature/ds/m7000.pdf

[5]谢筑森,张 辉,陈奥初,等.单片机开发与典型应用设计[M].合肥:中国科学技术大学出版社,1997.

[6]李清军.一种解调时统信号新方法的探讨[J].光学精密工程,1997,5(4):89-94.

[7]张 骞.基于AD8346的通用通信信号发生器[J].电子设计工程,2009,17(1):9-11.