基于0.35 μm工艺的Delta-Sigma ADC实现

曾 博,杨志坤

(电子科技大学 电子工程学院,四川 成都 611731)

过采样Delta-Sigma调制技术采用过采样技术与调制器的噪声整形技术对量化噪声进行双重抑制,信噪比的提高,可使A/D转换器达到很高的精度[1]。同时,采用过采样调制技术,可大大缓解对前置抗混叠滤波器的性能要求,使A/D转换器中数字电路的比例增加,模拟电路的比例减少,对模拟电路精度的要求降低,适于VLSI技术的发展,并且能以较低的成本实现高精度A/D转换。

1 过采样A/D转换技术

1.1 过采样技术

过采样指以远高于奈奎斯特(Nyquist)采样频率的频率对模拟信号进行采样[2]。若输入信号的最小幅度大于量化器的量化阶梯,并且输入信号的幅度随机分布,则量化噪声的总功率是一个常数,与采样频率fs无关,在0~fs的频带范围内均匀分布。因此量化噪声电平与采样频率成反比,提高采样频率,可以降低量化噪声电平,而基带是固定不变的,因而减少了基带范围内的噪声功率,提高了信噪比。

1.2 Delta-Sigma调制技术

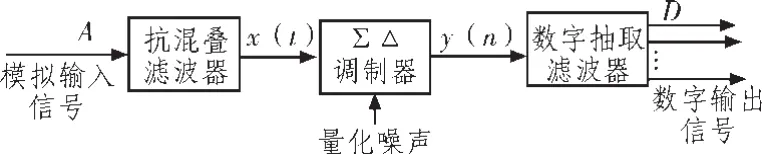

Delta-Sigma调制器及噪声整形技术过采样A/D转换器的框图如图1所示。调制器的输入为经过前端抗混叠滤波器的模拟信号,输出为经过过采样调制的脉冲编码调制(PCM)数字码流。数字抽取滤波器的作用是滤除带外噪声,降低抽样频率。

图1 过采样A/D变换器框图

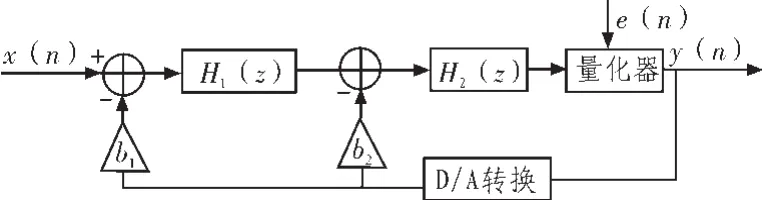

调制器的特点在于它的噪声整形特性。图2(a)为一阶调制器框图。其中b为反馈系数。为避免多比特带来的非线性变换问题,一般多采用1 bit量化,其量化器是一个过零比较器,对器件特性要求不高。在输入端调制器对过采样时域离散信号和反馈信号之差进行积分,其输出信号再经过量化器形成1 bit PCM数字信号。图2(b)为积分器框图,其中a表示积分器增益,d表示延时单元。积分器起到低通滤波器的作用,其Z域传输函数为:

图2 一阶调制器及积分器框图

假定量化噪声为累加噪声,则图2(a)所示一阶调制器的传输函数为:

由式(2)可知,调制器对输入信号X(Z)是无失真传输,而对量化噪声E(Z)则是以一阶差分的形式进行传输,从频域来看则是高通滤波,或者说调制器将量化噪声从基带内搬移到基带外的更高频段,通常将这一技术称为噪声整形技术。

1.2.1 Delta-Sigma调制器的信噪比

对L阶调制器,当输入为正弦信号时,其输出信号的最大信噪比SNR为:

式中,OR为过采样率,定义为过采样频率与Nyquist采样频率的比值。设过采样率为OR=2r,那么式(3)可以改写为:

由此可知,过采样率OR对信噪比SNR的影响。在工艺允许的范围内,每提高1倍采样频率,调制器输出带内信噪比就会大约提高3.01(2L+1)dB。在过采样率一定的情况下,调制器阶数越高,其信噪比越高。

1.3 二阶与高阶调制器

二阶调制器由于阶数增加,其噪声整形的效果在相同采样频率的条件下,要比一阶调制器好,即其输出基带内信噪比较大。图3为二阶调制器框图[3]。

图3 二阶调制器框图

图中 H1(z)和 H2(z)为积分器,b1和 b2为反馈系数。 研究表明,b2/a1>1.25 时,满足稳定条件,当 a1=a2=1,b1=1,b2=2 时,该二阶调制器的Z域传输函数可表示为:

由式(5)可看出,其对输入信号仍为全通函数,而对量化噪声为高通,且效果更明显。

由于高阶调制器存在稳定性问题,因此往往采用一些特殊的调制器电路结构,如级联结构。

一阶与二阶调制器结构是非常成熟的且保持绝对的稳定性,所以高阶的调制器可以用一阶或二阶调制器级联的方法构成。这样每一级都能保持稳定,同时也实现了高阶的噪声整形。

2 Delta-Sigma调制器的行为级仿真与分析

根据以上理论基础,将工作分成两部分进行,首先兼顾时间、速度、精度各方面采用最流行的仿真工具—MATLAB中的SIMULINK[4]来对二阶调制器进行功能仿真;然后采用AMS 0.35 μm的工艺,利用Cadence进行电路设计与仿真。

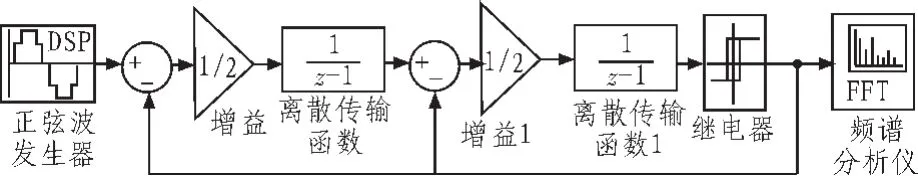

图4 二阶调制器结构

按如图3设计二阶调至器的框图结构,如图4所示。在仿真过程中采用以下的设置,采用0.5的反馈系数,因为考虑到实际的积分器电路会有一个饱和界限。以下是具体的仿真条件:Amplitude[Vsin]=0.5,Frequency[Vsin]=5 K;OSR=64;A=1/2 Quantizer:On,Vout=1;Off,Vout=-1;

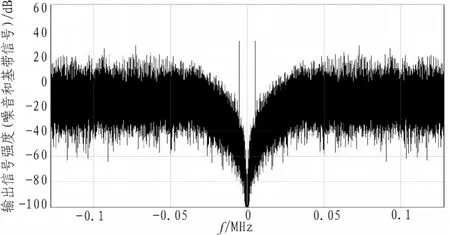

输出信号的行为级仿真实验结果如图5所示,显示二阶理想调制器在信号带宽内能达到100 dB的信噪比,调制器的输出带内SNR,基本上随输入电平的增加而增加,精度较低的话,显然需要更高阶的噪声整形。调制器的输出在其他条件不变的情况下,只与相对输入电平有关而与输入信号的幅度无关。

图5 输出信号的FFT分析

3 电路设计和仿真

在Iinux redhat版本环境下,使用Cadence设计晶体管级电路,采用安装hotkit版本的AMS 0.35 μm PDK,电路主体结构采用以上的行为仿真模型。

二阶调制器的核心电路采用单端输出的Folded-Cascode放大器[5],结构如图6所示。积分器以及比较器均根据该结构设计,由于电路还在进一步研究中,目前的放大器增益相位图结果为图7所示。关于该运放的功耗优化以及尺寸的优化将在今后的工作中讨论。

图6 调制器中采用Folded-Cascode结构的运算放大器

该电路的所有开关采用互补的MOS管对传输门结构,其转折点电压被调整到0 V左右,以适应整个电路的工作电压基准,电路采用非重叠的时钟,以避免高低电平处的混乱情况发生,采样保持电路由传输门与单位积分器构成[6]。

图7 Op-amp的Gain-phase margin特性曲线

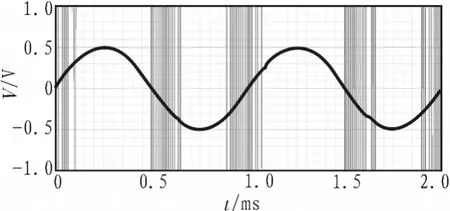

电路中的比较器由放大器与非门组成,结构简单,能在接近1 MHz的频率范围内工作,其输出波形满足门限判决要求,以下是采用以上结构的一阶和二阶调制器的输出波形,如图8、图9所示。

图8 一阶Delta-Sigma调制器的输出波形

图9 二阶调制器的输出波形

仿真条件:Vsin=0.5sin (2pi*1 k),Vsampling=100 k,output=[-1,1],放大器偏置于1.5 V,该工艺调制器采用 3.3 V电压供电从输出波形观察,显然一阶调制器的输出按取平均值得算法与预期值误差比较大,二阶放大器在给定初值时要考虑电路饱和问题,采用合理的反馈系数与加权系数,上述讨论的电路结构能较好地工作于1 MHz以下的频率,证明采用该工艺的该结构的调制器能稳定工作。 仿真结果还表明,该电路的信噪比受运放参数中的差模增益和增益带宽积的影响较大,而受其他参数的影响较小。

4 结论

分析过采样Delta-Sigma变换器中调制器的几种基本结构及性能特点,并给出了行为仿真结果。结果表明,增加过采样率和调制器整形阶数均可提高信噪比。过采样率的提高受到器件速度的限制。设计了由开关电容构成的一阶、二阶调制器电路,进行了仿真,并分析了其性能与电路参数的关系。在今后的工作中将进一步优化和改善现有电路。

[1]邓彦松,杨 勇,单玉华.过采样调制器原理及实现[J].中国集成电路,2004,6(43):247-249.

[2]Candy J,Temes G:Oversampling methods for A/D and D/A conversion,in oversampling Delta-Sigma data converters[M].New York:IEEE Press,1992:1-29.

[3]Malcovati P, Brigati S,Francesconi F,et al.Behavioral modeling of switched-capacitor sigma-delta modulators[J].IEEE Trans.Circuits Syst.,2003(50):352-364.

[4]Math Works Inc.SIMULINK and MATLAB users guides[Z].Natick,MA,1997.

[5]BrandtB,WingardD,WolleyB.Second-ordersigma-deltamod-ulator for digital-audio signal acquisition[J].IEEE:Solid-State Circuits,1991(SC-26):618-627.

[6]Razavi B.Design of analog CMOS integrated circuits[M].New York:McGraw-Hill,2001.