基于SystemC语言的伪随机序列发生器设计*

裴 佩 卢立丹

(中国船舶重工集团公司第722研究所 武汉 430079)

1 引言

随着集成电路设计的发展,SoC时代已经到来。为了满足SoC设计的要求,一种能够同时实现较高层次的软件和硬件描述的系统级设计语言,可以大大提高设计效率。SystemC正是这样一种适于系统级设计的硬件描述语言。它支持门级、RTL级、系统级等各个抽象层次上的硬件的建模和仿真,而且支持软硬件协同设计,能够描述由硬件和软件组成的复杂系统结构,支持在C++环境下对硬件、软件和接口的描述[1]。

自1999年提出后,SystemC在 Synopsys、ARM 、Mentor Graphics、Coware 、Cadence 、Intel等微电子业内主流公司的支持下得到了很大的发展,由于其开放性等特点,已经得到全世界工程师的欢迎和认可,并已经于2005年成为IEEE标准。

2 SystemC语言的特征

SystemC是完全免费并且开放的,它的源代码可以使用任何标准C++编译环境进行编译,生成可执行文件。SystemC本质上时在C++的基础上添加的硬件扩展库和仿真核,通过使用SystemC类库,设计者可以根据不同的需求编写目标系统的系统级(system level)、行为级(behavioral level)或RT L级的SystemC模型代码。

SystemC具有所有硬件描述语言所共有的基本特征,包括模块、端口、进程和信号等。SystemC中的模块用关键字SC MODULE来定义,其端口定义与Verilog类似。在SystemC中,进程是一个基本的执行单元,它被调用来仿真目标系统的行为。进程的行为是多样化的,可以实现某个函数的功能,也可以在运行过程中被挂起,并且进程是并行执行的,一个进程中不能包含或直接调用其他进程。SystemC的进程主要有两种,事件进程(SC_MET HOD)和线程进程(SC T HREAD)。事件进程是惟一可以综合的RTL进程,它的特点是当敏感表上有事件发生时,它就被调用,调用后立即返回。只有该类进程返回后,仿真系统的时间才有可能前进,因此该类进程不能被挂起(类似于Verilog中的always)。线程进程不是RTL级进程,它可以被挂起和重新激活,所以它的一个重要用途是用来描述验证平台(testbench)。

图1 SystemC描述加法器的简单实例

SystemC描述加法器的一个简单例子如图1所示,该例是一个简单的加法器的描述。在 my_adder.h中定义了一个名为my_adder的模块,输入端口为int类型的a、b和时钟类型的clk,输出信号为int类型的c。此外,模块里面定义了一个类型为SC_METHOD的进程,其对时钟的上升沿敏感。每当时钟上升沿到来时,该进程被激活,完成将两输入端口上的数据相加再从输出端口送出的功能。进程entry的实现在adder.cpp中。

3 基于SystemC语言的伪随机序列发生器设计

SystemC语言必须可以综合才能投入实用,目前许多支持SystemC综合的软件已经投入商用。Agility Compiler软件就是比较好的一种,它是由Agility公司和Celoxica ESL business所共同开发的。Agility Compiler可以将SystemC语言综合成适合指定目标芯片的Verilog、VHDL、EDIF等文件,进而进行下一步的设计,实现了与传统硬件描述语言的无缝衔接[2]。

本设计就是利用SystemC语言设计pn序列发生器,具体实现一个m序列发生器的功能,然后在Agility Compiler中进行综合生成Verilog语言,再利用ModelSim等软件仿真。

3.1 pn序列简介

一个伪随机(或PN)序列是一个1和0的码序列,由于它具有类似白噪声的随机特性但是又能重复产生,所以称为伪随机序列,并且可以代替白噪声用于需要随机信号的场合,例如测试系统性能。更重要的是,它具有良好的相关特性,可以用于码分复用、多址接入、测距、密码、扩频通信和分离多径信号等许多领域[3]。

通常情况下,扩频序列具有如下性质:

1)具有尖锐的自相关性;

2)有尽可能小的互相关性,互相关性最好为零;

3)有尽可能大的序列复杂度,即足够长的码周期保证保密和抗干扰要求;

4)有足够多的独立地址数,以实现码分多址的要求;

5)工程上易于产生、加工复制和控制。

3.2 pn序列发生器设计

伪随机序列不止一种,其中以m序列最为重要,因此设计中,将对m序列发生器进行设计。一个m序列的长度为L=2m-1比特,周期为L,并由一个m级的带有线性反馈的移位寄存器产生,每个周期内有2m-1个 1和 2m-1-1个0[4]。

设计中,将设计通信中常用的12级,周期为4095的m序列发生器。

一般要产生一个m序列主要有以下几个步骤[5]:

1)根据m序列产生原理得到m序列的生成多项式;

2)根据生成多项式的级数确定要实现的m序列产生器所需要的移位寄存器的长度;

3)实现移位寄存器链;

4)按照生成多项式对移位寄存器链抽头;

5)将抽头信号进行“异或”,结果反馈到移位寄存器的输入端。

本次设计中采用的生成多项式为:f(x)=x12+x6+x4+x+1。

3.2.1 m序列的systemc主要程序设计

/************************

模块功能:该模块是周期为4095(12级)的m序列发生器,采用线性反馈移位寄存器实现。

…

************************/

#define bit_size 12

#include"systemc.h"

SC_MODULE(m_gen){

sc_in<bool> clk,rst;

…

void prc_m_gen();

SC_CTOR(m_gen){

SC_M ETHOD(prc_m_gen);

sensitive_pos<<clk;

}

};

void m_gen::prc_m_gen(){

…

if(!rst.read()){

shift_reg=4095;//设定寄存器的初始状态,不能为0

m_out=0;

}

else if((ena==1)&&(rst==1)){

shift_temp=shift_reg;

shift_reg.range(bit_size-1,1)=shift_temp.range(10,0);

shift_reg[0]=shift_temp[0]ˆshift_temp[3]ˆshift_temp[5]ˆshift_temp[11];

}

m_out=shift_reg[bit_size-1];//最高位输出}

3.2.2 m序列程序综合

在Agility Compiler软件“工程设置”中,设置综合的目标芯片为 Altera Stratix II系列的ep2s130f1020c4。

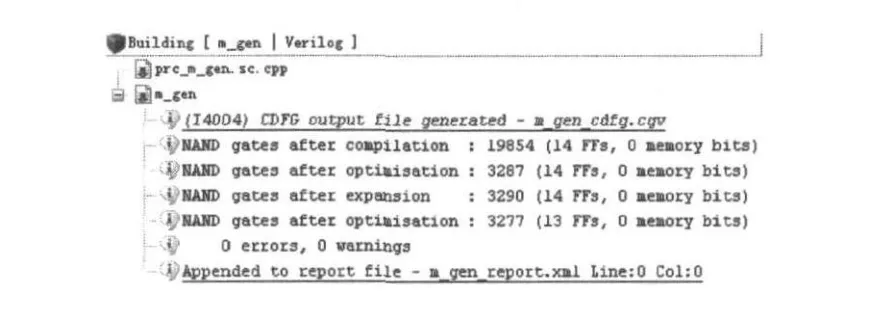

Agility Compiler综合出的信息见图2所示。由图可见,优化综合后共用到14个触发器,3277个与非门,0bit寄存器。

图2 m序列发生器综合信息图

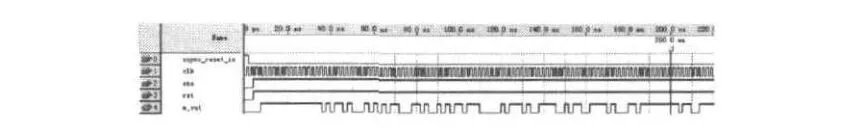

为了验证结果的准确性,利用ModelSim软件和Quartus II软件对综合出的Verilog HDL程序进行仿真,得到仿真结果如图3所示。

图3 m序列发生器的ModelSim仿真结果

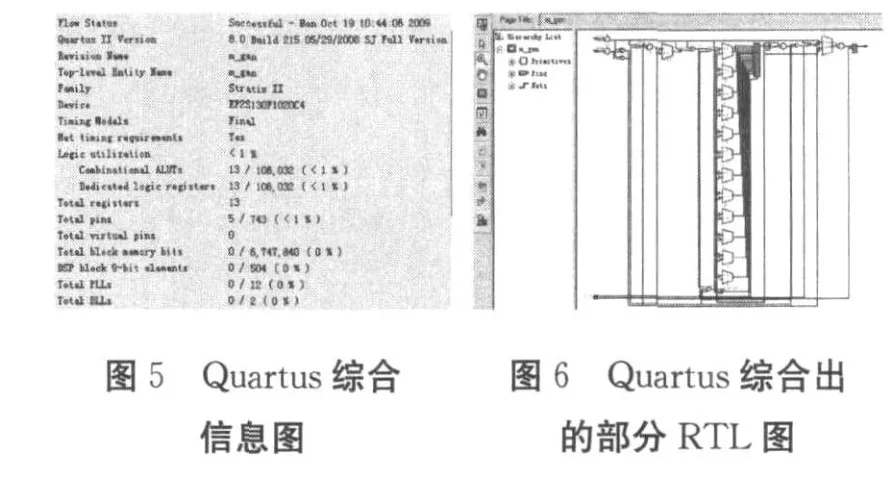

利用Quartus仿真综合出的Verilog代码后的部分仿真结果如图4所示,综合出的资源等信息如图5所示,RTL部分图如图6所示。

图4 m序列发生器的Quartus仿真结果

3.2.3 m序列仿真结果分析

为了分析结果的正确性,将考察从三个时间处的连续32比特m_out信号序列。结果见表1。经统计,一个周期内有2048个1,2047个0。

表1 m序列输出统计

由此可见,生成的周期为4095的该m序列符合设计要求。

4 结语

从这个实例可以看出,利用SystemC完成设计相比于传统的硬件描述语言具有很多优点:

1)SystemC语言更加灵活,因为其本质上是C++语言,所以设计更加灵活。

2)SystemC语言的设计效率更高。

3)SystemC语言对于具有C语言基础却熟悉Verilog语言的技术人员更有优势。

4)SystemC语言能够实现实现较高层次如系统级的软件和硬件描述,较好地实现软硬件的协同设计,而且它使得系统级设计和RTL级设计均可以在同一平台下完成。

SystemC已经成为IEEE标准,这将促进SystemC更快的发展。相信不久的将来,其一定会成为业内主流的设计工具。

[1][美]巴斯克.SystemC入门[M].夏宇闻,等译.北京:北京航空航天大学出版社,2008

[2]Agility公司.agility_manual

[3]西瑞克斯(北京)通信设备有限公司.无线通信的Matlab和FPGA实现[M].北京:人民邮电出版社,2009,6

[4]樊昌信.通信原理教程[M].北京:电子工业出版社,2005,7

[5][美]John G.Proakis,等.现代通信系统(MATLAB版)[M].第二版.北京:电子工业出版社,2008,1