高速嵌入式系统中电源噪声抑制方法

,2

(1.武警工程学院 电子技术系,西安 710086;2.西安电子科技大学 宽禁带教育部重点实验室,西安 710071)

1 引 言

嵌入式系统正朝着高速、高频、低电压等方向发展,使得电源分布网络(Power Distribution Network,PDN)中的噪声成为影响高速嵌入式电路性能的主要因素之一[1-2]。当电路中多个有源器件同时转换逻辑状态时,产生的切换噪声会引起PDN上的电压波动,这种波动称为同步切换噪声(Simultaneous Switched Noise,SSN)。目前,高速嵌入式系统中普遍采用电源平面对的方式进行供电,这种结构具有直流阻抗低、散热快、易于布线等优点。然而,随着电路速度的提高,SSN的有效频谱范围可达10 GHz左右。此时,电源平面对表现为电磁谐振腔,当相应的谐振模式被激励时,平面对就会成为高速电路的重要噪声源,同时也是一个边缘场辐射源。谐振腔内的驻波会对附近的电路及其互连造成严重的耦合,从而产生相应的信号完整性问题和电磁干扰问题[3-4]。

文献[5]使用平面微波电路中的谐振腔理论推导出规则电源平面对中阻抗的数学表达式,该表达式中的自阻抗和互阻抗均表示为双重级数的格式。文献[6,7]研究了双重级数求解阻抗的快速算法,Wang Z L在文献[8]中结合分解元法(Segmentation Method)和谐振腔理论快速分析复杂形状的电源平面对的阻抗。通常采用添加去耦电容的方法来抑制电源平面对的谐振,但由于去耦电容存在等效串联电感,使得去耦电容仅适用于频率低于500 MHz以下的场合[9]。文献[10]中提出可以使用高磁导率、低电导率的导体材料代替普通导体材料充当高速电路中的平面层以增加导体损耗,从而达到抑制谐振的目的。但采用低导电率的导体会导致直流阻抗较高、难以散热等实际问题,与使用电源平面对的初衷相悖。本文根据文献[5]中的阻抗表达式,分析了电源平面对的谐振特性与PCB板材、介质材料、介质层厚度以及导体平面的电导率之间的关系,提出可通过减小介质层厚度、使用高介电常数的介质材料以及增加介质损耗等3种方法来抑制电源平面对的谐振效应,并使用Ansoft公司的Siwave全波电磁场仿真软件对相应方法进行了仿真。接着从时域仿真了高速电路中的噪声传播与电源平面对谐振阻抗的相互关系,说明通过抑制电源平面对谐振可有效减低电路中的电源噪声,提高电路的电源完整性。

2 基于谐振腔理论的电源平面对阻抗计算方法

电路中的电源平面对如图1所示,电源平面与地平面被介质隔开,其中,a为平面的长,b为平面的宽,t为平面的厚度,平面的导电率为σ,d为介质的厚度,介质的介电常数为ε,磁导率为μ,损耗角为δ,介质四周可等效为PMC边界(理想磁壁)。当电磁波传播到边界不连续点时,就会产生反射,从而导致谐振现象的产生。

图1 规则电源/地平面对结构Fig.1 Structure of the regular power ground pair

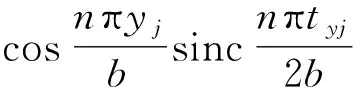

当a和b远大于d,d远小于数字信号最大频率分量的波长时,电源/地平面对之间仅存在Ez,Hx和Hy电磁场分量,根据麦克斯韦方程组可求解得到平面上任意位置(端口)处的自阻抗和传输阻抗的解析解,如下式所示:

f(xi,yi,xj,yj)

(1)

其中:

图2 解析计算与全波仿真自阻抗比较图Fig.2 Calculating self-impedance and simulating self-impedance

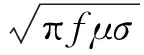

图2是采用式(1)计算的自阻抗(m=n=100)和使用Ansoft公司的Siwave全波仿真软件得到的自阻抗之间的对照图,其中电源平面对参数分别为:a=b=9 cm,d=0.4 mm,介质材料为FR4,相对介电常数为4.5,损耗正切为0.02,自阻抗的计算点坐标为(7.5 cm,7.5 cm)。从图2可以得出:当传播模式m、n足够大时,使用式(1)计算得到的自阻抗与使用全波仿真软件得到的自阻抗基本一致。当电源平面对谐振时,在图中体现为阻抗的极大值点。而谐振频率由平面的大小和介质的介电常数决定,具体可由式(2)进行计算:

(2)

式中,μ0和ε0分别是真空的导磁率和介电常数,而εr为电源平面对中电介质的相对介电常数。根据式(2)可计算出前几个谐振频率分别为:f(1,0)=f(0,1)=795 MHz,f(1,1)=1.12 GHz,f(2,0)=f(0,2)=1.59 GHz,f(2,1)=f(1,2)=1.78 GHz。

从以上分析可以看出,使用式(1)可以准确地计算出电源平面对的阻抗特性,至于如何快速计算式(1)可见文献[6,7],下文主要从式(1)出发分析电路板参数对谐振阻抗的影响,并寻找抑制谐振的有效方法。

3 影响谐振特性的PCB参数分析

由式(1)可知,影响电源平面对性能的参数主要有两平面之间介质的介质厚度、板材的介电常数和损耗角正切、平面尺寸、测量点位置以及平面所使用导体的电导率,通过改变以上参数均可改变系统的阻抗特性。在电源平面对的谐振频率上,系统输入阻抗达到最大值,该值由平面结构的损耗决定,增大损耗即可抑制谐振阻抗。通常我们可以使用的增大损耗方法有:使用高介电常数的电介质、增大电介质的损耗正切、使用低电导率的导体作为平面对、在平面的边缘增加损耗材料等。另外,当两平面之间介质的介质厚度d减小时,电磁波被迫穿过导体增加了导体损耗,从而也抑制了平面谐振。

图3为介质层厚度、相对介电常数、损耗正切以及所使用的导体材料等参数变化时,测量点(7.5 cm,7.5 cm)处的自阻抗变化情况。从图中可以得出:当介质层厚度d从16 mil变化至1 mil时,电源平面对的自阻抗不断减小,谐振频率位置不变,而谐振阻抗被有效抑制;当相对介电常数从4.4变化至30时,电源平面对的自阻抗也在减小,谐振处的阻抗也有所下降,同时谐振频率有向低频段移动的趋势,而低频端的谐振可使用去耦电容有效抑制;当介质损耗正切从0.002变化至0.02时,电源平面对的自阻抗有所减小,谐振频率位置不变,同时谐振阻抗也有所减小,但减小幅度不大;当导体板从铜改变为石墨时,谐振阻抗也可以被有效抑制。从图3可得出,降低谐振阻抗的有效方法是减小介质层厚度、使用高介电常数的介质材料、使用高损耗正切的介质材料。而使用低导电率的导体作为电源平面对虽然也可有效降低谐振阻抗,但存在直流阻抗较高、难以散热等问题,因此在实际的高速电路中不建议使用。

图3 电源平面对在不同参数下的自阻抗Fig.3 Self-impedance of power plane pair with different parameters

4 噪声传播与电源平面对谐振关系的时域分析

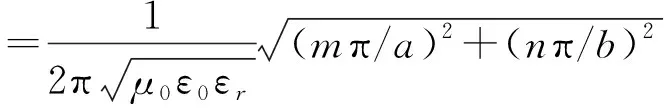

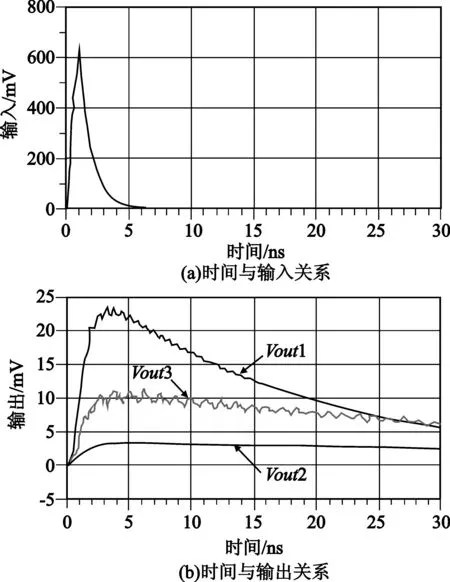

由于实际电路板上同步切换噪声的产生和干扰都是在时域内体现的,本节将对上文中所提到的3种方法在时域中抑制SSN的效果进行对比。在此我们主要对比3种结构,分别是:εr=4.4,d=16 mil,δ=0.02,copper;εr=4.4,d=1 mil,δ=0.02,copper;εr=16,d=16 mil,δ=0,copper;电源平面对的大小均为90 mm,使用的导电材料都是铜。首先我们通过Siwave软件分别对以上3种电源平面提取全波SPICE模型,然后将全波SPICE模型用于安捷伦公司的仿真软件ADS2008之中进行时域仿真。ADS2008中仿真原理图如图4所示,在电源平面中心位置A点(45 mm,45 mm)处注入干扰信号,从B点(75 mm,75 mm)位置处观测由干扰信号所产生的同步切换噪声传播情况。

图4 使用ADS进行时域仿真的原理图Fig.4 Schematic diagram of circuit simulation in ADS

在A点的输入信号是一个上升时间为1 ns、持续时间为5 ns、最大幅度为1 V的指数信号,经傅里叶变换后,该信号产生的同步切换噪声的频谱有效带宽为4 GHz。图5描述了上面所提到的3种电源结构中噪声的传播情况,3种结构在观测点B处所产生的噪声分别用Vout1、Vout2和Vout3表示。根据图5可知,Vout1、Vout2和Vout3的峰峰值分别为23 mV、3 mV和11 mV。由于结构2的介质层厚度仅有1 mil,可有效降低电源平面对的谐振阻抗,因此,在B点处的噪声相比其它两种结构分别下降了85%和73%。因此,这种电源平面对结构可应用于高速数字电路或高速数模混合电路以提高系统性能。

图5 3种结构时域仿真的噪声传播抑制情况图Fig.5 Time-domain response

5 结束语

随着嵌入式系统工作速率的提高,电源平面对的波动特性越来越明显。由于电源平面对可等效成一谐振腔体结构,当平面对的谐振模式被激励时,平面对就会成为高速电路的重要噪声源。通过抑制谐振阻抗可有效抑制电源噪声,提高系统的电源完整性。本文从电源平面对阻抗的解析表达式入手,分析了电源平面对的谐振特性与PCB板材、介质材料、介质层厚度以及导体平面的电导率之间的关系,得出可通过减小介质层厚度、使用高介电常数的介质材料以及增加介质损耗等3种方法来抑制电源平面对的谐振效应。使用时域仿真工具对3种不同参数电源平面对结构进行了噪声的耦合分析,发现采用薄介电材料是降低谐振阻抗的最有效方法。目前已有相应的电路板制作厂家支持电源平面对之间介质层厚度为1 mil的超薄设计,而笔者也在实际应用中使用过介质层厚度为2 mil的设计方案,实践证明该方案可有效抑制电源噪声在电源平面上的传播。随着技术的进步,最近学者又提出了一些降低谐振阻抗的新方法,如:嵌入式电容、电磁带隙结构等[11-12]。如何结合具体设计,抑制电源平面对谐振阻抗以实现电源完整性依然是高速嵌入式系统设计中最具挑战的领域之一,还需要我们不断地探索和努力。

参考文献:

[1] Swaminathan M, Kim J, Navak I, et al. Power distribution networks for system-on-package: status and challenges[J]. IEEE Transactions on Advanced Package, 2004, 27(2): 286-300.

[2] Madhavan Swaminathan, Daehyun Chung, Stefano Grivet-Talocia, et al. Designing and Modeling for Power Integrity[J]. IEEE Transactions on EMC, 2010, 52(2): 288-319.

[3] Swaminathan M,Ege Engin A. Power Integrity Modeling and Design for Semiconductors and Systems [M]. Englewood Cliffs, NJ: Prentice-Hall, 2007.

[4] Tzong-Lin Wu, Hao-Hsiang Chuang,Ting-Kuang Wang. Overview of power integrity solutions on package and PCB: decoupling and EBG isolation[J]. IEEE Transactions on EMC, 2010, 52(2): 346-356.

[5] Okoshi T. Planar circuits for microwaves and light waves[M]. Minich, Germany: Springer, 1985.

[6] Wang Z L, Wada O, Toyata Y, et al. Reducing Q factors of resonances in power/ground planes of multilayer PCBs by using resistive metal films[J]. Transactions on IEE, 2001, 121(10): 579-587.

[7] Wang Z L, Wada O, Toyota Y, et al. Convergence acceleration and accuracy improvement in power bus impedance calculation with a fast algorithm using cavity modes[J]. IEEE Transactions on EMC, 2005, 47(1): 2-9.

[8] Wang Z L, Wada O, Toyata Y, et al. Modeling of gapped power bus structures for isolation using cavity modes and segmentation[J]. IEEE Transactions on EMC, 2005, 47(2): 210-218.

[9] Knighten J, Archambeault B. PDN Design Strategies: I Ceramic SMT Decoupling Capacitors-What Values Should I Choose[J]. IEEE EMC Society News Letter, 2005, 203(1): 34-41.

[10] 苏东林,王晓晓. PCB材料与电源/地层谐振阻抗关系[J]. 北京航空航天大学学报,2007, 33(5): 568-571.

SU Dong-lin, WANG Xiao-xiao. Relationship between PCB material and power/ground impedance[J]. Journal of Beijing University of Aeronautics and Astronautics, 2007, 33(5): 568-571.(in Chinese)

[11] Muthana P, Srinivasan P, Engin A E, et al. Design, modeling, and characterization of embedded capacitor networks for core decoupling in the package[J]. IEEE Transactions on Advanced Package, 2007, 30(4): 809-822.

[12] CHEN Wei-hua,ZHANG Hou,WANG Jian,et al. A Novel Z-Bridge Electromagnetic Bandgap Power Plane for Suppression of Simultaneous Switching Noise[J]. Microwave and Optical Technology Letters, 2009, 51(2): 483-486.