基于VHDL的图像传感器TCD1206的驱动设计

崔朋朋,刘艳萍,杨玉芝

(河北工业大学 信息工程学院,天津 300401)

基于VHDL的图像传感器TCD1206的驱动设计

崔朋朋,刘艳萍,杨玉芝

(河北工业大学 信息工程学院,天津 300401)

介绍图像传感器TCD1206的主要特点、结构原理、引脚功能,并详细分析其驱动时序。通过研究采用VHDL实现TCD1206驱动脉冲的方法及逻辑设计原理,完成了驱动脉冲的VHDL程序设计和时序仿真。仿真结果证明了该驱动电路的可行性。

TCD1206;线阵CCD;驱动时序;VHDL

电荷耦合器件CCD(Charge Couple Device)是集光电转换、电荷储存、电荷转移为一体的新型光电传感器件。该器件的主要功能是将光学图像转换为电信号。当对其施加特定时序脉冲时,其存储电荷能在CCD内作定向移动,从而实现自扫描,输出电压信号的大小与CCD单元存储的电荷多少成正比,CCD单元存储电荷多少与光的强度和CCD单元光积分时间成正比。与传统的光电传感器相比,CCD图像传感器具有输出噪声小,动态范围大,光谱响应范围宽,分辨率高,输出信号线性度好,功耗低,体积小,寿命长等优点[1-2]。而CCD应用的关键就是获取驱动脉冲,这里分析线阵CCDTCD1206的工作原理和对驱动时序的要求,在此基础上设计合理的脉冲产生方案。该设计采用复杂可编程逻辑器件CPLD作为硬件设计平台,通过超高速硬件描述语言VHDL描述驱动方案,采用Altera公司的仿真软件QUARTUS II对其驱动脉冲进行仿真。

1 TCD1206的主要特点

TCD1206是一款高灵敏度、低暗电流、2 160像元的双沟道线阵CCD图像传感器。由2 236个PN结光电二极管构成光敏元阵列,其中前64个和后12个是用作暗电流检测而被遮蔽的,中间2 160个光电二极管是曝光像敏单元,每个光敏单元的尺寸为长 14 μm、高 14 μm,中心距亦为14 μm。光敏元阵列总长为30.24 mm。

TCD1206的主要特性有[3]:1)光敏像元数为2 160像元;2)像敏单元为:14 μm×1 414 μm(相邻像元中心距为 14 μm);3)光谱范围为250~1 100 nm;4)光敏区域采用高灵敏度 PN结作为光敏单元;5)时钟为二相(5 V);6)内部电路包含采样保持电路,输出预放大电路;7)采用22引脚DIP封装。

2 TCD1206的结构原理和引脚功能

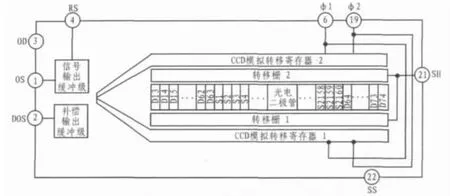

2.1 结构原理

TCD1206是二相电极的双沟道线型CCD,其结构原理如图1所示。中间一排是由多个光敏二极管构成的光敏阵列,有效单元为2 160位,其作用是接收照射到CCD硅片的光,并将其转化成电荷信号,光敏元两侧是存储其电荷的MOS电容列—存储栅。MOS电容列两侧是转移栅电极SH。转移栅的两侧为CCD模拟移位寄存器,其输出部分由信号输出单元和补偿单元构成[4]。

图1 TCD1206的结构原理图

2.2 引脚功能

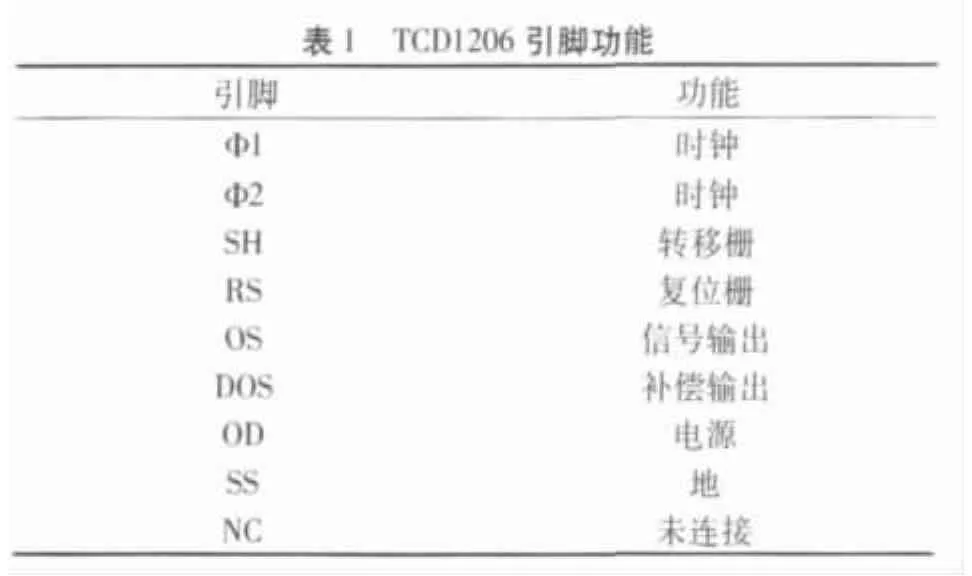

TCD1206器件采用DIP封装,各引脚功能如表1所示。

?

3 驱动时序及驱动设计

3.1 驱动时序分析

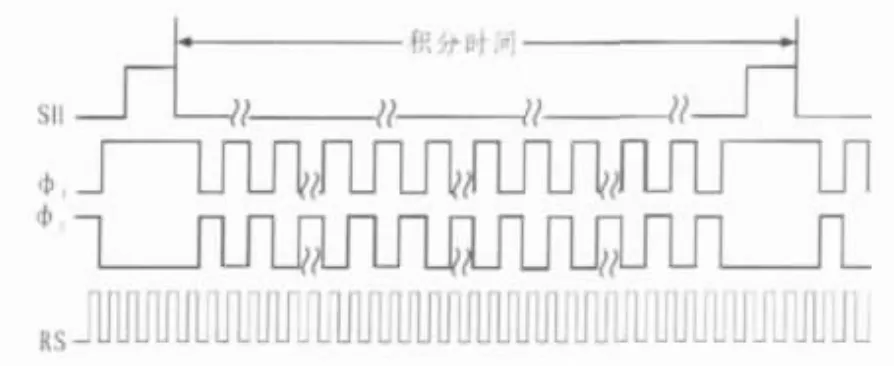

TCD1206在图2所示的驱动脉冲作用下工作[5-6]。当SH脉冲高电平到来时,φ1脉冲为高电平,其下形成深势阱,同时SH的高电平使φ1电极下的深势阱与MOS电容存储势阱沟通。MOS电容中的信号电荷包通过转移栅转移到模拟移位寄存器的φ1电极下的势阱中。当φSH由高变低时,φSH低电平形成的浅势阱将存储栅下的势阱与φ1电极下的势阱隔离开。存储栅势阱进入光积分状态,而模拟移位寄存器将在φ1与φ2脉冲的作用下驱使转移到φ1电极下的势阱中的信号电荷向左转移,并经输出电路由OS电极输出。DOS端输出补偿信号。

图2 TCD1206驱动脉冲波形图

由于结构上的安排,OS端首先输出13个虚设单元信号,再输出51个暗信号,然后才连续输出S1到S2160的有效像素单元信号。第S2160信号输出后,又输出9个暗信号,再输出2个奇偶检测信号,以后是空驱动。空驱动的数目可以是任意的。由于该器件是两列并行分奇偶传输的,所以在一个SH周期中至少要有1 118个φ1脉冲。RS为复位级的复位脉冲,复位一次输出一个信号。

3.2 驱动电路设计

驱动电路的作用是给CCD提供正常工作所需要的逻辑时序脉冲和偏置工作电压,并在CCD的输出端把光电转换得到的电荷量转变成电压量输出。驱动脉冲信号的波形、相位、前后沿时间等对器件工作有很大影响。

为了保证CCD工作稳定可靠,必须设计符合CCD正常工作要求的时序脉冲和驱动控制电路,驱动控制脉冲与CCD良好配合,才能充分发挥CCD的光电转换、电荷存储和电荷转移等功能。不同型号的CCD要求的工作参数不同,很难设计一种驱动控制电路同时满足多种CCD工作需要,即使是相同像元数的CCD器件,若型号不同也不具有互换性。

TCD1206传感器的驱动脉冲都为周期性方波,但周期和占空比不同。其4路驱动脉冲之间需要满足特定的时序关系:根据驱动脉冲时序图可知在1个SH周期中至少有1 118个φ1脉冲。即TSH>1 118T1,T1为驱动脉冲φ1的周期。这里选择TSH=1 128T1。在SH为高电平期间,要求 φ1与φ2有一个大于SH=l持续时间的宽脉冲,这是由于此时像元中的电荷正在向两列寄存器中转移,如果在此期间φ1与φ2有上升或下降沿出现,则会造成电荷转移不完全的情况。时钟脉冲 φ1,φ2频率的最大值是1 MHz,典型值是0.5 MHz。复位脉冲RS频率的最大值是2 MHz,典型值是1 MHz。本设计中都选用典型值。而且 φ1、φ2必须反相,占空比1:1;SH的高电平脉冲宽度要小于φ1,φ2;RS与 CLK时钟的占空比为 1:4。

3.2.1 原理图设计

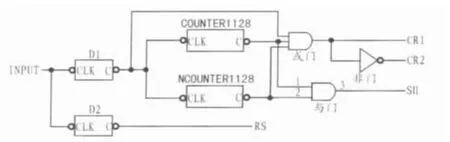

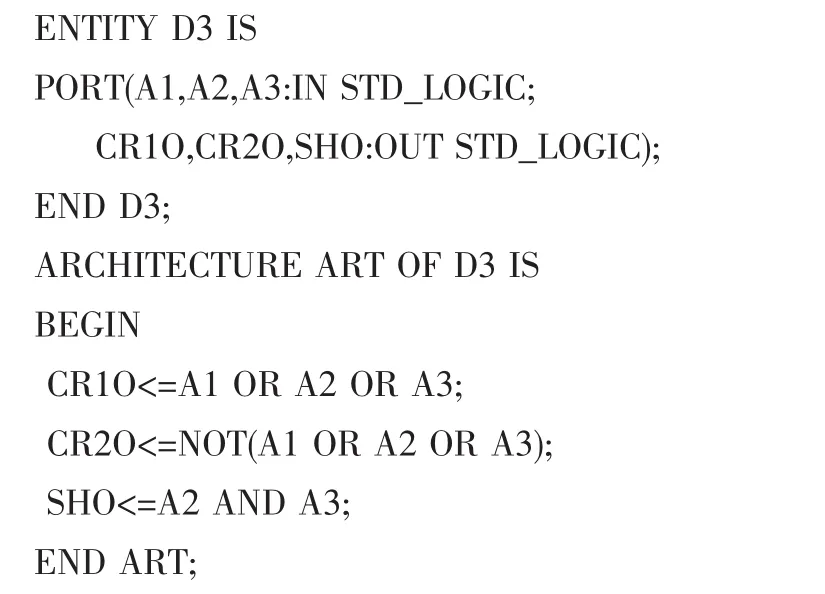

确定SH、φ1、φ2和RS的参数后,则可根据它们之间的时序关系设计硬件逻辑图,如图3所示。

图3 TCD1206驱动电路逻辑图

本设计利用CPLD作为硬件设计平台,它具有较高的灵活性,电子电路设计完成后,如果需修改时序逻辑,只需重写CPLD内部逻辑电路即可。因此,CPLD非常适合用于设计CCD驱动电路[7-8]。

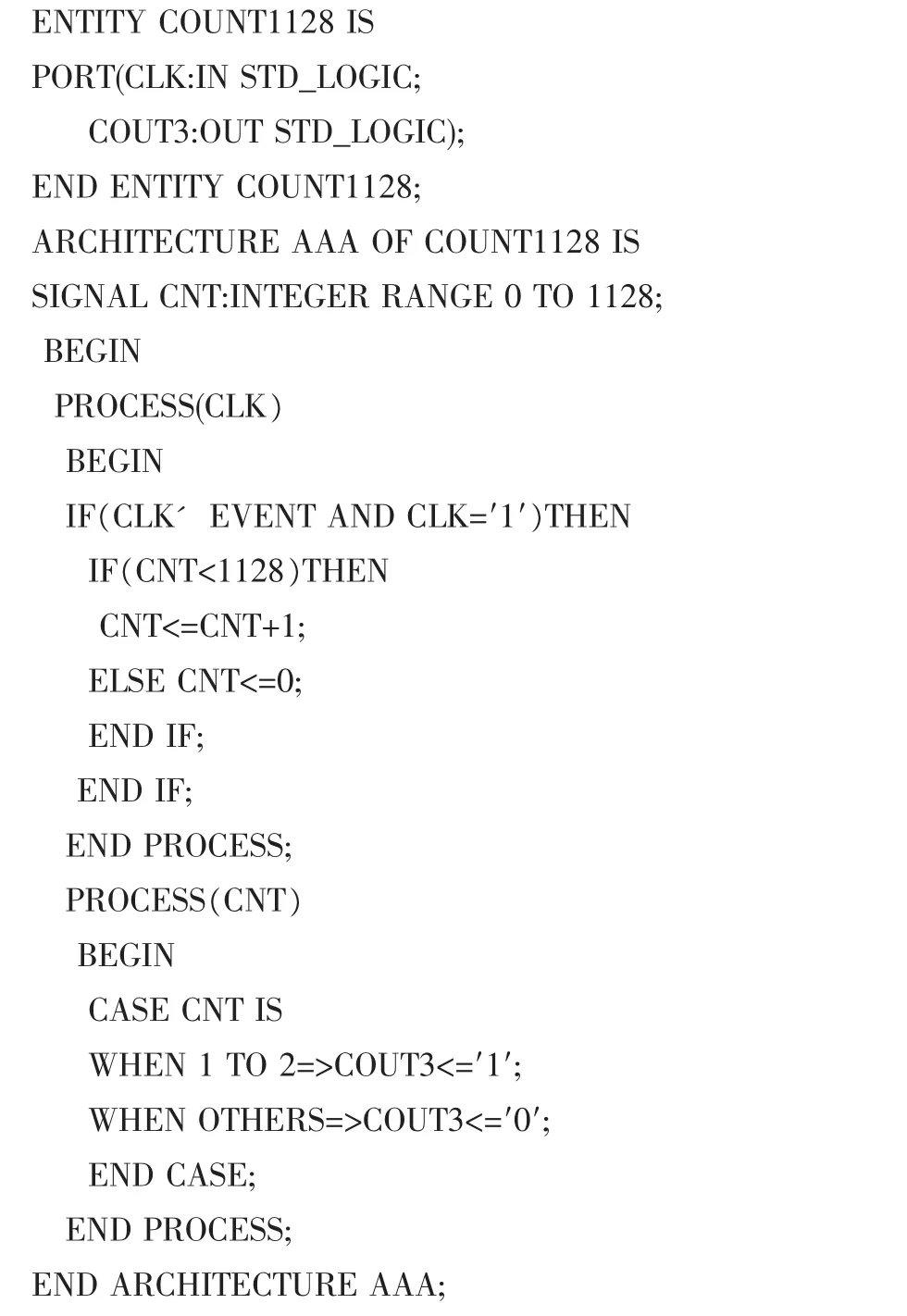

各个模块的设计采用VHDL语言描述。采用4 MHz的时钟CLK作为输入的时钟,D1模块用于将时钟信号进行8分频,将4 MHz的时钟频率分成0.5 MHz。D2模块是将时钟频率分成 1 MHz,占空比为 1:4。COUNTER1128模块和NCOUNTER1128模块分别是上升沿和下降沿计数,计数范围在0~1128之间循环,在前两个时钟为高电平,其余时间都为低电平。

电路实现是先用Dl模块将4 MHz的时钟频率分成0.5 MHz,用0.5 MHz的脉冲作为COUNTER1128和NCOUNTER1128的输入端,将COUNTER1128和NCOUNTER1128的输出相与,输出结果就是SH,将D1和COUNTER1128以及NCOUNTEER1128的输出进行逻辑或,则得到φ1,再将φ1反相,得到φ2,由D2模块可直接得到RS。

3.2.2 模块电路的VHDL设计

每个模块的VHDL设计都包括如下部分:1)定义所需的库函数;2)定义输入、输出端口;3)对设计所需预置数初始化;4)相关功能的实现语句[9-10]。CCD驱动程序主体部分设计如下:

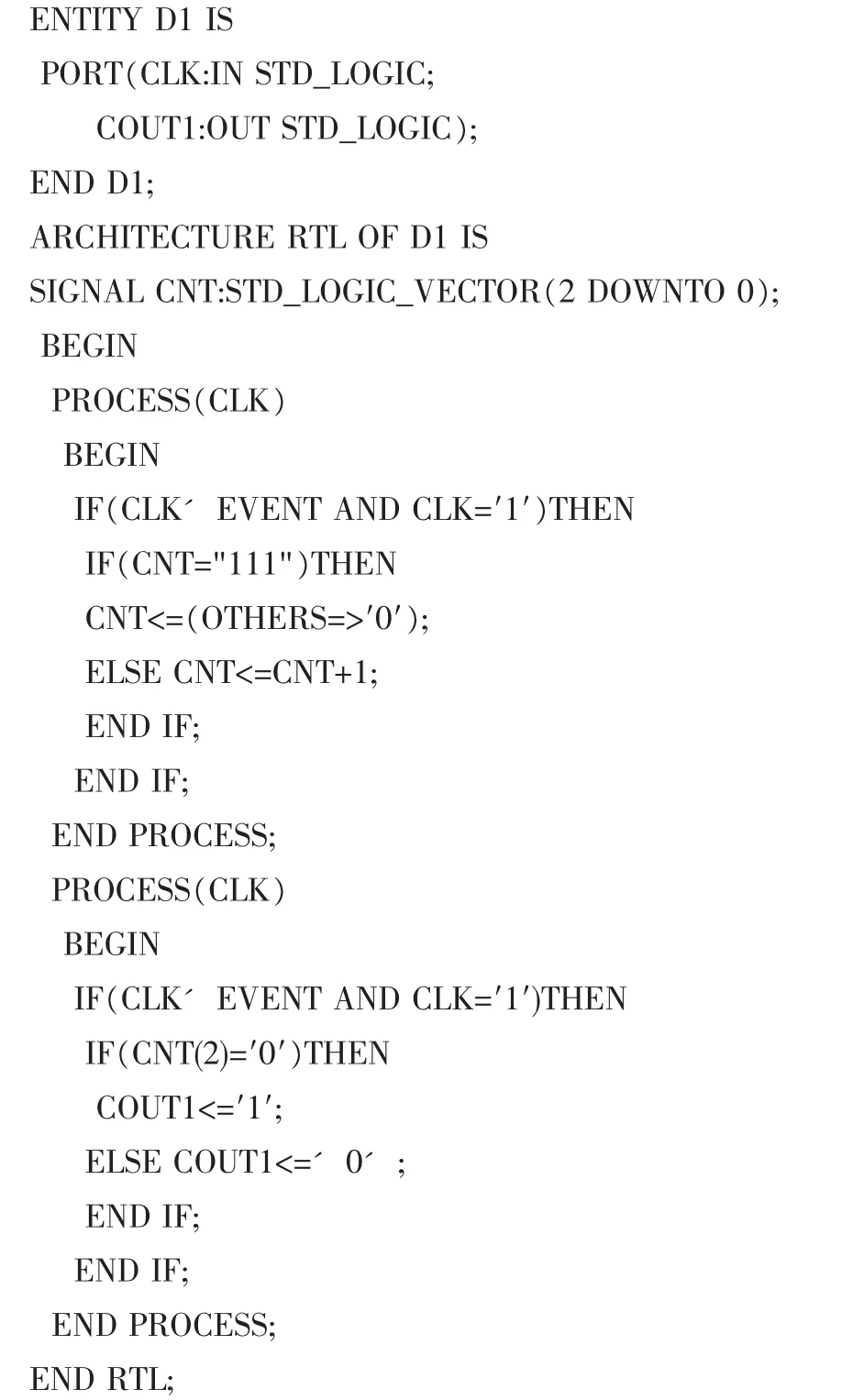

1)D1模块的8分频设计

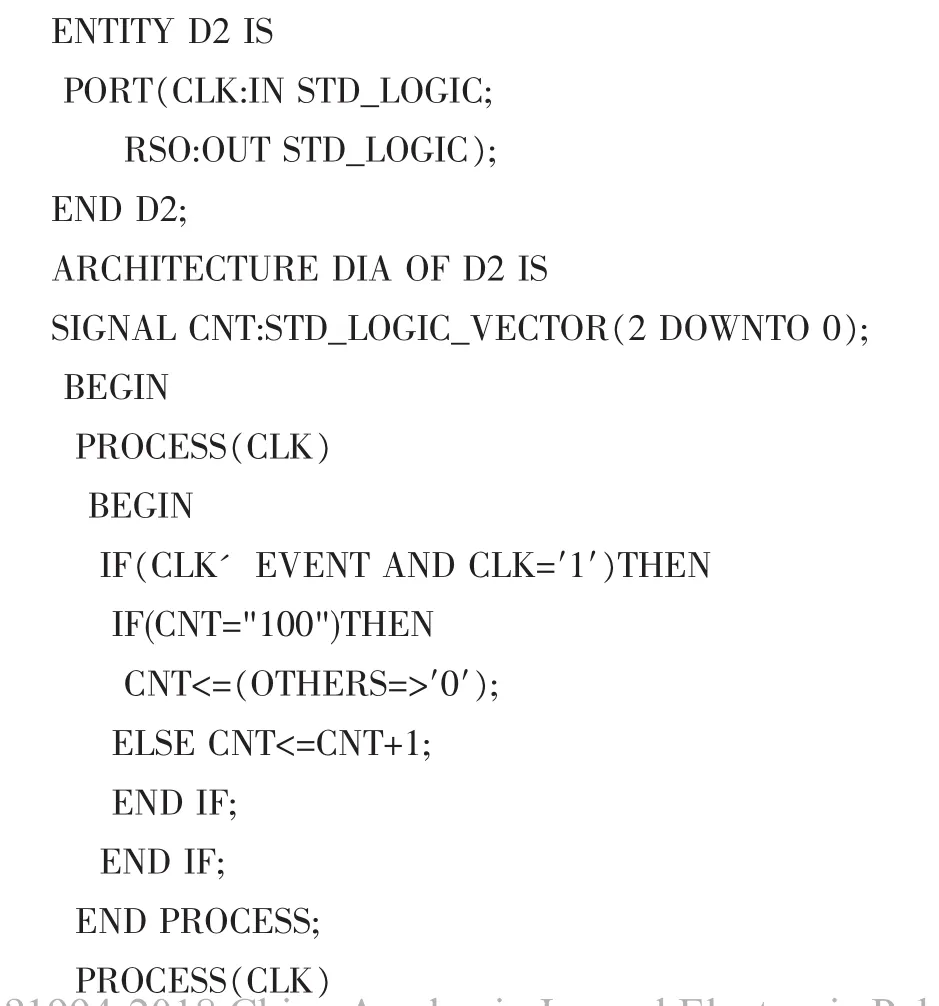

2)D2模块与CLK占空比为1:4的分频设计

3)计数器COUNTER1128设计

4)D1模块、COUNTER1128模块与 NCOUNTER1128模块综合后产生φ1,φ2,SH 设计

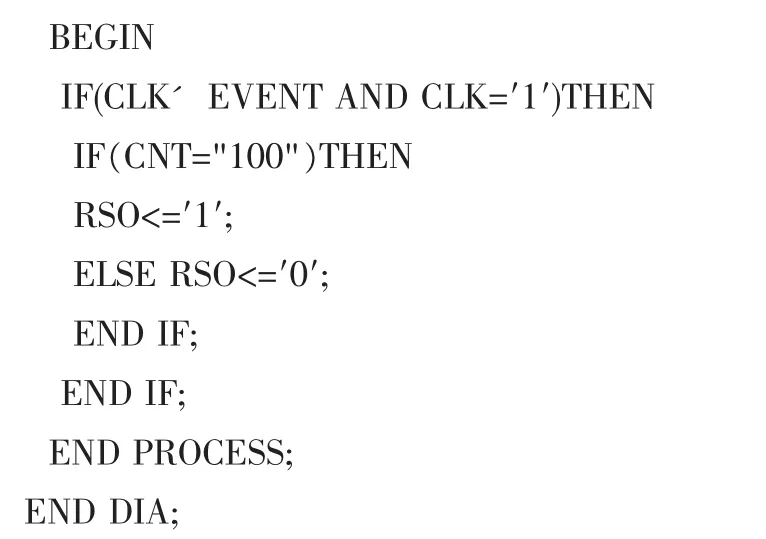

4 设计结果仿真

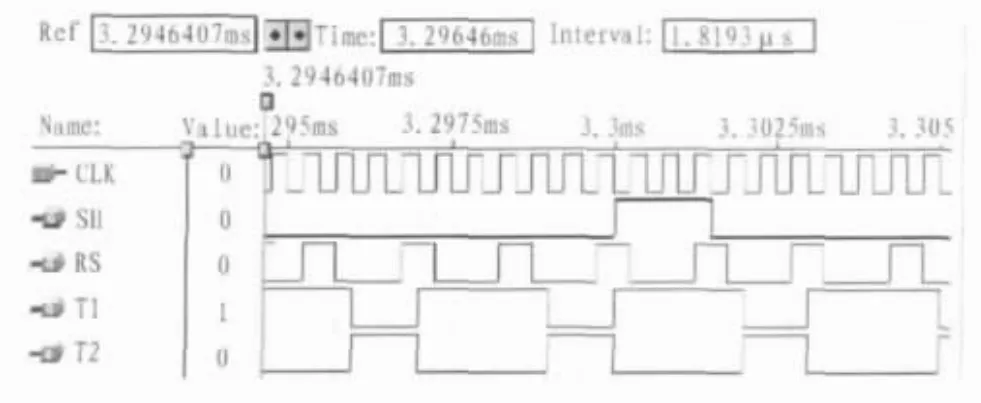

图4是在Altera公司的QUARTUS II开发系统中仿真的波形,从图中可以看出,产生的4路驱动脉冲完全满足TCD1206所需的时序脉冲,达到驱动要求。

图4 CCD驱动时序仿真波形

5 结束语

VHDL是一种自上向下设计的硬件描述语言,同时又具有高级语言的特性,这使得用这种硬件描述语言设计的逻辑功能比较容易实现。同时VHDL语言具有很好的可重用性和可移植能力,能够减轻工作量。利用VHDL设计整个传感器的驱动,并与硬件原理图相结合,不同于以往以单纯的硬件设计实现,这样不仅利于修改而且设计周期短。因此,基于VHDL对TCD1206驱动电路的设计是一种较实用的设计方案。

[1]Wang Qingyou.Study on vibration measurement with the use of CCD[J].SPIE,1999(3):339-341.

[2]唐贤远.传感器原理及应用[M].北京:电子工业出版社,2000.

[3]蔡文贵.CCD技术及应用[M].北京:电子工业出版社,1992.

[4]刘文耀.数字图像采集与处理[M].北京:电子工业出版社,2007.

[5]王庆有.CCD应用技术[M].天津:天津大学出版社,2002.

[6]孟立凡.传感器原理及应用[M].北京:电子工业出版社,2007.

[7]常丹华.基于CPLD技术的CCD驱动时序产生方法[J].仪表技术与传感器,2001(3):26-28.

[8]姜雪松,吴钰淳,王 鹰,等.VHDL设计实例与仿真[M].北京:机械工业出版社,2007.

[9]刘爱荣,王振成.EDA技术与CPLD/FPGA开发应用简明教程[M].北京:清华大学出版社,2007.

[10]侯伯亨,顾 新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2004.

Driver design of image sensor TCD1206 based on VHDL

CUI Peng-peng,LIU Yan-ping,YANG Yu-zhi

(School of Information Engineering,Hebei University of Technology,Tianjin300401,China)

The main features,structural principle,pin functions of TCD1206 are introduced and its drive cycle time is analysed particularly.Through researching the implementation of image sensor TCD1206 driver pulse by VHDL and logical design principle,the VHDL programming of drive pulse and the timing simulation of waveform are completed.The simulation result shows that the driving circuit is feasible.

TCD1206;linear CCD;drive cycle;VHDL

TP18

A

1674-6236(2010)01-093-04

2009-05-08 稿件编号:200905013

崔朋朋(1984—),女,河南平顶山人,硕士。研究方向:通信测控技术。