24 bit、4通道、高动态范围、每通道156 kS/s同步采样数据采集系统

电路功能与优势

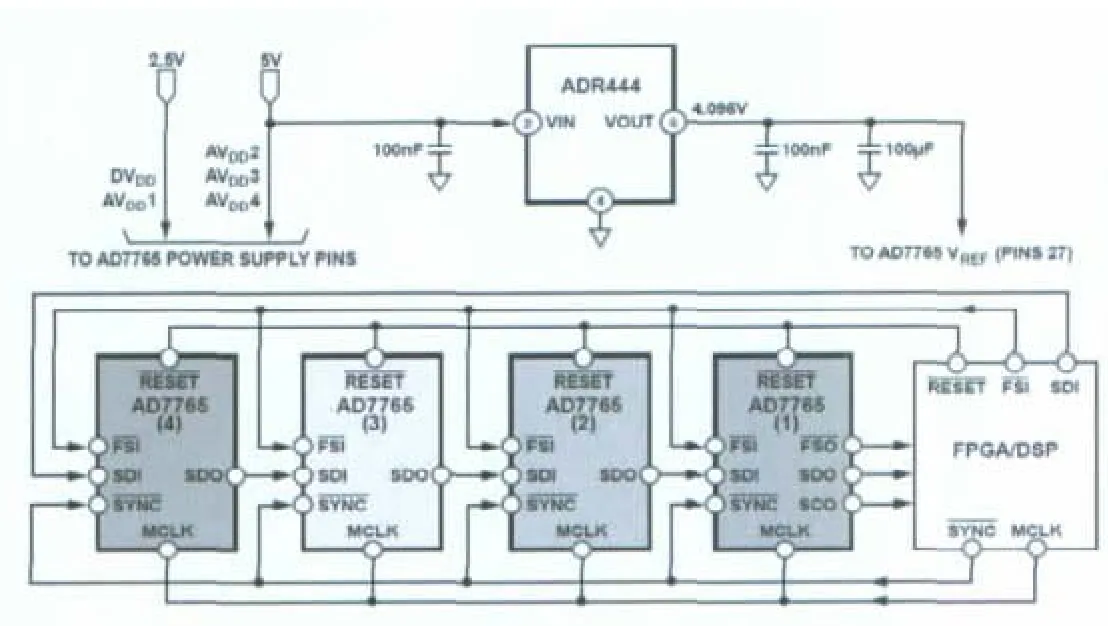

图1所示电路提供一种高动态范围4通道同步采样系统,它具有高串扰隔离度和灵活的采样速率,所需外部器件极少,能够轻松连接到DSP或FPGA。该电路的4个Σ-Δ型ADCAD7765采用菊花链配置,因此到数字主机的连接数量被减至最少。AD7765完全集成差分输入/输出放大器和基准电压缓冲器,所需的外部器件数量得以显著减少。

图14 个菊花链连接的AD7765 ADC实现同步采样

使用同步采样配置的AD7765可提供以下优点:

·通道间串扰隔离度优于单芯片集成多个24 bit ADC的解决方案;

·在156 kS/s时的动态范围为112 dB;

·支持更多或更少的通道数;

·支持多种SYNC控制(彼此之间可以存在相移);

·双抽取速率(128和256)和灵活的采样时钟能够处理宽输入带宽范围。

电路描述

每个AD7765利用公共采样时钟(MCLK)、同步信号(SYNC)和复位信号(RESET)提供时钟,如图1所示。ADR444提供的4.096 V公共基准电压(使用图5所示电路)以星形单点配置施加于每个AD7765(各ADC内置基准电压缓冲器)。

上电时给所有器件施加一个RESET脉冲(脉冲的最短低电平时间为1×MCLK周期)。RESET上升沿(使ADC离开复位状态)施加于各AD7765,以便与MCLK下降沿同步。然后将一个SYNC脉冲(最短低电平时间为4×MCLK周期)施加于所有AD7765器件,其作用是选通AD7765的数字滤波器(当它为逻辑低电平时)。在SYNC回到逻辑高电平后的第一个MCLK下降沿,AD7765的数字滤波器开始在内部处理采样。

SYNC功能起到两个作用:(1)为各AD7765提供离散的时间点以便开始处理采样。(2)确保各器件SDO引脚的数据输出同步(各ADC的FSO下降沿同步),如图2所示。

图2 各AD7765通道的FSO的示波器图,以156 kS/s的输出数据速率同a步采样放大

一旦所有器件同步,就可以配置所有ADC。菊花链工作模式要求所有ADC使用相同的抽取率(由引脚18控制)和功耗模式(通过写入控制寄存器地址0x0001进行控制)设置,从而确保各器件的数据同步输出。

为了写入菊花链中的所有4个器件,需将一个公共FSI(帧同步输入)信号施加于所有AD7765。对AD7765的写操作由32 bit组成(16个地址位、16个寄存器位)。FSI以帧形式将数据传输到器件。写入所有4个器件时,菊花链的SDI输入利用单个数据写入指令进行加载,即当FSI变为低电平时,32 bit数据写入AD7765(4)的SDI(串行数据输入)。

本笔记中的示例以正常功耗模式工作,抽取系数为128(最大输出数据速率为156 kS/s)。

阅读本文更多细节请访问:

http://comm.ChinaAET.com/ADI/Circuit201106.html。