基于FPGA的出租车计费系统的设计与实现

姚利彬,许 勇,潘 明

(桂林电子科技大学 电子工程与自动化学院,广西 桂林 541004)

随着出租车行业的发展,出租车在交通运输中承担着重要的角色,具有良好性能的计价器对加强行业管理以及减少乘客与司机之间的纠纷是必不可少的。采用模拟电路和数字电路设计的计费系统整体电路较复杂,器件多,故障率高且难调试。目前市场上的出租车计费器主要采用的都是利用微控器如89C51、μPD78F0034单片机设计的计费器[1]。

传统的出租车计费器由于发展使用了十几年,在稳定性、成本、以及使用习惯上都具有一定优势,但在运行过程中系统不是很稳定,有时会造成死机的现象。而且基于单片机设计的计费器产品更新周期长,大部分功能可用单片机来实现,但是单片机程序是不通用的,不同的芯片有不同的指令集,因此设计研发比较困难,周期长。如果系统设计的不好,则系统不稳定,且灵活度不够,不易实现功能复杂的设计。再者,计价方式也不够不灵活,每次计价标准的修改都需要将芯片重新烧录,使得每次调价都需要耗费大量的人力物力,很难达到目前油价联动的需求[2-3]。这些都体现了目前对出租车计费器市场更新换代的需求。比较而言,基于FPGA的计费系统不像微控制器那样会漏掉某些特性,它可以编程,并根据需要重新编程,快速完成原型开发,更迅速地将产品推向市场[4]。如果需求变化了,还可以在现场对其进行更新。

本设计采用Alter的CycloneⅢ系列EP3C5E144C8型芯片,利用VHDL语言,实现对出租车的多功能计费器设计,采用LCD1602液晶输出显示,如需要,只需重新锁定输出端口,便可外接七段数码管显示。该计费系统,不但能实现基本的计费,而且还能根据行驶的路程、总费用等调节行驶单价。最后将可执行文件下载到康芯公司的KX_7C CycloneⅢ系列EP3C5E144C8型实验开发系统上进行验证。经实际电路验证,该系统可以实现通过程序设置起步价格、行驶单价、等待计费价格,并且计费正常,达到了预先设计要求。

1 出租车计费器的系统要求

出租车计费系统应有的功能有:1)车起步开始计费,起步价为7元,车行驶5 km以内,只收取起步价。2)车行驶超过5 km后,每千米收费1.6元,在起步价的基础上每行驶1 km累加计费。3)当总费用达到或超过100元时或行驶公里数超过50 km后,每千米收费上升为2.4元。4)当遇到等红灯或客户需要停车等待时,前5分钟等待时间计价器不计费,超出5分钟后的等待时间按每60 s收费0.8元计费。5)若计价器收到暂停命令,则不计费,车费保持不变。若收到停止命令,则车费清零,计费标准返回初始值,等待下一次计费开始。

要求本系统能够实现计费器预置功能,即能够预置起步价、单价、涨价里程、涨价费用、计时收费标准等。并且可以模拟汽车行驶、暂停、停止等状态,根据不同状态进行计费。以十进制显示租车行驶路程、收费标准、总费用及等待时间[5]。

2 出租车计费系统的整体设计方案

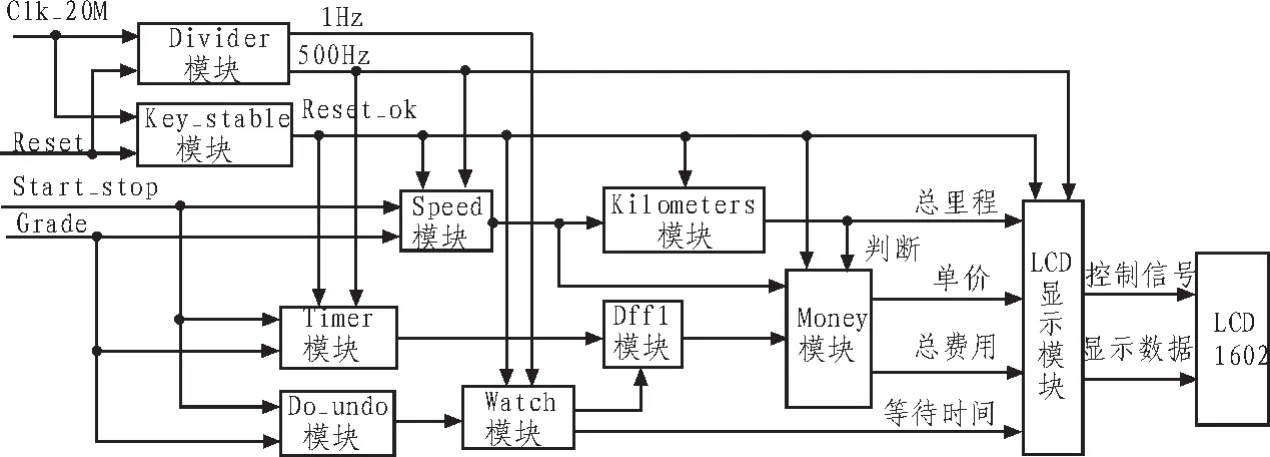

从上述设计要求中可以得出出租车计费器的系统结构图,如图1所示。整个出租车计费系统按功能主要分为分频模块、速度模块、时间模块、倒/正计时模块、计程模块、计费模块和LCD1602显示模块。

系统接收到reset信号后,总费用变为起步价7元,倒计时寄存器变为05:00(5分钟),同时其他计数器、寄存器等全部复位。

系统接收到start_stop信号后,首先把部分寄存器赋值,总费用不变,通过对总费用和总路程的判断后单价unit_price赋值为1.6元,其他寄存器和计数器继续保持原始状态。

Grade信号是速度传感器的输入信号,本设计采用4位二进制数来模拟输入脉冲频率的大小,并与速度模块中预先设置好的速度大小进行比较,为计程模块提供100 m路程标志脉冲。系统采用经过分频模块产生的1 Hz和500 Hz的时钟信号[6]。

图1 系统结构图Fig.1 System structure

3 具体电路模块的功能

Key_stable模块:通过对reset信号的采样判断处理,能够对reset按键进行消抖处理[7-8],防止由于微小震动而产生的复位信号。

Divider模块:生成适合于本系统需要的500 Hz与1 Hz的时钟信号。

Speed模块:通过对速度信号Grade的判断,决定变量need_100m的值。need_100m即是行进100 m所需要的时钟周期数,当到达到所需的时钟周期数后,产生一个脉冲clk_100m。

Timer模块:在汽车启动后,当遇到顾客等人、红灯或堵车不能前进时,出租车采用计时收费的方式。通过对速度信号Grade的判断决定是否开始记录时间。当Grade为零时,开始记录时间。当时间达到预设时长时则产生clk_time脉冲,并重新计时。一个clk_time脉冲相当于等待的时间达到了计时收费单位。本设计采用60 s的计时收费单位。

Do_undo模块:通过对速度信号Grade与Start_stop信号的判断,来控制Watch模块工作还是暂停状态。

Watch模块:通过对do_undo输出信号的判断,当输出1时,本模块内的倒计时dec_watch模块先开始工作,并使得二选一mux2_1模块选择倒计时显示输出;当倒计时到00:00时,倒计时停止的同时正计时inc_watch模块从00:00开始计时,并使得mux2_1模块选择正计时显示输出。dec_watch模块与inc_watch模块分别由模为十和模为六的减/加法计数器构成,其内部系统结构如图2所示。

图2 Watch电路模块内部系统结构图Fig.2 Structure of watch circuit module

Dff1模块:由Watch模块输出的flag信号来控制Dff1的选通,当flag=0时,即还处在倒计时状态下,dff1关闭,使得Timer模块输出的 clk_time不能通过 dff1传送给Money模块;当在正计时状态下,flag=1,dff1打开,使clk_time传送给Money模块进行计费,这样就实现了预设时间内不收取等待时间费用的功能[9-10]。

Kilometers模块:由于Speed模块传送来的一个clk_100m信号代表行驶100 m,故通过对clk_100m计数,可以获得总行进的距离km_cnt。

Money模块:由两个进程组成。其中,一个进程根据Kilometers模块输出的行驶里程判断是否超过5 km,超过后开始按每公里进行收费,当行驶公里数大于50 km或者总费用大于100后,则单价unit_price由原来的1.6元/km涨为2.4元/km;第二个进程在每个时钟周期检测Speed模块的输出信号clk_100m是否累积到10个(即1 km),同时检测Dff1模块的输出信号clk_time_ok的值。当行驶公里超过5 km且clk_100m累积到10个后总费用加上行驶单价,当检测到clk_time_ok=1时,总费用上加上计时收费单价。模块中嵌入了将二进制数转换为十进制的B_to_BCD模块,将行驶单价和总费用转化为可读性更强的十进制输出。

LCD显示模块:系统采用字符型液晶显示数据,将行驶单价、总公里、总费用以及等待时间在LCD上显示。1602液晶具有体积小、外围电路简单、稳定性好而且价格低廉,综合考虑所以选用LCD1602而并没有采用电路较为复杂的LED数码管。但为适应实际应用中不同的显示方式,在程序设计时,将数据输出格式调整为BCD码,可以很方便地将LCD1602更换为七段LED数码管显示,满足不同客户的要求。

4 系统部分核心模块的实现

4.1 速度Speed电路模块

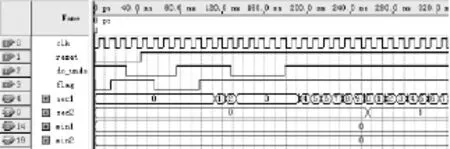

该模块是模拟实际速度脉冲信号的模块。通过对开始信号start_stop和速度信号grade进行判断,对系统时钟进行计数,当计数达到与grade值相对应的数目时输出一个clk_100m脉冲。Speed电路模块仿真波形如图3所示。

图3 Speed电路模块仿真波形Fig.3 Simulation waveform of Speed circuit module

仿真时采用的是100MHz的时钟脉冲,当reset无效且stat_stop为高电平时,输出clk_100m信号的频率随着grade的大小发生相应变化。

4.2 计时Timer电路模块

Timer模块用于计时收费,记录允许计费后出租车速度为零的时间。通过对Grade信号的判断,当Grade=0时开始记时。当累积时间达到预设时长,则产生clk_time脉冲,并重新计时。模块的仿真波形如图4所示。从图中可以清楚看到,在允许计费时段,当Grade=0时,每隔固定时间会有一个clk_time脉冲,在Grade不为零时,没有clk_time脉冲输出。

图4 Timer电路模块仿真波形Fig.4 Simulation waveform of Timer circuit module

4.3 等待时间W atch电路模块

该模块是完成倒/正计时的功能模块,输入频率为1 Hz,当do_undo=1时开始计时,当do_undo=0时暂停计时。无论在什么状态下,只要reset=0,则该模块输出为程序中设定好的05:00(5 分钟)。

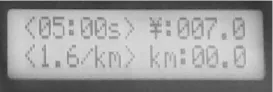

Watch电路模块内部是由3部分构成的,第一部分就是倒计时钟dec_watch模块,该电路根据对信号do_undo的判断,开启倒计时工作,当倒计到00:00时,输出端flag置1,并反馈给dec_watch模块,使其停止工作。dec_watch电路模块仿真波形如图5所示。由dec_watch电路模块的仿真波形可以看出,当倒计时到00:00时,再来一个clk脉冲后flag被置为1,且停止倒计时。

图5 dec_watch电路模块仿真波形Fig.5 Simulation waveform of dec_watch circuit module

第二部分就是正计时钟inc_watch模块,该电路通过对信号do_undo和dec_watch模块输出信号flag的判断,开启正计时电路。inc_watch电路模块仿真波形如图6所示。由仿真波形图可以看出,复位信号结束后,当do_undo=1且flag=1时,inc_watch电路开始正计时,当do_undo=0时,正计时处于保持状态。

图6 inc_watch电路模块的仿真波形Fig.6 Simulation waveform of inc_watch circuit module

4.4 里程Kilometers电路模块

此模块主要用于记录行进的距离,通过对clk_100m信号的计数,计算行驶的距离km_cnt。一个clk_100m脉冲表示行驶100 m,所以只要记录clk_100m脉冲的数目即可确定行驶的距离。km_cnt0为十分位,km_cnt1为个位,km_cnt2为十位,分别为十进制数,Flag_100 km为满量程溢出标志位,light是为了体现速度快慢的输出端口,顺序连接上LED灯后,能够直观的看到速度的大小。此模块的仿真波形如图7所示。

由仿真波形图可以看出,当行驶公里数达到99.9 km后,Flag_100km加1,公里数又重新从零开始计数。而且伴随着公里的增加,light也在进行循环变化。

图7 Kilometers电路模块的仿真波形Fig.7 Simulation waveform of kilometers circuit module

4.5 Money电路模块

计费模块可分为M1、M2两个进程和二进制转BCD码模块。M1进程用于设置公里收费的单价unit_price和产生允许按公里计费的en_km信号。当记录距离达到5 km后,en_km=1,允许开始按公里收费。当总费用大于100元或行驶总公里数超过50 km后,单价unit_price由原来的1.6/km变为2.4/km。

M2进程用于进行总费用的累计。当clk_time_ok=1时,总费用加上等待时间单价wait_unit_price;当en_km=1且对clk_100m=1计数达到10时,总费用加上公里收费的单价unit_price。为了进行加法运算时候更便捷,此处采用的是二进制加法,要显示出十进制数字,需将总费用和单价经过B_to_BCD模块进行转换,输出总费用以及单价的BCD码,以便显示模块进行显示输出。

4.6 LCD显示电路模块

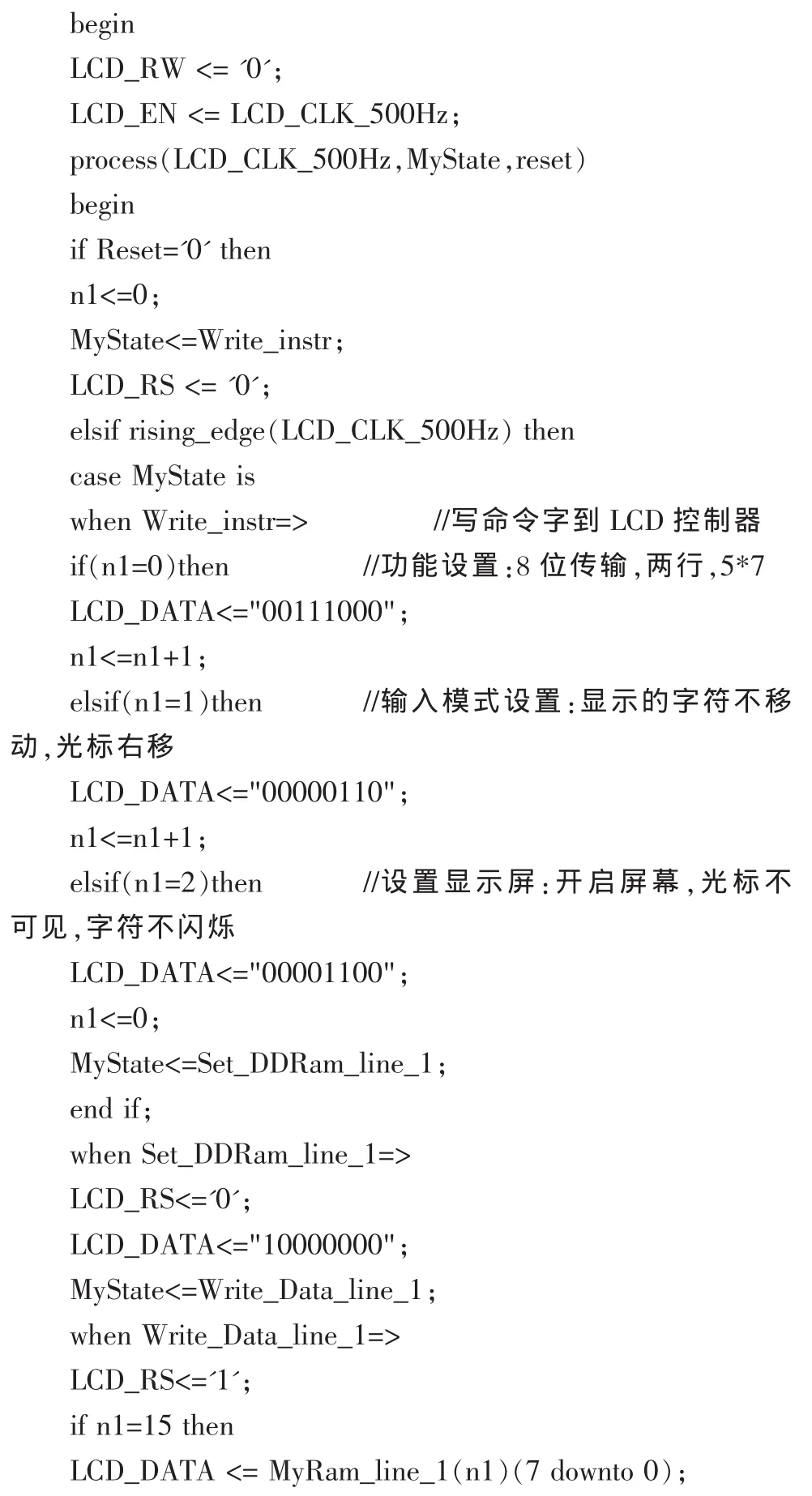

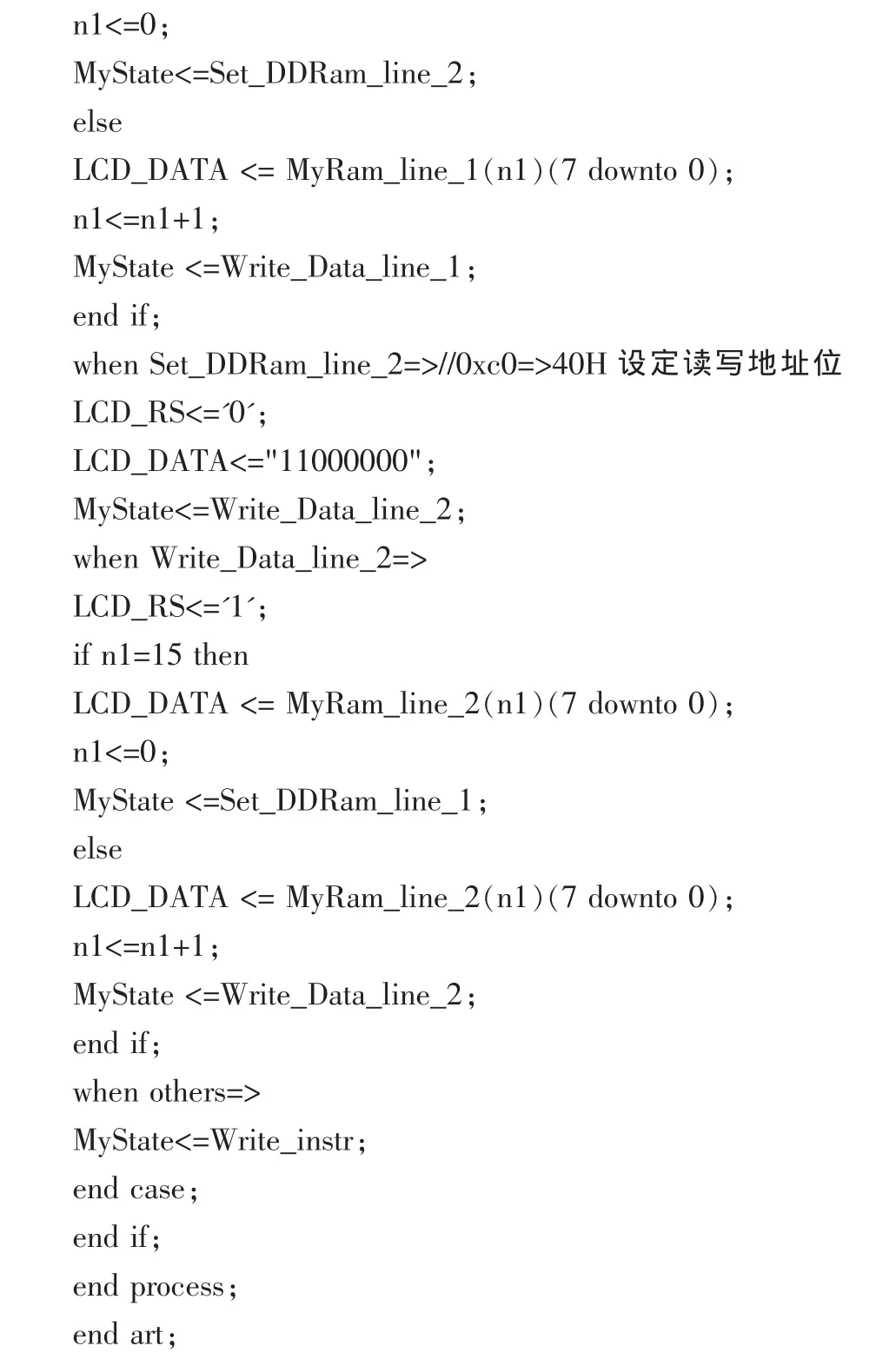

将各个模块输出的需要显示的数据(总费用,行驶公里,等待时间,当前行驶单价 )传送给此电路模块,经本电路将数据输出显示到LCD1602上。由于LCD1602显示的是数据的ASCⅡ码值,故在将要显示的数据前先转换为对应数字的ASCⅡ码值,再将此值传送给LCD1602[11]。利用VHDL编写的LCD1602显示核心程序为:

利用VHDL状态机实现对LCD1602的数据写入。图8为LCD1602显示屏的初始状态。

图8 LCD1602显示屏的初始状态Fig.8 Original state of LCD1602

5 整个系统的测试

根据以上10个模块的程序,编写顶层程序文件(TAXI_TOP.vhd),进行编译,锁定引脚。整个系统的输入引脚共有 7位,一位时钟信号(clk_20M),一位复位信号(reset),一位启动/暂停信号(start_stop)和4位速度信号(grade)。输出引脚共有 27位,其中 3位 LCD1602控制位(RS/RW/EN),8位数 据 (DATA),8 位 速 度 指 示 灯 (light),4 位 百 公 里 标 志(Flag_100km),4 位千元标志(Flag_1000RMB)。

由clk_20 M引入20MHz时钟频率,reset锁定到一个常高按键,start_stop锁定到一位拨码开关,grade[3..0]由4位拨码开关输入。Light[7..0]锁定到8个LED灯上,Flag_100km[3..0]和Flag_1000RMB[3..0]分别锁定到两位LED数码管上,RS、RW、EN、DATA[7..0]分别锁定到对应的LCD1602的输入引脚上。通过编译把程序下载到康芯 KX_7C CycloneⅢ 系列EP3C5E144C8型实验开发系统上进行实验测试。

首先将start_stop和grade[3..0]置零,然后按下复位键reset,液晶屏上显示免费等待时间“<05:00>”,公里计费单价“<1.6/km>”,起步价“¥:007.0”,行驶公里数“km:00.0”。

当把start_stop置1后,倒计时钟开始倒计时,表示开始计费,处在等待状态。若此时将grade置为任何一个非零值,则倒计时钟停止倒计时,并且公里数开始增加,同时8位LED数码管顺序点亮,点亮的速度随着grade的值增大而增大。公里数超过5 km后,每增加1 km,总费用累加1.6元。当公里数涨到50 km后,行驶单价由1.6变为2.4,每再增加1 km,总费用累加2.4元。直到公里数增至100 km,公里数溢出标志数码管加1,而LCD1602显示公里数变为0。此时,如果将grade置零,则倒计时钟又接着开始倒计时。当倒计到00:00时,开始正计时,且每1分钟,总费用累加0.8元。当总费用达到1 000时,总费用标志数码管加1,LCD1602显示的总费用从零开始继续计费。我们还可以复位后重新开始测试,让公里数未到达50 km时,使grade为零,系统进入等待计费状态,直到总费用增至100元后,行驶单价也会由1.6元变为2.4元。

在上述过程中,一旦start_stop置0,整个系统将处于暂停状态,停留在暂停前一时刻的状态。一旦reset置0,整个系统复位,回到初始状态。

本系统中各个收费参数标准都可精确到0.1元,在程序中可轻松更改起步价、里程单价、等待时间收费单价等参数,而无需费力更改大量程序。

由于在数字电路的输入信号中抖动是不可避免的,抖动会造成严重的后果。所以对输入信号去抖是逻辑电路设计中的必要环节,也是提高数字系统电磁兼容能力的关键技术[10]。所以在系统中加入了复位按键去抖电路 (Key_stable电路模块),有效的防止在汽车上嘈杂震动环境下的误操作。

在使用康芯CycloneⅢ系列EP3C5E144C8型芯片实验板时,为了实验演示清晰明了,利用仅有的8个LED灯顺序点亮快慢以表示行驶速度的大小,以为客户显示更直观的效果。由于系统总费用的量程范围为999.9元,总公里数的量程范围为99.9 km,为了能够显示更大的量程范围,利用实验板上的两位LED数码管分别表示总费用和总量程的溢出标志位,即每到1 000元或100 km后,相应的溢出位加1,其范围为(1~F),这样该系统显示的总费用量程能够达到 15 999.9元,行驶总公里数能够达到1 599.9 km。

6 结束语

文中运用VHDL语言采用电子产品设计中比较先进的FPGA技术设计了一款出租车计费系统,实现了出租车计费器的主要功能,运行稳定、可靠。EDA技术是以计算机为工具来完成数字系统的逻辑综合、布局布线和设计仿真等工作,电路设计者只需要完成对系统功能的描述,就可由计算机软件进行系统处理,得到设计结果,且修改设计方案如同修改软件一样方便。如本出租车计费系统中设定的起步价、行驶单价、免费行驶公里数、等待时间计费标准、免费等待时间等均不需要硬件电路的支持而直接可以在VHDL源程序中进行修改。可见,利用FPGA可以极大地提高设计效率和灵活度并且修改快捷。

[1]黄再银.基于μPD78F0034单片机的出租车计费器的设计与实现[J].电子设计工程,2004(8):21-24.HUANG Zai-yin.The design and realization of taxi-meter based on upD78F0034 microcontro//er[J].Electronic Design Engineering,2004(8):21-24.

[2]廖艳秋.基于FPGA的出租车计费器设计[D].成都:电子科技大学,2008.

[3]焦敏.FPGA在出租车计费器上的应用研究[J].中国科技信息,2009(9):145-146.JIAO Min.Research of taximeter based on FPEA[J].China Science and Technology Information,2009(9):145-146.

[4]San Jose.实现灵活的汽车电子设计[R].Altera公司:2007.

[5]刘欲晓,方强,黄宛宁.EDA技术与VHDL电路开发应用实践[M].北京:电子工业出版社,2009,175-186.

[6]曹公正,陈娟,张宝利,等.FPGA在出租车记费器上的研究与设计[J].长春工业大学学报,2007,28(3):267-270.CAO Gong-zheng,CHEN Juan,ZHANG Bow-li,et al.Design of a taxi meter based on FPGA[J].Journal of changchun University of Technology,2007,28(3):267-270.

[7]白莹杰,杜建铭,罗一星.基于FPGA的脉冲分频技术研究[J].微计算机应用,2010,31(3):67-71.BAI Ying-jie,DU Jian-ming,LUO Yi-xing.Research of the pulse frenquency-division technology based on FPGA[J].micro Computer Application,2010,31(3):67-71.

[8]陈英梅,席亮亮.基于FPGA的多种分频设计与实现[J].电子元器件应用,2007,9(6):47-52.CHEN Ying-mei,XI Liang-liang.Design and implementation of a mult frequency based on FPGA[J].Electronic Design Engineering,2007,9(6):47-52.

[9]陈忠平,高金定,高见芳.基于Quartus II的FPGA/CPLD设计与实践[M].北京:电子工业出版社,2010.

[10]Stephen Brown,Zvonko Vranesic.数字逻辑基础与VHDL设计[M].3版.北京:清华大学出版社,2011.

[11]刘福奇.基于VHDL的FPGA和Nios II实例精炼[M].北京:北京航空航天大学出版社,2011.

[12]潘松,黄继业.EDA技术与VHDL[M].2版.北京:清华大学出版社,2007.