基于DSP的网络通信转换系统设计

刘岩俊,闫海霞,张磊

(1.中国科学院长春光学精密机械与物理研究所,吉林长春130033;2.吉林大学电子学院,吉林长春130012)

以太网接口和RS422串行通信接口作为目前应用最广泛的两种通信接口,被应用到各个领域中。传统的使用计算机的网络接口和串口转换卡的方式,需要以计算机作为主要运算部件,在很多工业场合不方便使用[1-3]。数字信号处理器(DSP)芯片作为一种特殊的嵌入式微处理器系统,是专门为实现各种数字信号处理算法而设计的,嵌入式网络可以有效地用于不方便使用计算机的应用场合,而嵌入式网络开发的应用前景十分广阔,已经成为研究的热点[4-5]。

根据实际项目的使用要求,本文使用TI公司的TMS320F2812 DSP芯片与Xilinx的FPGA芯片XC3S400以及ASIX公司的AX88180芯片完成了基于网卡通信控制系统。

1 方案设计

系统以TI公司的TMS320F2812 DSP为中央处理器,该芯片是用于测控领域的16位定点DSP,处理速度达到150 MHz,其主要特点是采用哈佛总线结构,具有快速中断响应和处理能力,具有4 M线性程序地址与4 M线性数据地址,16位的数据总线,以及1 M寻址空间的地址总线;三个外部芯片选择信号[6,7]。DSP负责通信数据信息的处理,接收网络接口数据包,将其转换成串行通信数据包,并且将接收到的串行通信数据返回给网络接口。网络接口控制芯片对收到的网络数据进行处理,将以太网传输的数据格式转换成数据,与DSP处理器进行交互。采用Xilinx公司的Spartan系列的Spartan3-SC3S400芯片作为外部微处理器,该芯片有400 K门,8 M逻辑单元,32×28个CLB(Configurable Logic Block)内部资源。可获得的LUT门为7168;可以使用的逻辑区为3584[8]。FPGA完成以太网接口芯片AX88180的控制和UART实现,采用DS90LV019进行TTL信号与差分信号转换;DSP与FPGA之间采用总线方式进行数据读写操作。系统功能框图如图1所示。

2 硬件电路设计

系统硬件设计分三部分:(1)中央处理器TMS320F2812 DSP与FPGA之间的接口部分,这部分负责系统的通信转换控制;(2)网络控制芯片与FPGA之间的接口,这部分负责以太网数据与总线数据之间的转换;(3)UART接口,这部分负责串行通信数据串并转换。

2.1 DSP+FPGA硬件电路

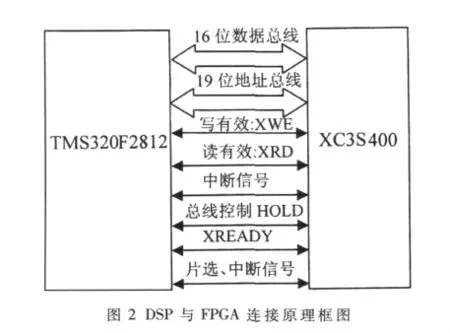

TMS320F2812作为中央处理器;FPGA作为外部接口XINTF与DSP连接,连接内容包括:地址总线Address(18~0)、数据总线(15~0)、片选信号(XZCS0AND1)、DSP读使能(XRD)、DSP写使能(XWE)、外部保持请求(XHOLD)、外部保持应答(XHOLDA)、外部准备后信号(XREADY)、中断控制信号XINT。DSP与FPGA连接原理框图如图2所示。

DSP处理器与FPGA处理器之间采用XINTF总线接口进行数据交互,FPGA作为DSP的一个外部扩展区,DSP处理器需要通过读、写、片选三个控制信号,以及地址总线、数据总线以访问外部SRAM的方式进行读写控制,控制信号通过DSP的外部I/O进行。实现方法如下:首先在FPGA内部构建一个基于分布式块区域异步IP核的SRAM,该SRAM的数据宽度是16位,深度是1 024,具有读写控制信号WE,读时钟RCLK和写时钟WCLK。读时钟RCLK由DSP的读信号XRD赋值,写时钟WCLK由DSP的写信号XWE赋值,读写控制信号WE由DSP的外部扩展IO赋值,当DSP需要写外部SRAM时,IO设置为低;当DSP需要读外部SRAM时,IO设置为高。

2.2 网络接口

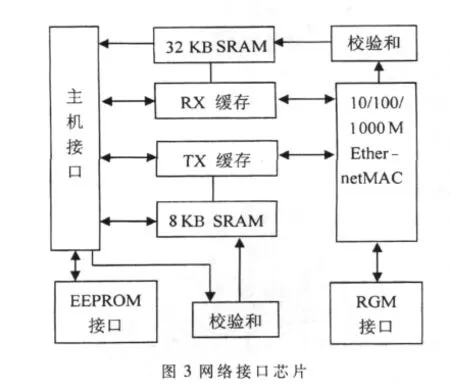

网络控制器选择ASIX公司的AX88180芯片,AX88180芯片是台湾ASIX公司推出的全球第一款Non-PCI接口的千兆以太网络控制芯片。

通过FPGA芯片需要配置其控制信号,网络接口芯片控制原理图如图3所示。

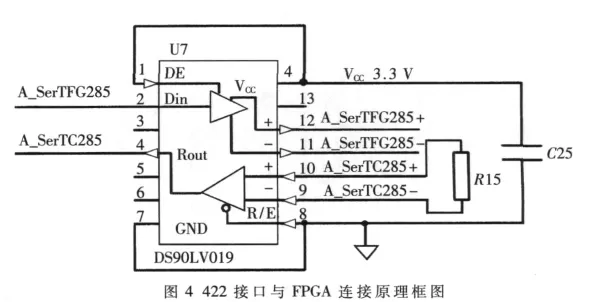

2.3 UART接口

UART接口芯片采用DS90LV019芯片,该芯片电压是3.3 V,接口是RS422/RS485接口与TTL电平转换,电路原理图如图4所示。

3 软件设计

系统软件由两部分组成,DSP软件和FPGA软件,其中DSP软件负责系统的控制工作。FPGA负责系统底层工作,包括网络接口芯片的驱动及数据转换和UART接口的实现。

3.1 DSP软件设计

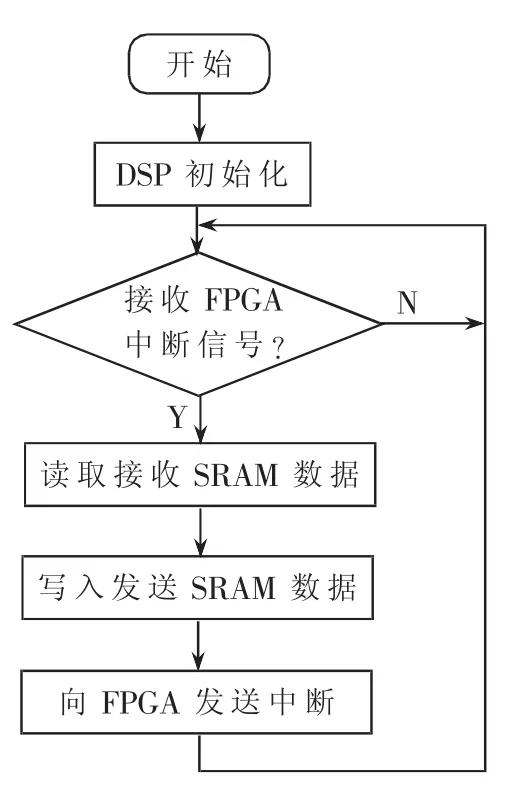

DSP作为系统的核心处理器,系统地控制全部工作过程。DSP首先完成上电初始化,并进行参数设置,完成中断源XINT设置、GPIO设置,然后进入主循环程序,进行系统需要的运算处理。处理过程中,DSP以中断方式接收FPGA提供的中断信号,该中断信号表示网络接口芯片AX88180已经接收到完整的一帧UDP数据包,接收到中断信号后,DSP设置FPGA内部的网络接口SRAM为读操作,读取接收到的网络通信数据。进行数据判断与处理之后,DSP需要通过FPGA内部的发送SRAM向控制端返回数据,DSP先把需要发送的数据写到FPGA内的发送SRAM,这时SRAM的操作信号由DSP产生,数据写好以后,DSP需要产生一个低电压有效的宽度为1 μs的脉冲信号,作为网络发送数据的起始信号。发送SRAM与接收SRAM是FPGA内部建立的两个独立的SRAM,这两个SRAM可以并行操作。需要注意的是,网络接收的数据格式与SRAM内顺序保存的数据格式不同,需要DSP进行数据格式转换。

DSP处理器接收到数据包以后,需要将接收到的网络数据写给UART接口SRAM,然后由UART接口完成数据发送。UART接口接收过程与网络接口接收过程是一致的。

DSP接收网络数据包流程图如图5所示。

3.2 FPGA软件设计

3.2.1 网络接口芯片

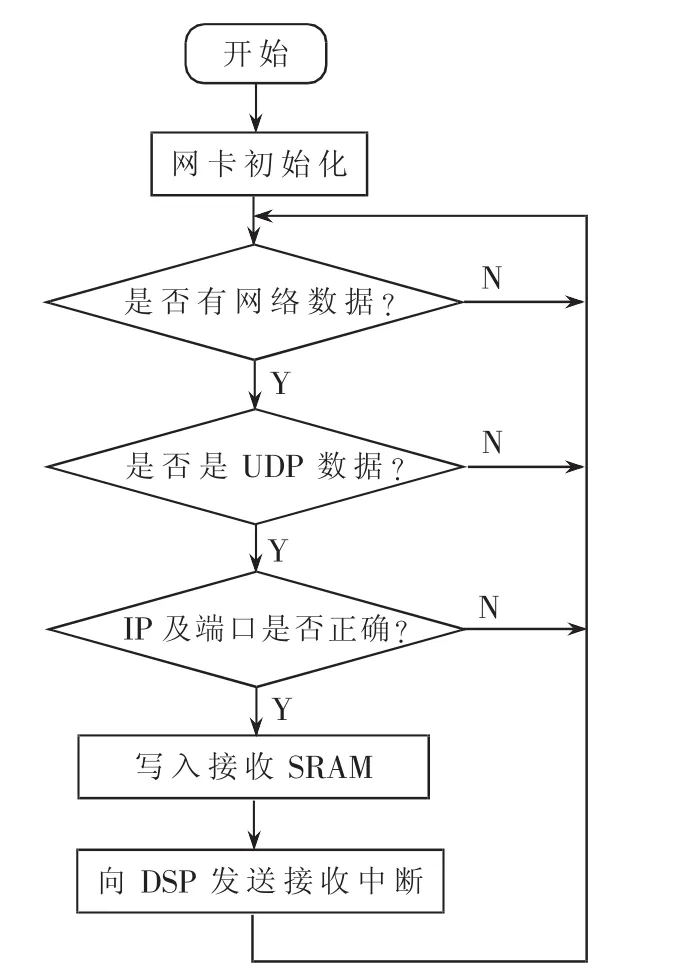

网络接口操作是由FPGA使用VHDL语言实现的,所以接收和发送两个进程可以并行操作。图6是网络接口发送流程图。

图5 DSP软件流程图

图6 网络接口流程图

当网络上有数据时,AX88180对数据包进行分析,如果UDP数据包的目的地址、源地址、端口号都正确,进入数据接收进程,按网络格式把数据保存到FPGA的接收SRAM内,这时,接收SRAM的控制信号是由FPGA产生的,包括写信号、写时钟。数据接收完成后,产生中断信号,并且把SRAM的控制信号交给DSP。

数据发送进程如下:当接收到DSP产生的发送脉冲后,FPGA操作SRAM,并且读出数据,封装目的IP地址、源IP地址、端口号等固定格式,产生UDP数据包,通过网络发送。

3.2.2 UART接口

UART接口与网络接口一样,都采用DSP的外接总线接口XINTF实现,通过两个SRAM与DSP处理器进行数据交互。篇幅原因,这里不再重复。不同的是,UART这里没有采用专用的接口芯片,而是由FPGA使用VHDL语言实现,这样对于程序控制更简单。

4 实验结果

本文提出的硬件设计已经通过实验验证,系统在网络通信速度为1 Gb/s、串行通信速度为230.4 kb/s、8位数据位环境中运行稳定可靠。

本文设计了采用TMS320F2812DSP和以太网控制器芯片AX88180实现的嵌入式系统,设计了系统的硬件电路、以太网接口和UART接口及软件程序。实验表明,该电路实现简单、工作稳定,具有一定的实用价值。

[1]刘岩俊,闫海霞.HDLC通讯协议中CRC的应用[J].电子测量技术.2010,33(3):21-23.

[2]周益,周清根,乔鹏,等.基于FPGA+DSP微小型捷联惯导系统的设计[J].电子测量技术,2008,31(2):119-122.

[3]刘岩俊,闫海霞,何昕.基于FPGA的HDLC协议实现[J].电子器件,2009,32(3):707-710.

[4]徐义忠,孙苓生.基于FPGA的测量数据存储交换技术[J].电子技术应用,2008,34(1):62-64.

[5]王海涛,段哲民.多路数据采集与网络远程传输系统实现[J].计算机测量与控制,2008,16(3):421-423.

[6]姜培培,裘燕青,傅志辉,等.基于DSP和FPGA的多路型光纤光谱仪系统[J].光学精密工程,2006,14(6):944-948.

[7]万山明.TMS320F281xDSP原理及应用实例[M].北京:北京航空航天大学出版社,2008.

[8]Xilinx Inc.Xilinx Spartan-3 Generation FPGA User Guide[S].2008.