基于MPC8280的MCC驱动设计

杨小冬,王俊芳

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

MPC8280具有强大的接口能力和多协议支持功能,非常适用于高端网络和通讯设备[1]。HDLC协议是重要的数据链路层协议,通过一次群(E1)中继传输HDLC数据包是数据传输的重要方式。

MPC8280应用中对外提供5个E1接口,信令和业务使用HDLC协议封装后通过E1中继传输。支持 8个时分复用(Time Division Multiplexing,TDM)接口,并且MCC支持HDLC协议,通过管脚规划可以利用2个MCC的5个TDM实现设计功能,既节约了开发成本又缩短了开发周期。

1 设计方案

高性能处理器MPC8280内含指令单元和指令执行单元,是程序的执行单元;完成对TDM数据流的HDLC格式封装,以及对其他模块的初始化和配置等。

1.1 MPC8280硬件结构

MPC8280结构框图如图1所示。MPC8280采用MPC603e内核和通信处理器模块(Communication Processor Module,CPM)的双内核结构,CPM减少了MPC603e内核对底层通信任务的干预,从而提高了MPC603e内核的工作效率[2]。

图1 MPC8280结构

MPC8280内部结构包含3个主要功能模块:具有内存控制单元和缓存的64位内核MPC603e、系统接口单元(System Interface Unit,SIU)和 CPM。MPC603e具有16 KB的指令缓存和16 KB的数据缓存,执行高层代码,完成对外设的控制管理。SIU完成系统复位、中断管理、时钟配置、总线接口和内存控制。CPM处理底层的通信任务,包括1个32位的精简指令集处理器、2个MCC、3个快速通信控制器(Fast Communications Controller,FCC)、4 个串行通信控制器(Serial Communications Controller,SCC)、2个串行管理控制器(Serial Management Controller,SMC)、1个串行外设接口(Serial Peripheral Interface,SPI)和 1个集成电路互连(Inter-Integrated Circuit,I2C)总线控制器等。时隙分配器(Time Slot Assigner,TSA)完成路由选择和时分复用,将MCC、FCC、SCC和SMC等连接到物理层的TDM管脚,将数据复用到8个TDM接口。

1.2 MCC工作原理

MPC8280具有 2个 MCC,分别为 MCC1和MCC2,每个MCC支持128条独立的时分串行通道,每个通道都可以独立配置为不同于其他通道的工作模式。每个MCC连接到相应的串行接口(Serial Interface,SI),分别为 SI1和 SI2,MCC1的通道(0~127)只能连接到SI1上,MCC2的通道(128~255)只能连接到SI2上[3]。通过配置SI和串行接口随机存储器(Serial Interface RAM,SIRAM)可以将TDM数据中的时隙路由到特定的MCC通道。

CPM通过一系列与MCC相关的数据结构实现对数据的处理。全局参数对MCC通道状态进行全局管理,设定通道的接收门限和寄存器的基地址;通道参数用于设置单个通道发送数据、接收数据的相关寄存器及方式,对MCC通道的先进先出存储器(First In First Out,FIFO)进行管理;外部参数设置单个通道发送缓存描述符(Transmit Buffer Descriptor,TxBD)表、接收缓存描述符(ReceiveBuffer Descriptor,RxBD)表的基地址和指针,用于缓存描述符(Buffer Descriptor,BD)表的索引。BD由状态控制字、数据长度和数据缓存指针3个部分组成,MCC根据BD提供的信息对缓存区进行访问和操作。

当SI的某个TDM被配置为包含有MCC通道的时隙并且TDM被使能,CPM就将MCC通道的发送缓存区内的数据复制到发送FIFO内,然后SI在时钟驱动下将MCC通道的发送FIFO内的数据发送到TDM接口;或者将数据从TDM接口接收下来并存入到MCC通道的接收FIFO内,然后CPM再将接收FIFO内的数据复制到MCC通道的接收缓存区内。

2 需要解决的问题

由于需要使用2个MCC的5个TDM,对相关参数和资源的分配需要合理规划。传统的收发设计采用轮询方式,虽然设计简单,易于控制,但缺点是既增加了系统开销,浪费了中央处理器(Central Processing Unit,CPU)资源,又不能及时响应事件。该设计需要解决的问题包括MCC的初始化设计和MCC收发处理设计等问题。

2.1 MCC的初始化设计

MCC的初始化涉及到配置位于MPC8280内部的双端口随机存储器(Dual-Port RAM,DPRAM)中的全局参数(Global MCC parameters)、通道参数(Channel-specific parameters)、外部参数(Channel extra parameters)和SIRAM等参数;位于外部随机存储器中的BD表参数、中断表等参数;还需要配置TDM的管脚、MCC中断的相关寄存器等参数。为了使2个MCC的5个TDM之间不相互影响,MCC的初始化需要对各个TDM进行相关参数和内部外部资源的分配,比如时钟、外部端口、数据缓存、参数缓存和中断队列等都需要对应正确。

2.2 MCC的收发处理设计

为了减少对系统资源的开销并且能够及时响应事件,MCC的收发处理需要解决在保证最大业务量的情况下提高CPU效率的问题。收发处理需要使用中断和任务,中断的优先级较高可以保证对线路数据的及时响应,在中断中只进行占用CPU资源较少的操作;任务分为MCC收发处理任务和收发数据处理任务,不同响应时间要求的任务需要配置为不同的优先级。

3 关键技术

MCC驱动程序的实现涉及MCC的初始化实现和MCC的收发处理实现等关键技术。

3.1 MCC的初始化实现

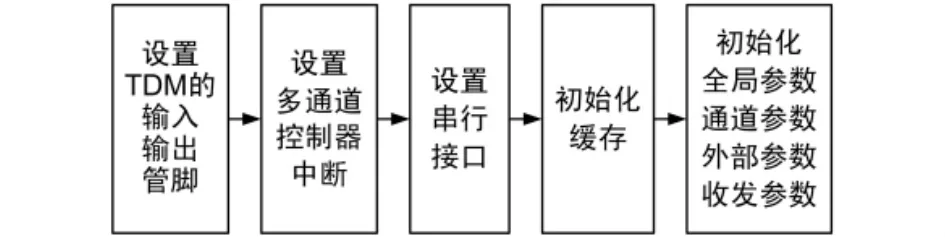

MCC的初始化流程如图2所示。

图2 MCC初始化流程

MCC初始化需要注意以下几点:

①SIRAM的个数设置必须是偶数,并且要在最后一个SIRAM设置last entry位。

②设置TxBD表、RxBD表需要注意的是:初始化时应将TxBD的状态位ready置“0”,数据长度为非零,RxBD的状态位empty置“1”,BD表的最后一个BD的状态位 wrap置“1”[4]。此外,由于数据是网际(Internet Protocol,IP)数据包,所以BD的个数不能分配太少,该设计的BD个数可以保证缓存2个IP长包。为了高效地利用有限的缓存资源,该设计采用动态分配内存的方式获得缓存资源。

③初始化MCC全局参数,需要注意最大接收帧长度要合适,每个MCC对应各自的中断队列而且中断队列的大小要合适。

④初始化MCC的通道参数,需要注意使能需要处理的各种中断,设置MCC通道的工作模式、循环冗余校验方式等。

3.2 MCC的收发处理实现

MCC的收发处理是通过中断处理程序、消息队列和任务共同配合完成的,具有处理及时和减轻CPU负担的优点。中断处理程序的设计需要简洁,尽可能减少操作;消息队列的长度需要设置合理;任务优先级的设置需要整体考虑,需要及时响应的任务设置为较高优先级[5]。

3.2.1 MCC的接收处理

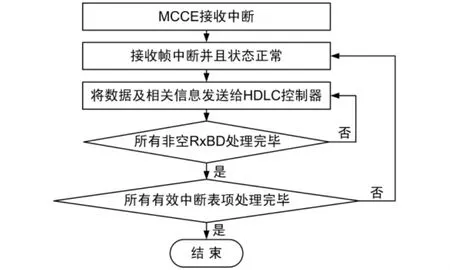

MCC的接收处理是当MCC的某个通道接收到数据后会设置MCC事件寄存器的接收中断比特位。中断处理程序将MCC的中断信息进行封装后发送到消息队列。任务从消息队列接收消息,当中断表项有效并且接收到完整的HDLC帧,对MCC的某个通道的所有有效的RxBD进行处理,将数据的地址和数据长度通过消息队列发送给HDLC控制器并设置RxBD的接收状态。当所有有效的中断表项都处理完成后,接收处理结束。MCC接收处理流程图如图3所示。

图3 MCC接收处理流程

3.2.2 MCC的发送处理

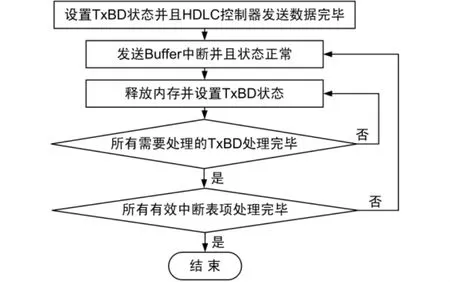

MCC的发送处理是当HDLC控制器需要发送数据时,将数据的地址和数据长度写入TxBD并设置发送状态,数据发送完成后会设置MCC事件寄存器的发送中断比特位。中断处理程序将MCC的中断信息进行封装后发送到消息队列。任务从消息队列接收消息,当中断表项有效并且发送完成1个Buffer的数据,那么对MCC的某个通道的所有有效的TxBD进行处理,释放内存并设置TxBD的发送地址。当所有有效的中断表项都处理完成后,发送处理结束。MCC发送处理流程图如图4所示。

图4 MCC发送处理流程

3.2.3 中断及任务配置

中断处理程序的设计尽可能减少占用CPU的操作,并且不能执行可能导致阻塞的操作,否则可能无法及时处理其他中断,影响其他模块通信甚至引起CPU重启。设计中的中断处理程序只进行中断信息读取与发送消息处理等占用CPU很少的操作。

任务优先级的设置需要满足的要求如下:占用CPU资源较少的任务可以设置较高的优先级;需要响应时间较短的任务设置为较高的优先级;高优先级的任务可以用来响应事件,对于事件的处理可以由低优先级的任务完成;不要设置过多的优先级,系统任务为0~50,驱动程序为51~99,用户的应用程序优先级不要太高,为100~250,以10级为间隔划分,为了系统的可扩充性,以20级为间隔划分[6]。设计中几乎不占用CPU资源同时又具有较高实时性要求的MCC收发处理任务设置为较高的优先级;占用CPU资源较多的数据内容处理任务设置为较低的优先级。

4 性能测试结果分析

2台设备通过1路E1接口互连,以计算机ping包为测试手段,对于32字节的短包和1 500 byte的长包分别进行1 800 s测试,丢包率为0。当通过5路E1接口互连,每一路都进行ping包操作,对于32 byte的短包和1 500 byte的长包分别进行1 800 s测试,丢包率<1‰。使用AX4000测试仪的以太网接口进行性能测试。2台设备通过1路E1接口互连,单路 E1设置双向 2 Mb的数据流量,对于64 byte的短包和1 500 byte的长包进行1 800 s测试,收发均正常而且丢包率为0。当通过5路E1接口互连,每一路E1设置双向1.95 Mb的数据流量,对于64 byte的短包和1 500 byte的长包进行1 800 s测试,收发均正常而且丢包率为0。由于数据通过CPU的以太网接口传送,所以证明在满足5路E1同时处理数据时,CPU有能力处理其他模块的业务。

通过测试,验证了利用2个MCC的5个TDM实现5路E1中继传输的可行性;采用中断处理程序、消息队列、任务共同配合完成的MCC收发处理,能够及时响应多路E1的处理请求,并且使CPU有能力处理其他业务请求;长时间的数据收发测试,验证了MCC驱动程序的稳定性和可靠性。

5 结束语

通过性能测试说明,利用高性能处理器MPC8280通过TDM和MCC之间的连接,并且采用中断、消息和任务相结合的高效调度处理方式实现5路E1中继传输是可行的,既节约了开发成本又缩短了开发周期。长时间的数据收发测试,验证了MCC驱动程序的性能、稳定性和可靠性。

[1]赵宇浩.基于MPC8280的网络通信平台的实现[J].电子技术,2010,26(6):58-59.

[2]王永强.基于MPC8280的嵌入式设备的通信接口驱动实现[D].西安:西安电子科技大学,2008:10-13.

[3]闫宇博,张 磊,彭来献.基于MPC8280多通道控制器驱动的研究与实现[J].微计算机信息,2010,76(23):177-179.

[4]王 炼,刘喜古,徐子平,等.基于MPC8270的MCC接口HDLC驱动程序开发[J].军事通信技术,2009,30(2):48-52.

[5]何福永.基于VxWorks驱动程序设计方法的研究与实现[D].长沙:国防科学技术大学,2008:6-9.

[6]张 杨,于银涛.VxWorks内核、设备驱动与BSP开发详解[M].北京:人民邮电出版社,2009:101-105.