一种低功耗Sigma-Delta调制器的设计*

王 亮 , 杨 骁 , 齐 骋 ,凌朝东 , 谢应辉

(1.华侨大学 信息科学与工程学院,福建 厦门361021;2.北京微电子技术研究所,北京100076)

随着超大规模集成电路的高速发展,便携式设备大量应用于日常生活中。便携式设备对电路的低功耗要求非常高。Sigma-Delta ADC与其他结构的ADC相比,具有低功耗和高精度的特点,已经广泛地应用于各种便携式无线通信系统中。本文设计了一种适用于短距离无线收发机中的低功耗Sigma-Delta调制器。

Sigma-Delta调制器在设计中有几个重要的参数:调制器的阶数、过采样率、拓扑结构和量化器位数[1]。这些参数的选择决定了调制器的性能和成本。一位量化器具有很好的线性度,但其调制器要实现高精度必然要提高调制器的阶数或者过采样率,这样必然增加了系统的功耗,而且高阶结构不利于系统的稳定[2]。本文的目标是设计一个应用于短距离无线接收发机中的低功耗调制器,其性能指标为:带宽 9.6 kHz、精度大于 12 bit。综合以上考虑,本文采用改进的单环二阶多位量化器低功耗结构,并采用低功耗全差分运算放大器,进一步降低了电路的功耗。

1 系统设计与仿真

本文采用改进后的单环二阶Sigma-Delta调制器,其结构如图1所示。该结构与传统结构相比,增加了一条从调制器输入端到第二级积分器输入端的信号通路。

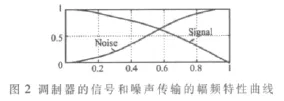

经过优化设计与仿真后,得到图中的系数分别为:a1=1,a2=1,b1=1,b2=2,c=0.5。调制器的信号传递函数(STF)和噪声传输函数(NTF)分别为:

本文调制器的信号和噪声传递函数的幅频特性曲线如图2所示。传统结构的STF为全通系统,而本文改进后结构的STF是低通系统,这种结构能有效地滤除输入信号中带宽外的噪声,降低了对后面数字抽取低通滤波器的设计要求[3]。此外,该结构还有以下优点:只有一条前馈通路,电路简单,减少额外的面积和功耗;降低了第一个积分器输出的幅度,也就降低对第一级OTA的输出摆幅的要求和系统功耗。

本文调制器采用多位量化器,在实际电路实现时,由于元器件的失配,多位量化器结构会带来非线性问题,使得调制器的输出信号产生较大的谐波[4]。针对这个问题,本设计采用了动态元器件匹配(DEM)技术中的数据权重平均法(DWA)来提高系统的线性度。DWA是通过 DAC开关的循环选择来实现的,该算法不但能够抑制调制器的谐波分量,还能对多位DAC误差进行一阶整形,并且实现电路简单[5-6]。

对图1所示的二阶2位调制器在Simulink中进行了建模,建模时考虑了多位量化器的非线性问题。仿真时采样频率为1.228 8 MHz,输入正弦信号频率为5 kHz,过采样率为 64,调制器带宽为9.6 kHz。当2 bit DAC不存在失配时,调制器输出信号功率谱如图3(a)所示,其信号噪声谐波失真比(SNDR)为 84.7 dB,并且频谱中没有谐波分量;当DAC中各个采样电容之间存在1%的失配时,调制器的输出功率谱如图3(b)所示,从图中可以看出,此时频谱中存在较大的谐波分量,调制器的 SNDR降至50.9 dB,严重影响了整个系统的性能;采用DWA算法电路后,同样在各个采样电容之间存在1%的失配情况下,输出功率谱如图3(c)所示,与未使用DWA算法相比,其低频段的噪声基底小得多,并且没有明显的谐波分量,SNDR为80.7 dB。这表明,本设计所采用的DWA算法能够较好地抑制多位DAC非线性对调制器性能的影响。

2 电路设计

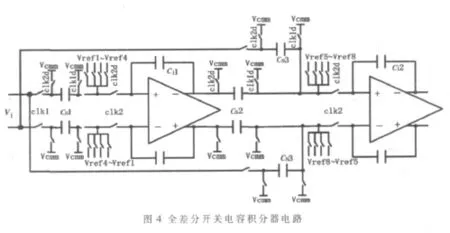

2.1 全差分开关电容积分器

A/D转换器是模数混合系统,容易受时钟馈通、衬底、电源、开关电荷注入噪声的影响,因此本设计电路采用全差分开关电容积分器来实现。全差分结构能有效地抑制共模噪声,而且具有较大的输出摆幅。本文全差分开关电容积分器电路如图4所示,电路由两相不交叠时钟来控制。Clk1为采样时钟,Clk2为积分时钟,Clk1d和Clk2d分别为Clk1和Clk2的延迟时钟,使用这样的时钟控制能够有效地降低电荷注入效应[7]。

图3 Simulink行为级仿真结果

对于全差分结构的开关电容积分器,其热噪声的主要来源是开关,由开关引入的调制器信号带宽内的热噪声功率为2 KT/CsM,其中Cs为采样电容,M为调制器的过采样率[8]。调制器对第一级以后的热噪声是有整形效果的,抑制了调制器信号带宽内的热噪声,所以只需要考虑第一级积分器电路引入的热噪声,为了降低热噪声对系统的影响,第一级积分器一般选择较大的采样电容,但是大的采样电容又会降低电路的速度,增加功耗。本文根据调制器的各项性能指标折中考虑,经仿真选取Cs1=6 pF。

2.2 运算跨导放大器

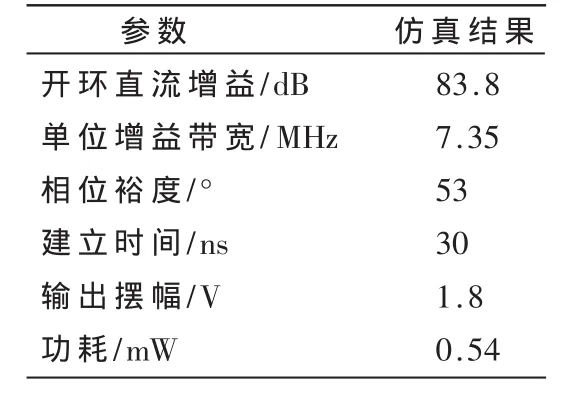

在开关电容Sigma-Delta调制器中,为了使运算放大器的有限增益和有限带宽不明显地降低调制器的性能,一般要求运放的开环增益不小于 60 dB,单位增益带宽为调制器采样频率的4~6倍。本调制器的采样时钟频率为1.228 8 MHz,为了满足上述要求,OTA的单位增益带宽需要大于5 MHz。

本文所设计的运算跨导放大器OTA(Operational Transconductance Amplifier)电路如图 5所示,采用了两级运放的结构,第一级采用折叠式共源共栅放大器实现高增益;第二级采用AB类推挽共源放大器实现大的电容负载驱动能力。AB类输出级使得在实现与A类输出级相同第一非主极点的情况下,可以节省大约一半的输出电流[9],降低了电路的功耗。电路采用全差分结构,其共 模 反 馈 电 路 由 M17、M18、M19、R1、R2、C5 和 C6 组成。第一级运放的各项性能指标如表1所示,该结果满足系统对运放的要求。系统对第二级OTA的要求要低于第一级的要求,因此可以采用第一级的结构,并等比例缩小管子参数后得到第二级OTA,从而能够降低系统的功耗。

表1 OTA的性能

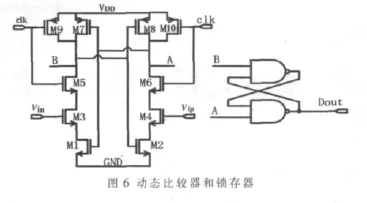

2.3 量化器

量化器采用一个2 bit的Flash A/D转换器实现,每位都是由一个比较器和一个锁存器实现,出于速度和功耗方面的考虑,比较器采用动态CMOS结构,电路如图6所示。

该比较器的工作状态由时钟clk端控制,工作过程可以分为复位期(reset interval)和再生期(regeneration interval)。clk为低电平时,比较器工作在复位模式,电路处于预充值状态,使得锁存器的A和B输入端变为高电平,因此SR锁存器的输出保持不变。clk为高电平时,预充值管M9、M10截止,电路进入比较状态,当Vip>Vin时,流过M4的电流大于M3的电流,正反馈使得A点电位迅速降低,B点电位升高,Dout输出高电平。

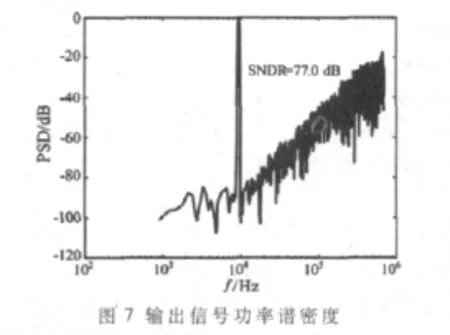

3 调制器整体仿真结果

整个Sigma-Delta调制器电路采用TSMC 0.18 μm工艺实现,并用 Cadence/Spectre对电路进行仿真验证。仿真时,输入信号是频率为9.3 kHz、幅度为250 mV的正弦信号,调制器的采样频率为1.228 8 MHz,过采样率为64。对调制器输出数据采样4 096点后,将数据导入Matlab,利用快速傅里叶变换,得到输出信号频谱图如图7所示,其输出信号SNDR为77.0 dB,达到了整个收发机系统对调制器的要求。

本文基于3.3 V TSMC 0.18 μm CMOS工艺实现了一种低功耗低通Sigma-Delta调制器,其工作频率为1.228 8 MHz,过采样率为 64,信号带宽为 9.6 kHz。调制器采用了二阶2 bit低功耗架构,并采用两级AB类运放来降低功耗。仿真结果表明,调制器的SNDR为 77.0 dB,达到了收发机系统对调制器性能的要求,并且其功耗仅为1.18 mW,具有较好的低功耗特性。

[1]RABII S,WOOLEYB A.The design of low-voltage,Lowpower sigma-delta modulators[M].Boston:Kluwer Academic Publishers,1999.

[2]BRANDTB P.Oversampled analog-to-digital conversion[D].Stanford:Stanford University,1991.

[3]SCHREIER R,TEMES G C.Understanding delta-sigma data converters[M].New York:IEEE Press,2005.

[4]Cheng Yongjie.Multibit delta-sigma modulator with two-step quantization and segmented DAC[J].IEEE Transactions on Circuits and System,2006,53(9):848-852.

[5]CINI D, SAMORI C,LACAITA A L.Double-Index averaging:a novel techinque for dynamic element matching in sigma-delta A/D converters[J].IEEE Transactions on Circuits and Systems II:Analog and Digital Signal Processing,1999,46(4):353-358.

[6]欧伟,吴晓波.高精度低功耗多位量化Σ-Δ调制器的设计[J].机电工程,2008,25(12):28-30.

[7]韩俊,王卫东.基于开关电容技术的Σ-Δ调制器的设计[J].微电子学,2011,41(3):354-358.

[8]NGUYEN V T,LOUMEAU P,NAVINER J F.VHDL-AMS behavioral modeling and simulation of high-pass delta-sigma modulator[C].Proceedings of the 2005 IEEE International Behavioral Modeling and Simulation Workshop.San Jose,CA,United States:Institute of Electrical and Electronics En gineers Computer Society, 2005:106-111.

[9]YAVARI M,SHOAEI O,AFZALI K A.A very low-voltage,low-power and high resolution sigma-delta modulator for digital audio in 0.25-μm CMOS[C].ISCAS,2003:1045-1018.