RFID读写器的电路设计的实现及其测试

艾尔肯·艾则孜

(乌鲁木齐职业大学,新疆 乌鲁木齐 830002)

射频识别技术RFID(Radio Frequency identification)是一项正处在快速发展中的技术,其通过射频信号,进行非接触式的双向数据通信,实现物与物之间的自动识别,具有非常广阔的应用前景。

1 系统整体硬件图

图1为整个系统的硬件结构框图。结构中包括W77E58主控芯片,FPGA的编解码芯片以及其他必需的接口。阅读器以W77E58为处理核心,其外部接口主要为LED显示、键盘、PC接口以及和FPGA的控制链接。FPGA的主要任务,是对数据进行编解码以及CRC的计算和校验。FPGA选择的是Xilinx XC2S300E。

图1 读写器系统结构图

XC2S200E芯片拥有20万个逻辑门,4 320个逻辑单元、480个LUT、30 kB分布式RAM、216 kB块状RAM、12个专用乘法器、4个DCM、97个可用I/O引脚数,采用144个引脚的PQG封装,性能级别为4。

通常使用其内部的DCM,系统的工作频率可以达到340MHz。

2 CRC电路设计

2.1 初设计

在高频和超高频射频识别系统中,循环冗余校验(CRC)电路,一般采用线性反馈移位寄存器(LFSR),本文以CRC-5举例说明实现过程,其生成多项式为

g(x)=x5+x3+1,

即控制向量

g(g 0,g 1,g 2,g 3,g 4),

其中,

g 0、g 2和g 4为“1”,其余为“0”。

结合上面的分析,可以得知当gi 为“1”时,对应的与门为打开状态,即相当于短路,对应的异或门将进行正常工作,执行模2除法;当gi 为“0”时,则其对应的与门处于截止状态,相应的异或门相当于处于短路状态。

工作过程如下:

(1)先将移位寄存器置000000H;

(2)将数据流高位的前5位输入寄存器,数据流的高5位移进寄存器不会发生改变,因为寄存器初始值为0;

(3)数据流继续移位寄存器时,第5级移位寄存器移出值若为“0”时,则直接右移一位;若为“1”则进行模2运算后右移一位;

(4)当数据流全部移入寄存器时,还需要另外移进5个连续“0”之后,才会得到CRC的结果。

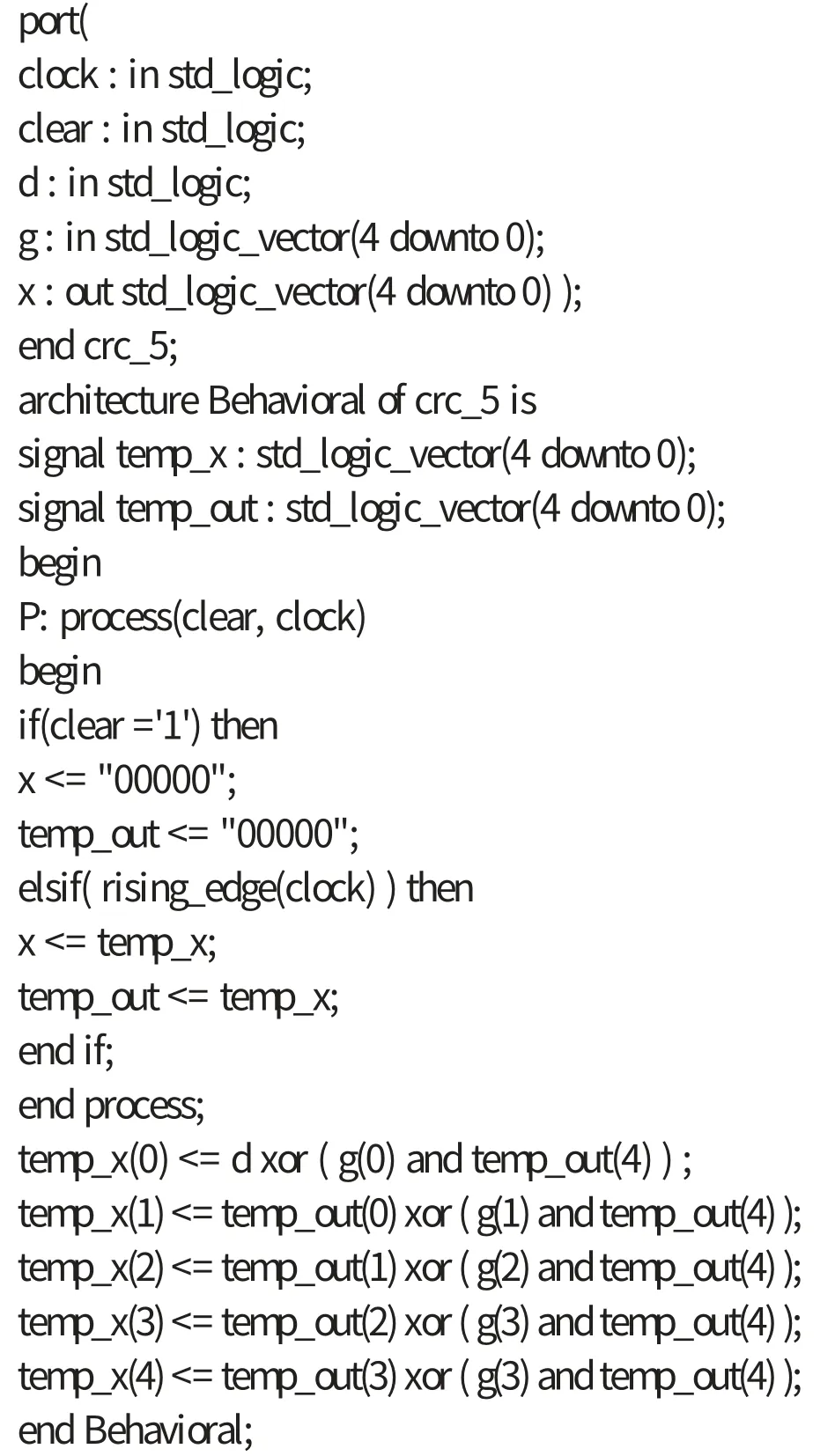

下面是在Xilinx开发环境中实现CRC-5的VHDL代码。

初设计的最大的缺点,就是效率低,因为数据流移进寄存器后还需要继续输入5个“0”,增加了5个时钟延迟。

2.2 改进后的设计

通过对CRC运算过程做一些递归变换,找到一种消除时钟间隔的电路设计方法。与线性反馈移位寄存器不同,将改进前电路结构上左边的异或门移到了右边,这样就会减少CRC码的计算时间。

改进型的线性反馈移位寄存器CRC电路中,数据流先进行模2除法运算,并且数据流的高5位不必预先送入移位寄存器,和改进前的CRC电路相比,改进后的电路CRC码的计算提前了5个时钟周期,解决了数据结束后另外需要等待的5个时钟周期。

图2(b)是改进后线性反馈移位寄存器实现CRC,下面是在Xilinx开发环境中实现CRC-5的VHDL代码。

3 射频收发模块(RF)电路设计和分析

射频模块的性能直接影响整个RFID系统的性能。由图2可见,本设计的射频模块主要有锁相环电路、功率放大电路设计以及双通道检波接收电路。

图2 RF硬件结构图

3.1 锁相环电路

锁相环电路的主要作用,是产生读写器调制所要的载波信号,读写器的硬件性能,决定了信号的可靠性。本文中采用的锁相环频率合成器为ADF4360-1,是一款完全集成式整数N分频合成器和电压控制振荡器,其设计中心频率2 250 MHz,输出频率范围为2 050~2 450MHz,满足读写器的工作频点多的要求。

3.2 功率放大电路

结合本文要求,这里选择的功放为PF01411B,可以减少整个电路布板面积。同时功放PF01411B转换效率高,通过控制自动增益控制引脚可调节输出功率的大小。因为功放PF01411B的三阶截取点为0 dBm,为了避免输出信号的失真,要求输入信号强度应小于0 dBm。

3.3 双通道检波接收电路

一般远场耦合的RFID接收机,都使用零中频混频结构,见图3(a)。通常环形器的隔离度为–25~30 dB,如果发射电路连续载波信号为30 dBm,则依然有0 dBm左右的波信号泄露,这样会提高接收通道的功率。一般的混频器的输入信号功率上限在-5~-10 dBm范围内,即低于读写器发射泄露的载波功率,所以零中混频结构中需要在混频器前加一个衰减器,来降低读写器的接收灵敏度。

另外,混频器电路结构相对俞零中频检波电路复杂,成本昂贵。

图3 双通道检波接收电路

零中频检波电路见图3(b)。零中频率检波电路的优点,在于其利用肖特基二极管来直接检波调整信号,相比混频电路结构更简单,成本相应降低。另外肖特基二极管,可以承受的射频信号的输入功率很大,同时接收灵敏度由肖特基二极管的检波灵敏度决定。

又因为两路检波电路是正交信号,只跟读写器天线和标签之间的距离有关,所以两路信号不可能同时为0,这就保证了主芯片总能收到有效标签应答信号。

4 系统测试

系统先初始化,然后判断在读写器的范围内是否有标签。如果有标签,阅读器将发送信息给标签,将会得到标签应答,此时如果有标签冲突,则通过新防碰撞算法来处理,冲突解决之后,继续判断标签的信息,最后进行读写器和标签的通信。RFID读写器的测试结果如下:

识别速率:一个标签识别时间为1~5ms,多标签识别时间取决数量多少;

识别效率:单标签接近99%;多标签效率,取决于标签数量多少;

输出功率最大:32 dBm;

识别距离可达:30~60m。

5 结束语

射射频识别技术RFID实现物与物之间的自动识别,具有非常广阔的应用前景。作为一项正处在快速发展中的技术,其电路设计方面还有许多可以提高的方面。本文研究了目前RFID读写器中电路设计中的传统设计思路,重点针对其循环冗余校验(CRC)电路和射频收发模块(RF)电路设计中的不足进行了分析,提出了新的设计思路,并进行了实现,测试结果表明,改进后的RFID读写器的识别效果良好。

[1]陈 香.RFID防碰撞技术的研究[J].金卡工程,2005,(9):34-37.

[2]李锦涛.射频识别(RFID)技术及其应用[J].信息技术快报,2004,19(11):1-10.

[3]王海峰,王敬超,张 春,等.一种超高频RFID读写器设计[J].微计算机信息,2008,3(2):233-235.

[4]孙枫叶,张科峰,刘冬生.高频RFID标签曼彻斯特编码电路的设计[J].电子技术应用,2006,(10):108-110.

[5]孙晓云.接口与通信技术原理与应用[M].北京:中国电力出版社,2007.