基于游标法的时统IRIG-B(DC)码的数字传输技术

王志林,童 斌,王永岭

(91245部队,辽宁 葫芦岛125001)

时统的主要内容是通过对时刻相对准确的传递,使得在一个区域内形成一个高精度的时间同步体系。体系内各设备之间的对时和同步通过时间码信号进行统一,常用的时间码有IRIG-B(AC)码和IRIG-B(DC)码两种。AC码为1 kHz/s调幅模拟信号,DC码为直流方波信号。AC码传输距离远,但同步精度低,当两设备之间用实缆相连时,时间同步误差小于10 μs;当两设备不在同一个地点,AC码在通信信道传输过程中需经过A/D、D/A变换,信号在传输过程中会引起波形失真,对AC码的解调有影响,另外加上传输时延,设备间的对时同步误差会进一步加大。DC码同步精度相对较高,实缆直连时间同步误差小于 0.2 μs,但传输距离短(200 m);在通信信道传输过程中将DC码通过游标法将代码变换成标准的低速数字接口后,不仅对时同步精度高,而且信道利用率低,接口通用性强。随着电子技术的发展,EDA已经成为现代电子设计领域的基本手段,本文主要阐述利用游标法将DC码进行代码变换的原理,给出其FPGA的实现方法,同时就变换过程中的信号畸变对同步精度的影响进行分析,阐明时钟插入和封锁的作用及其实现方法。

1 时统DC码数字传输的原理

1.1 游标法代码变换原理

数据信号的数字传输按DTE数据信号时钟与PCM信道时钟是否同步可分为同步传输和异步传输,异步数据传输方式又可分为代码变换和脉冲塞入方式两类,代码变换方式又分为取样法、游标法等。

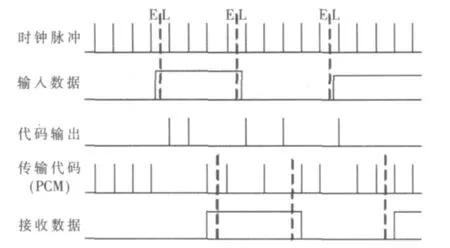

游标法是将数据信号的“1”和“0”的变化时刻用 3个比特来编码。第一比特 a表示“1”和“0”变化点的开始,a=1表示有变化点;第二比特b(也可以规定几个比特)表示变化点出现在时间脉冲间隔的哪一个规定位置:如b为1 bit时,将时钟间隔平分为前后两个时区,分别记为E和L,如果变换点处于 E区域,则b=1;若在L区域,则 b=0;第三个比特 c便是变换点的方向:如从“1”变到“0”,则 c=1;从“0”变到“1”,则 c=0。 另外,当数据中没有变化点时,向PCM信道连续发送“1”信号,可以限制连续“0”码。输出代码中,最初的“0”表示数据信号变换点的开始,图1是游标法的代码变换过程。由图可见,代码出现的位置在PCM帧结构上的位置是不固定的,它随输入数据信号的变化点位置而移动,所以称为游标法[1]。

1.2 信号畸变误差分析

IRIG-B(DC)码为TTL接口,准时点为上升沿,GB11014-90标准接口,DC码由周期为 10 ms,脉冲宽度为 8 ms、5 ms、2 ms的脉冲信号组合而成。若以2 ms脉冲为最小周期,从数字传输的角度可将DC码看成是速率是0.5 kHz/s低速率的数据信号。由于DC码是靠脉冲前沿来产生同步信号的,因此信号畸变误差要求控制在一定的范围之内。信号畸变误差主要由代码变换畸变、通信信道抖动和收发晶振频率误差三方面的原因引起。

图1 游标法代码变化示意图

由游标法的工作原理可知,取代码变换后的数据传输速率为 16 kHz/s时,一个变化点的b比特数为7 bit,那么 b比特形成时钟频率应为 27×16 kHz/s=2 048 kHz/s,信号在每个变化点的最大畸变约为0.49 μs;通信传输信道的抖动为1.4 μs;10 MHz/s的恒温晶体振荡器的频率准确度为10-8、稳定度为10-9,可通过封锁或插入时钟的方法来消除晶振引起的累积误差,误差最大为0.5 μs,因此总的信号畸变误差小于 3 μs。

2 FPGA设计实现方法

2.1 系统的组成与功能

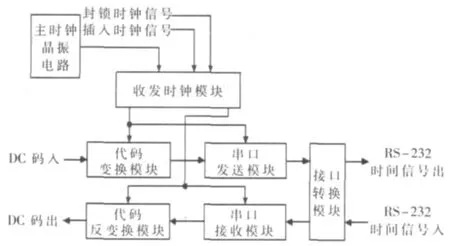

系统主要由主时钟晶振电路、收发时钟、代码变换与反变换、串口发送与接收、接口电平转换等模块组成。其中收发时钟模块产生系统所需的各种收发时钟信号;代码变换模块完成DC码到数据信号的转换;串口发送模块将数据信号变成RS-232串行接口时间信号;反之,串口接收模块将接收的RS-232串行接口时间信号变成数据信号,代码反变换模块将数据信号恢复成DC码;电平转换电路完成TTL电平与RS-232接口电平之间的转换,系统组成如图2所示。

图2 系统的组成结构

2.2 系统的设计平台

本系统采用Xillinx公司推出的FPGA/CPLD集成开发工具ISE Design Suite,以Verilog HDL语言进行设计输入,并用ISE集成开发环境中的Simulator进行仿真。FPGA采用Xillinx公司中低端平台推出的Spartan 3E系列中的XC3S1600E芯片,它的系统门数为150万,Slice数目为14 752个,分布式RAM容量为23 KB,块RAM容量为 648 KB,专用乘法器数为 36个,DCM数目为 8个,最大可用 I/O数为376个,最大差分I/O数为156个[2];RS-232接口电平转换芯片采用Maxim公司的MAX2322芯片;晶振采用长沙太阳人电子有限公司的高精密的恒温晶体振荡器(OCXO)。

系统采用自顶向下、层次化和模块化的设计模式,在确定电路功能后,在ISE开发环境中用Verilog HDL语言进行设计输入,并用ISE Simulator进行功能仿真。通过综合工具将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,综合仿真正确后,通过布局布线等实现功能将综合生成的逻辑网表配置到具体的FPGA芯片中,最后将编程数据下载到FPGA芯片中。

2.3 代码变换功能的设计

代码变换模块用16 kHz/s的clk_1时钟脉冲对DC码进行采样,并将连续采样的信息用两个D触发器进行存储。比较两采样值,如值不一样,则说明是DC码电平变换点,通过异或非门产生a比特,通过c比特产生器得到c比特;同时用计数器对上个clk_1时钟脉冲清零后的128进制计数器对2 048 kHz/s的clk_0时钟进行计数,用DC码的低电平将电平变换位置的精确计数值进行锁存,形成7 bit的b比特。此后通过9进制计数器将高电平信号进行封锁,将a、b、c比特值依次插入输出数据中,然后继续输出高电平信号。

2.4 代码反变换的实现流程

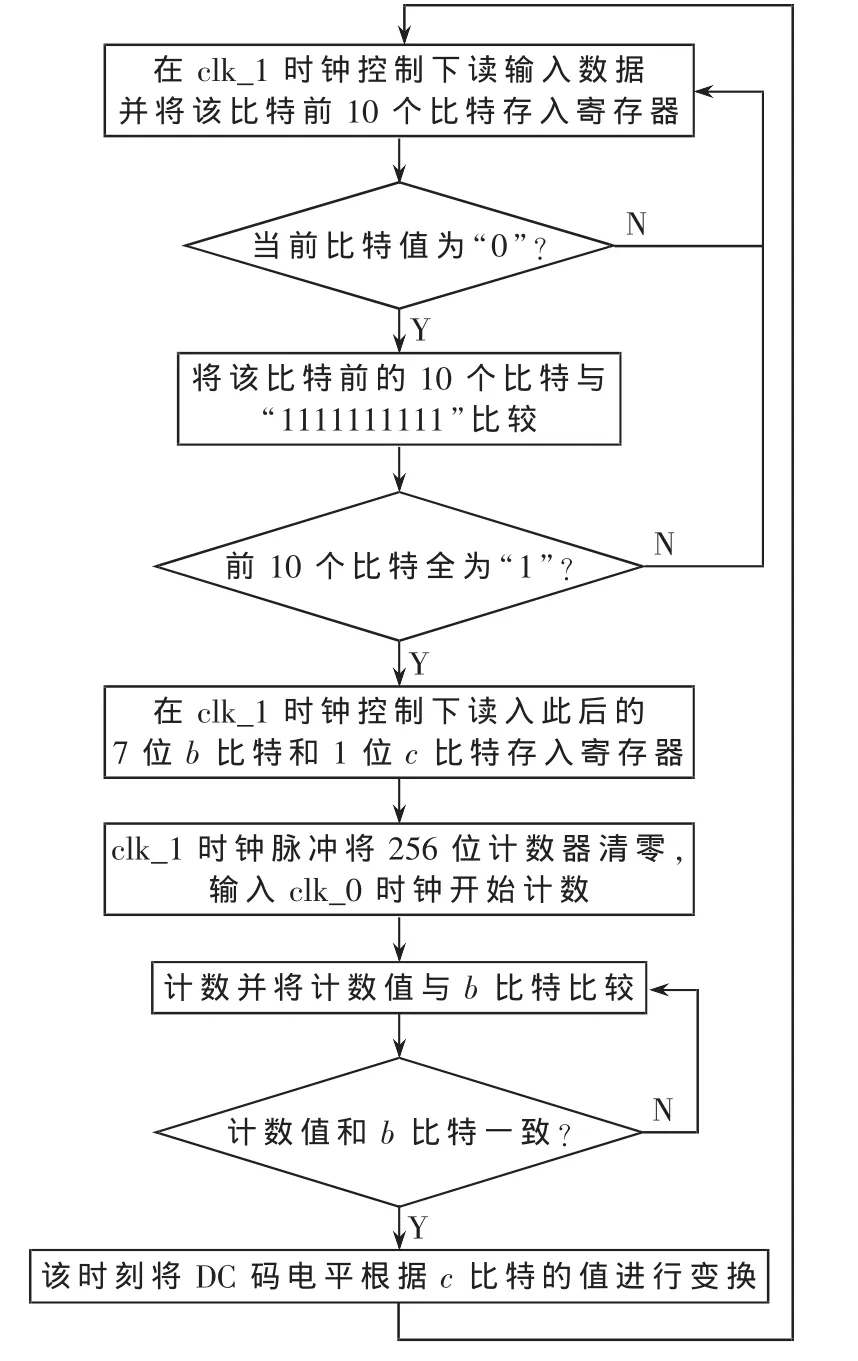

在代码反变换过程中,需要判别所接收数据中变换点的起始位置。a比特为“0”值时,表示数据电平发生变化,由于b比特中也有“0”值的比特,为了正确判别a比特,在代码变换过程中将抽样速率定为16 kHz/s,DC码可看成是速率为0.5 kHz的数据,每两个变化点之间至少有 32个抽样数据,去掉 a、b、c比特共 9个,其他 23个比特全为“1”,这样当某比特值为“0”且其前面的9个比特值全为“1”时,该比特就是a比特,否则就是b比特中的“0”比特。a比特确定后,将后面的b比特与2 048 kHz/s速率的计数器中的计数值进行比较,在两值相等时刻,根据c比特的值将DC码数据电平进行变换,c比特为“0”时,由高变为低,c比特为“1”时,由低变为高。代码反变换的实现流程如图3所示。

时钟模块、串口发送模块和串口接收模块的功能比较常见,其设计参见参考文献[2]第13.2节。

3 时钟的插入和封锁

图3 代码反变换的实现流程图

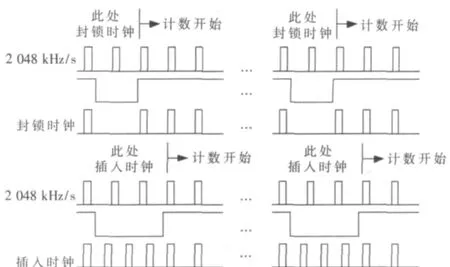

接收方采用由恒温晶体振荡器产生时钟。由于收发双方采用独立的时钟,因此虽然恒温晶体振荡器具有较高的频率准确度和稳定度,且误差较小,但时间较长时会引起误差累积,使得接收的时间信号产生漂移,因此系统采用时钟插和封锁的方法消除误差累积。首先测出接收方与标准时钟或收发双方直连时的同步1C/S信号的时延值,隔一段较长时间再测一次时延值,根据两次测得的时延差计算单位时间内的漂移值;将该值与2 048 kHz/s时钟的周期0.49 μs相比较,计算出时钟插入或封锁的间隔,并存入寄存器;根据超前或滞后状态,通过计数器对clk_0时钟计数,在计算的间隔对时钟进行插入或封锁,时钟插入和封锁如图4所示。

图4 时钟插入和封锁示意图

本文提出的方法直接在输入前对clk_0时钟进行处理,不会对上面的电路设计产生影响,上述设计无需任何改动,同步误差在一个时钟周期0.49 μs内。

游标法的DC码数字传输原理简单,采用FPGA技术实现方便快捷,整个时统传递全程数字化,对时同步精度高,RS-232接口通用性强,该技术在各个领域的实时测量系统中具有广泛的应用前景。

[1]倪维桢.数据通信原理[M].北京:中国人民大学出版社,2000.

[2]云创工作室.Verilog HDL程序设计与实践[M].北京:人民邮电出版社,2009.

——游标卡尺、螺旋测微器的应用和拓展