基于CPLD的ГОСТ18977总线收发系统设计与实现

王 瑞,芮国胜,张 洋

(海军航空工程学院 电子信息工程系,山东 烟台 264001)

在现代俄制飞机上,普遍采用符合俄罗斯ГОСТ18977总线的传送方式进行数字信息的传送和交换。该数据总线标准类似于美国航空无线电公司 (ARINC)制定的ARINC429传输标准。二者数据格式及电气特性一致,其不同之处在于俄式ГОСТ18977标准总线传输速率有12 kb/s、48 kb/s、100 kb/s和 250 kb/s 4 种, 而 ARINC429标准总线传输速率只有12.5 kb/s和100 kb/s两种[1]。目前,由于国内尚无专用的 ГОСТ18977总线芯片,大多ГОСТ18977总线收发设备通常采用 ARINC429专用芯片来实现[2]。而ARINC429芯片无法完全兼容ГОСТ18977的 4种总线传输速率,参考文献[3-4]通过设置芯片控制字的方法,对外部时钟进行分频以达到速率匹配的目的。这种硬件分频的方法只能兼容某一固定传输速率,无法满足不同传输速率设备之间的通信要求。本文设计并实现了一种基于CPLD的ГОСТ18977总线收发系统。该收发系统利用CPLD进行软件分频,可兼容不同的总线传输速率;并通过CPLD实现系统的逻辑设计与收发控制,能够实时完成总线数据的发送、接收、显示和存储功能。

1 系统总体设计

在系统设计上,采用模块化结构对系统的功能进行划分。主要功能包括对从其他机载设备到收发系统的信息的输入、显示、存储,以及从收发系统到其他机载设备的信息的输出等。根据其功能可将系统分为中央控制模块、信息输入/输出模块、带键盘和数码管的显控模块以及电源模块等,系统整体结构如图1所示。

系统采用对STC89C58RD+芯片进行指令编程的办法,并将编写的指令信息存储到STC89C58RD+芯片的指令存储器中。输入数据时,通过写入、存储指令直接存储到STC89C58RD+芯片的数据存储器中;输出数据时,直接通过读出等相关指令从存储器中提取相关数据并传送至CPLD,通过CPLD完成信息时序控制、并串转换,再输出至输入/输出模块进行信号的差分编码和信息波形变换;读取其他机载设备的数据时,通过输入/输出模块完成信号调理、差分编码的逆变换,同时由CPLD完成时序控制和串/并转换,再送至单片机,最后由单片机发出显示指令,通过显控模块完成信息的显示。RAM存储器用于保存自相邻模块获得的信息,并根据中央控制模块的指令将信息传输到相邻模块。ROM存储器用于长期保存自RAM存储器获得的信息,并根据中央控制模块的指令将信息传输到相邻模块。

2 硬件设计

2.1 中央控制模块

中央控制模块是该收发系统的信息控制和处理中心,它直接参与和控制各部分电路的正常工作以及各种信息的处理、传输和显示,起着整个系统信息处理与控制中心的作用。它包括中央处理器STC89C58RD+和可编程逻辑器件CPLD。

CPLD采用EPM7128SQI100-10可编程逻辑器件[5]。中央处理器通过其外部总线,与可编程逻辑阵列构成的接口电路相联系,经过CPLD对地址、数据、总线等信息地址锁存与缓冲等处理后,完成各种信息的键盘输入、数码管显示和存储控制等功能。

RAM存储器、ROM存储器矩阵用于存储256个24 bit字,采用STC89C58RD+内部集成的EEPROM。利用ISP/IAP技术,将内部DATA Flash当EEPROM使用。在进行256个24 bit存储中,采用4个EEPROM扇区,每个扇区512 B。该方案简化了系统的电路设计,方便使用[6]。

另外,系统采用12 MHz、24 MHz振荡器分别作为单片机和CPLD的时钟,CPLD将24 MHz时钟经分频后产生96 kHz的时钟作为32 bit串行码发送和接收的工作时钟。CPLD的分频时钟是通过编程的方式实现的,可根据传输速率的不同,灵活调整CPLD的工作时钟。

2.2 输入/输出模块

输入/输出模块主要用于与其他机载设备的信息交换,完成信息的32 bit串行码的差分编码、差分译码、波形变换等功能。

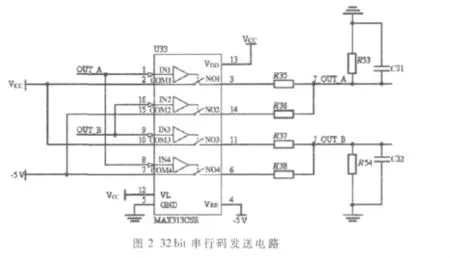

在发送32 bit串行码时,由STC89C58RD+准备数据,并通过总线通信的方式将数据传递给CPLD;由CPLD控制输入模块将其转换为串行码,并控制发送的时序,码元宽度为 20 μs,占空比为 50%[7]。输入模块的核心是双极性码形成模块,该模块主要由MAX313模拟开关及由CPLD组合逻辑电路组成的译码电路两部分构成,其主要作用是产生所需的32 bit串行双极性码。电路图如图2所示。

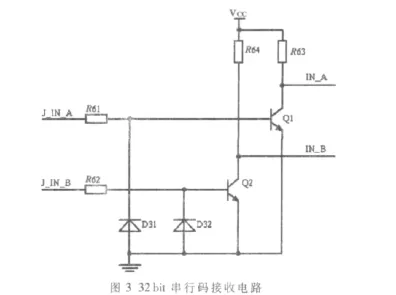

在接收32 bit串行码时,首先使信号J-INA、J-INB分别通过一个二极管和一个三极管,此过程中信号被削去负电平且被反向;再经过一个CPLD内部的“与门”,得到的信号就是从串行码信息中提取的时钟信号。由于每个上升沿正好在时钟周期的中间,所以此信号不仅可以送往单片机进行计数,而且可以作为CPLD的数据的移位脉冲。另外,信号还经过一个CPLD内部触发器,形成需要的单极性归零码信号,完成信号的接收。当完成32 bit串行码接收后,由CPLD送至单片机,经单片机控制显示控制模块进行信息的显示。编码接收电路如图3所示。

2.3 显示控制模块

显示控制模块由8 bit数码管、28个按键和 4个指示灯构成。其中,8 bit数码管、28个按键的驱动和控制主要由芯片CH451完成。8 bit数码管用于信息的显示,高6位为数据信息,低2位为地址信息;28个按键主要用于16进制信息的输入、设备状态的设定、输入按键、读取按键功能;4个指示灯分别对应清除、输入结束、写入、存储信息指示。

3 系统软件设计

系统软件部分由主程序、发送子程序和接收子程序构成。主程序负责对数据接收、发送、存储和显示的控制,同时通过奇偶校验对接收到的数据实现检错功能。发送子程序和接收子程序以对中断响应的处理为核心,通过主程序对中断的调度来实现数据接收和发送的功能。

3.1 数据接收

在接收状态下,主程序不间断地检测接收数据线的状态,当出现连续(4个码元周期)的高电平时,开始检测同步码;确认收到同步码后,准备在4个码元周期后接收32 bit的数据码,否则继续检测接收数据线的状态;间隔4个码元周期后,主程序产生接收中断信号,开始执行接收子程序,接收子程序将32 bit的数据存入缓冲区并完成串/并转换,以便主程序的显控模块调用;间隔一个字周期后,退出接收子程序中断,再次循环以上过程。其流程图如图4所示。

3.2 数据发送

在发送状态下,主程序不间断地扫描键盘的状态。当有按键按下时,数码管会显示相应的标示;当检测有发送的请求信号时,主程序产生发送中断信号,开始执行发送子程序;发送子程序将键盘按下的数据信息存入缓冲区,在完成并/串转换后,将 32 bit的数据码送入发送数据线上;在一个字周期后,退出发送子程序中断;间隔4个码元周期后,重新开启发送子程序,将32 bit的同步码送入发送数据线上,完成对同步码的发送过程;在一个字周期后,退出发送子程序中断,再次循环以上过程。其流程图如图5所示。

图4 数据接收流程图

图5 数据发送流程图

3.3 数据同步与纠错

由接收数据和发送数据的过程可知,精确地定位数据码和同步码间隔的4个码元周期的高电平,而不产生错位对于同步接收数据非常重要。CPLD的时钟频率为24 MHz,将其分频后的100 kHz作为串行码的工作时钟,分频后的200 kHz作为同步检测时钟。在同步检测时钟下,检测出16个高电平的数据信号,即为数据信号的同步头。同时,为避免直流电平对同步头检测的影响,还应排除大于4个码元周期的伪同步头。

为了提高数据接收的可靠性,本系统在进行数据通信中,通过奇偶检验来实现检错功能,将数据通信的误码率降到最小。数据码的第32位为奇偶检验位,在发送时,若前31位中 1的个数为偶数,则检验位为 0,否则为1;在接收时,按照同样的规则进行判定,若校验一致,则表明正确接收,否则通知发送端重新发送。其流程图如图6所示。

图6 检错实现过程示意图

4 测试结果

系统的测试包括硬件测试和软件测试。硬件测试主要是在完成PCB板的焊接后,对板上的元器件进行逐一测试,保证与原理图一致;并对焊接情况进行检查,防止出现虚焊、漏焊的情况,进而确保系统接口与其他机载设备电气特性的一致性。

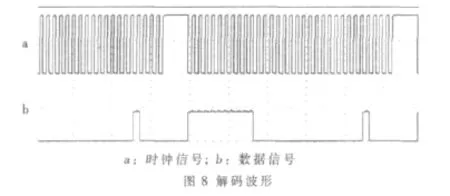

软件测试采用各模块联调的方式进行。首先用示波器测试了发送数据的波形接收后的解码波形,分别如图7和图8所示。另外,还测试了以下功能:(1)接收自其他机载设备的数据,并完成显示功能;(2)将键盘输入的数据发送至其他机载设备;(3)将发送或接收的数据存储到RAM存储器或ROM存储器,并完成显示功能;(4)将数据从存储器中读出,并完成显示功能。上述各功能在实验室及室外环境下均做了100次以上的测试。测试结果表明,系统均能正确地完成相应操作。

该收发系统充分利用CPLD硬件可编程性、高度集成性等特点,通过CPLD实现系统的逻辑设计与收发控制,能够实时完成总线数据的发送、接收、显示和存储功能。与采用专用芯片的实现方式相比,该系统可兼容不同的总线传输速率,且器件的成本较低,具有较强的推广价值。

[1]田城,王勇,何雅静,等.ГОСТ18977-79航空总线仿真系统的设计与实现[J].计算机应用与软件,2011,28(01):300-303.

[2]刘迎欢,罗志强.ARINC429协议和与之对应的俄罗斯标准的比较[J].航空电子技术,2002,33(1):11-15.

[3]邸亚洲,李富荣,于建立,等.基于 HS3282芯片实现ГОСТ18977总线数据传输方法[J].计算机测量与控制,2007,26(1):47-49.

[4]黄润龙.基于 ARINC429协议芯片实现俄式 ГОСТ18977-79 协议通 信 设 计[J].电 讯技术,2005,02(02):62-68.

[5]张立,刘昆.基于 FPGA的采样与控制系统设计[J].电子测量与仪器学报,2008,22(z2):520-523.

[6]吴继华,王诚.Altera FPGA/CPLD 设计[M].北京:人民邮电出版社,2011.

[7]杨军锋,谢聂.多通道串行双极性数字发送电路设计[J].测控技术,2003,22(1):67-69.