确定性测试矢量生成的低功耗设计

李 鹏,颜学龙,孙 元

(桂林电子科技大学电子工程与自动化学院,广西桂林541004)

随着深亚微米工艺技术的发展,集成电路的工艺尺寸日益减少,电路节点的物理可访问性正逐步削弱以至于消失,这使得电路和芯片的测试变得尤为困难,以往依赖自动测试仪器ATE(Automated Test Equipment)方法,因其传输带宽和存储容量的制约,已经增加了大量测试成本。内建自测试BIST(Built-in Self Test)摆脱了对昂贵ATE设备的依赖,仅仅依靠片上的资源完成对电路的测试[1-2]。传统的内测试方法如穷举/伪穷举测试、伪随机测试、确定性测试等方法,在测试时间、故障覆盖率、测试功耗和硬件开销等方面都值得改进,许多学者针对测试矢量生成结构的这些综合因素提出了解决方案,如文献[3-4]提出了一种低功耗DS-LFSR测试生成方案,方案不仅提高了故障覆盖率,而且还降低了部分测试功耗;文献[5]提出一种双模式的低功耗LFSR结构,该结构在不降低故障覆盖率的条件下,减少了超过70%的测试功耗;文献[6-7]提出了一种矢量插入结构,在保证一定故障覆盖率的前提下,通过降低原有的矢量对间的汉明距离,来减少测试功耗;文献[8]提出了一种基于格雷码的电路自测试序列的分配算法,方案根据电路的基本输入权重,合理分配格雷序列的跳变位,测试具有较高的故障覆盖率,而且更大程度上降低了测试功耗。

本文提出一种基于确定性矢量的低功耗测试生成方案,通过可配置反馈网络的LFSR来完成确定性测试矢量的生成,以保证有很高的故障覆盖率,并通过外围的单翻转矢量的生成逻辑,在欲生成的确定性测试矢量间插入单一翻转的测试矢量,以降低被测电路的各类功耗。对ISCAS’85基准电路的实验结果表明:该测试方案能得到很高的故障覆盖率,而且测试功耗降低明显。

1 可配置反馈网络的LFSR结构

传统的LFSR可以产生随机性较好的测试矢量,然而这类矢量只能检测出被测电路中的随机矢量可测性故障(Random Pattern Detectable Faults),而电路中的一部分抗随机性故障(Random Pattern Resistant Faults)需要借助固定的算法,产生一些有针对性的矢量才能够被检测[9]。可配置反馈网络的LFSR作为一种混合测试生成结构,既能生成确定性测试矢量,又能生成伪随机性测试矢量,本文正应用了该结构,以生成Atalanta工具模拟产生的一组确定性矢量集,以提高单位测试时间内的故障覆盖率。

1.1 确定性测试矢量的生成结构

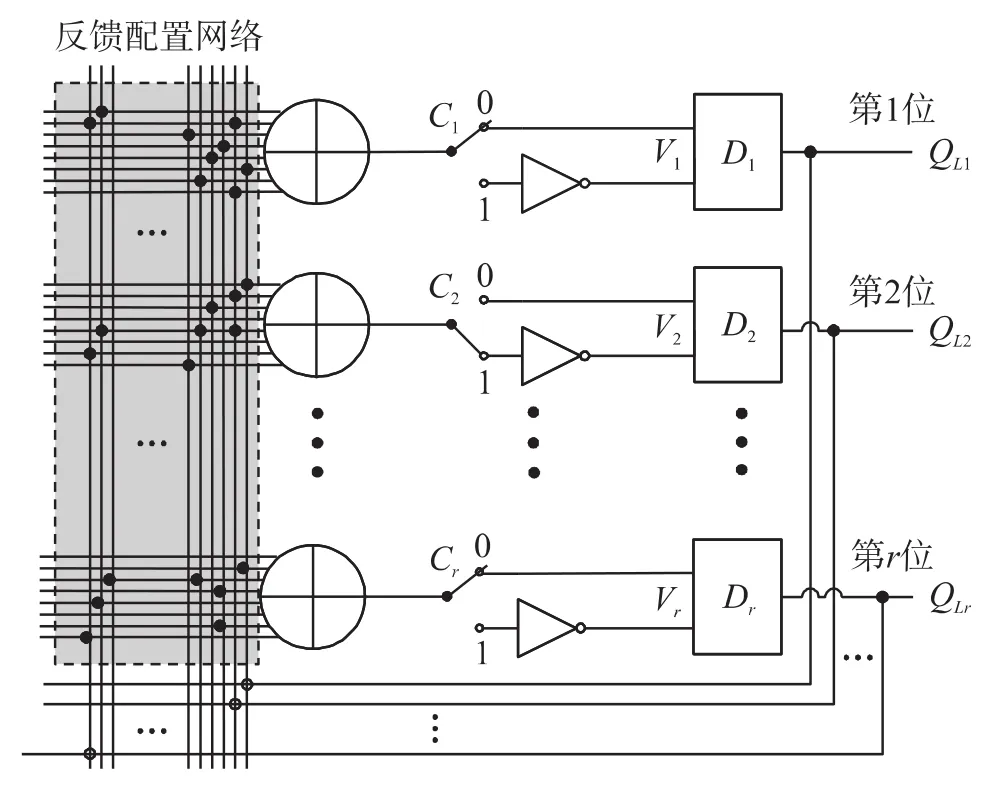

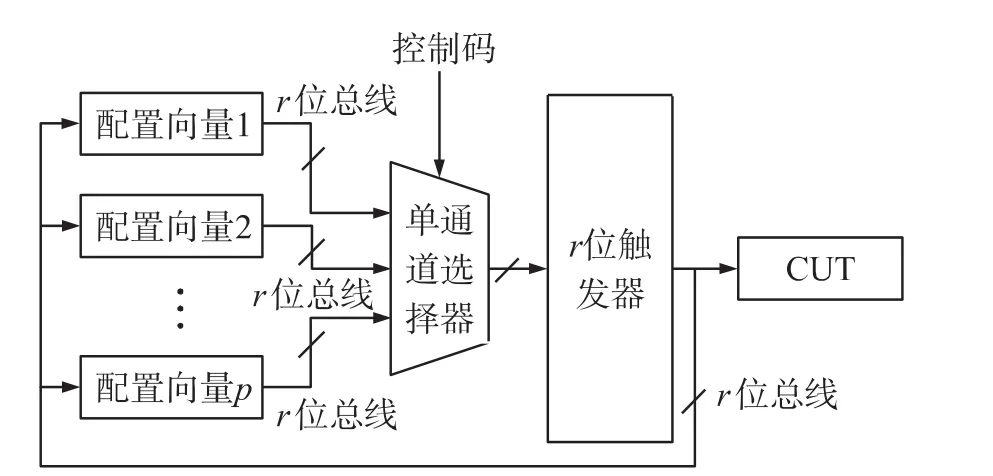

可配置反馈网络的LFSR的结构如图1所示,各个触发器的输入是由触发器输出经反馈异或配置和选择反向器配置得到(合并称“反馈配置”)。

图1 可配置LFSR结构

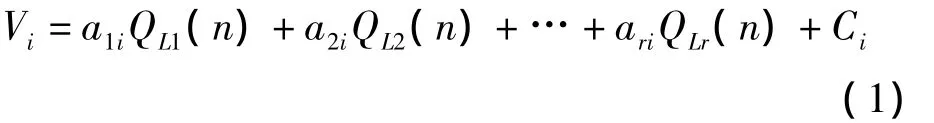

该电路的各个输入Vi可用含有r个触发器输出的逻辑变量QL1(n),QL2(n),…,QLr(n)和反向配置逻辑变量Ci表示成二元域内的线性非齐次方程:

其中aki为第k个触发器反馈接入第i位输入Vi的配置节点,aki∈{0,1},k、i=1,2,…,r.aki=1 时,表示反馈接入异或门,反之表示无反馈接入;Ci为非门控制,Ci∈{0,1},Ci=1时表示通过非门接入输入,反之则直通输入;QLi为第i位触发器输出。如果按确定性测试矢量集的顺序,将待生成的测试矢量的第i位从第1个序列到第s个序列依次代入到方程(1)中,即可得到矩阵方程(2),这里的表示第i位的第x个测试序列的次态值,x=1,2,…,s并有=V(x+1)i。并记 CNi=(a1i,a2i,…,ari,Ci)为该位的反馈配置向量,对应于式(2)中的各个部分,可简记为:b=A·CNi,其中b为确定性矢量在第i位的次态值,A中Vxi为确定性矢量的现态值,s为确定性测试集的大小。

如果方程(2)有解,说明该确定性测试集的第i位序列可以完全通过反馈配置向量CNi得到;反之,说明该反馈配置向量只能生成原确定性测试集在第i位中的一部分序列,而另一部分需要重新代入式(1),构造新的矩阵方程,寻求新的配置向量,直到全部测试集可解为止。故生成完整的确定性测试集,可能需要对原测试集进行划分,进而得到多个反馈配置向量。

1.2 确定性测试矢量的划分

图2为多通道的可配置LFSR结构,完整的确定性测试集被划分为p个子集,而每个子集由相应的配置向量作用一定的时钟来生成,其中配置通道的个数和配置向量的作用时钟都需要对原测试矢量的划分来决定,矢量划分的理论基础,就是非齐次方程组的有解判定定理。

图2 多通道的可配置LFSR结构

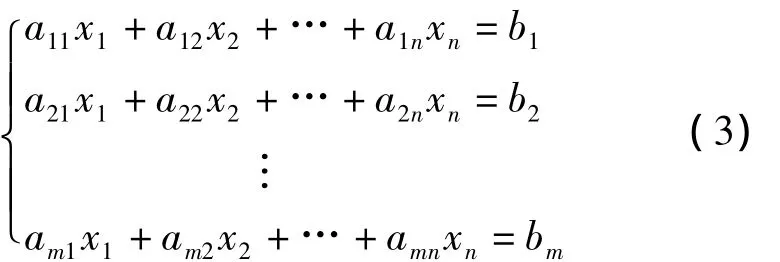

定理1非齐次线性方程组

定理2设η是非齐次方程组的一个特解,ξ1,ξ2,…,ξn-r,是其导出组的基础解系,则非齐次方程组(3)的通解为 η +k1ξ1+k2ξ2+ … +kn-rξn-r,其中r=R(A),k1,k2,…,kn-r为任意常数。

推论若R(A)=R(A|b)=n时,方程组(3)有唯一解;若R(A)=R(A|b)<n时,方程组(3)有无穷多解,其通解为 η +k1ξ1+k2ξ2+ … +kn-rξn-r;若R(A)≠R(A|b)时,方程组(3)无解。

根据上述的定理1和推论可知:方程组(3)中只有当R(A)=R(A|b)时,才可以求出其配置向量CNi,若R(A)≠R(A|b),则需要对原测试进行划分,划分的步骤为:

(1)将方程组(2)中的增广矩阵(A|b),做行初等变换(二元域内的模2加),使每行第一个非零元素下面的数为0。

(2)找出增广矩阵(A|b)中A阵全为0,而b中不为零的行,即使R(A)≠R(A|b)的行,那么该行即为原测试集的一个划分点。

(3)将原测试集在该划分点之后的测试矢量重新代入方程(2),并重复步骤(1)(2),直到剩余的测试矢量全部可解。

划分子集的多少,即为配置通道的个数,而划分子集的长度(子集中包含测试矢量的个数)就是每个配置向量的作用时钟数。

1.3 反馈配置向量的优化

根据定理(2)可知,非齐次方程可能存在多组解,而解结构的不同,整个结构的硬件开销也随之不同,因此为了获得较少的硬件开销,必须对方程的通解进行寻优。

对于反馈配置向量 CNi=(a1i,a2i,…,ari,Ci),其中各个元素取值为0或1,向量中的“1”元素对应着配置网络中的门结构,因此要使门结构最少,应以寻找通解中“1”最少的一组解向量作为限制条件,同时因非门比异或门的硬件开销要小,所以还可以在含“1”最少的通解中,尽量选择Ci=1的解,作为该位最优配置解进行解空间内的寻优,寻优步骤为:

(1)求出矩阵方程的基解(ξ1,ξ2,…,ξN)和特解η。

(2)将基解矩阵(ξ1,ξ2,…,ξN)T做初等行变换,使每行第一个非0元素以下和以上的各行对应元素为 0,得(ξ'1,ξ'2,…,ξ'N)T。

(3)计算 η 中含“1”的个数,记I(η),并在 ξ1',ξ2',…,ξN'中找出与 η 重复度最大的基 ξ'r1,做运算η1= η⊕ξ'r1。

(4)计算I(η1),并比较I(η)和I(η1)。若I(η)<I(η1),则 η 即为最优通解,算法停止;若I(η)≥I(η1),则在余下的 ξ'1,ξ'2,…,ξ'r1-1,ξ'r1+1,…,ξ'N中找出与 η1重复度最大的基 ξ'r2,重复(3)(4)两个步骤。

(5)在已寻得的所有最优通解中,尽量选择末位为“1”的通解。

2 低功耗测试生成的设计

2.1 测试功耗的产生与衡量标准

在集成电路测试过程中,往往因测试矢量的相关性较低,电路节点的翻转密度高,使得测试功耗要比正常工作时的功耗高出数倍[5-6],巨大的功耗聚集的热量不仅会缩短器件寿命甚至烧毁器件,而且还会严重影响测试质量。CMOS电路中的功耗来源主要分为静态功耗和动态功耗两种,其中的动态功耗约占总功耗的90%,因此减少动态功耗是降低系统功耗的有效途径。对于被测电路,当连续输入测试矢量对TPk=(Vk-1,Vk)时,定义在该区间的功耗Evk可表示为式(4):

式中i包括电路中所有的节点,Fi为该节点的扇出数,C0为单位输出的负载电容,VDD代表电源电压,S(i,k)为矢量对TPk引起节点i翻转的次数,因电源电压和单位输出负载电容是定值,S(i,k)×Fi是功耗分析中唯一可变因素,称S(i,k)×Fi为TPk作用在节点i上的WSA(Weighted Switching Activity),考虑电路总的测试向量集 TP=(V1,V2,…,Vn),k=1,2…,n-1。整个电路总功耗、平均功耗和峰值功耗都可以用WSA进行衡量,对应表达是依次为式(5)~式(7):

从上面的分析不难发现,被测电路的总功耗可以通过减少测试集长度来降低,也可通过减少测试节点的翻转来降低;在总功耗一定的情况下,增加测试集长度,可以降低平均功耗;电路的峰值功耗只能通过减少测试节点的翻转来降低。而这里被测电路内部节点的翻转,正比于其输入矢量的翻转密度[3],因此,减少测试矢量的翻转是降低被测电路各类功耗的有效方法。

2.2 低功耗测试结构

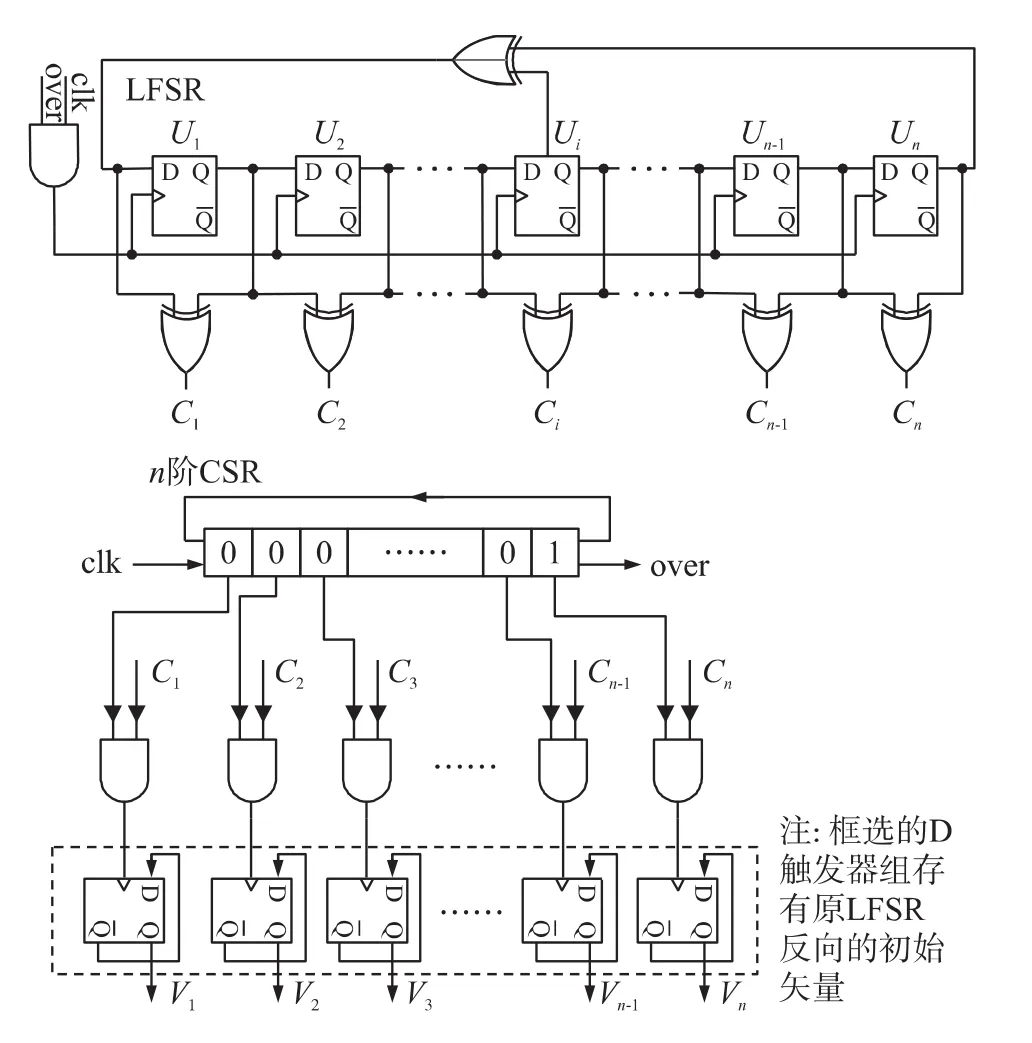

为了在不改变已生成的测试矢量基础上,得到矢量间单一翻转的测试矢量,可以采用如图3所示的LP-TPG(Low Power-Test Patterns Generation)结构[7],通过比较原有的相邻测试矢量,并用环形移位寄存器(CSR)按位依次检测比较结果,最后得到单翻转矢量进行插入。这样就保证了总功耗不变的情况下,增加了测试序列长度,从而降低平均功耗和峰值功耗。

由于随着被测电路输入端的增多,LP-TPG结构的硬件开销也会变得很大,因此做如图4的改进,图中应用了可配置LFSR结构替换了传统的LFSR,并利用了三个总线选择器就节省了原LP-TPG近一半的硬件开销。结构中可配置LFSR分为两个部分,即高n/2位(模块A)和低n/2位(模块B)(如果被测电路输入端为奇数位,则将最中间的触发器同时并入A、B两个模块),并将两部分的现、次态异或向量分时段送入n/2位的LP-TPG,原LP-TPG结构中的CSR输出over信号,需要经历高n/2位、低n/2位两次溢出计数后(couter=2),才能输出over’信号,并在下一个clk来临时,使可配置LFSR工作。此外总线选择信号也具备以下逻辑:当en=1时,高位进入翻转检测,低位保留现态值,即en1=0,en2=0,此时LP-TPG结构中的couter=1;当en=0时,低位进入翻转检测,高位保留次态值,即en1=1,en2=1,此时couter=2并返回0值。

图3 LP-TPG结构

图4 基于可配置LFSR的低功耗测试生成结构

3 实验及验证

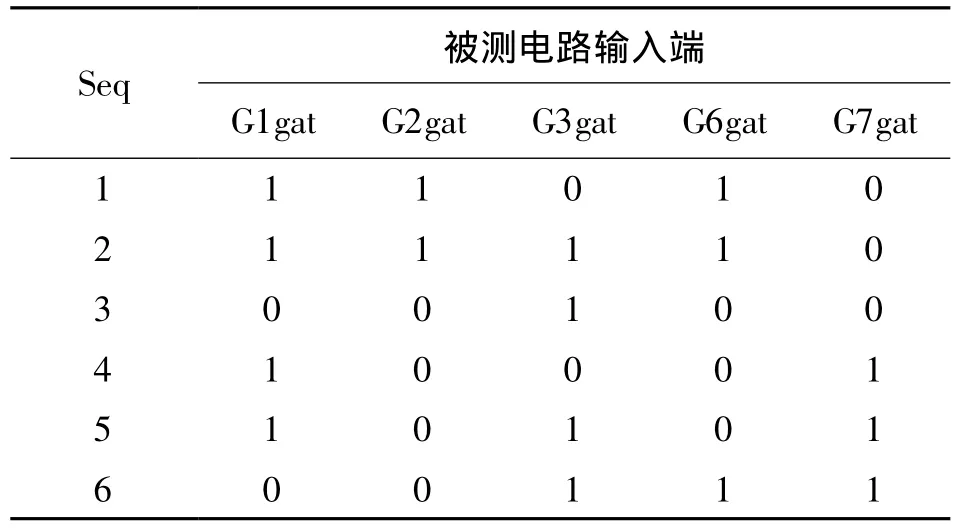

以ISCAS’85实验中的C17电路为例,利用Atalanta工具对该电路进行故障模拟,在随机数生成器的初始种子为“1358079950”时,得出的确定性矢量如表1所示,按照式(2),将全部位的序列代入到式(2)中,得到矩阵方程(8),并对该矩阵方程作矢量划分(式中用虚线标出)和通解优化处理,最优配置结果如表2所示。

表1 C17电路的确定性矢量

表2 C17电路确定性矢量的优化配置

按照矢量划分原理所得到方程个数,加载上述配置至图4所示结构,并作用相应的时钟数,即可在CUT的输入端得到表3所示的低功耗测试矢量。

表3 C17电路的低功耗测试矢量

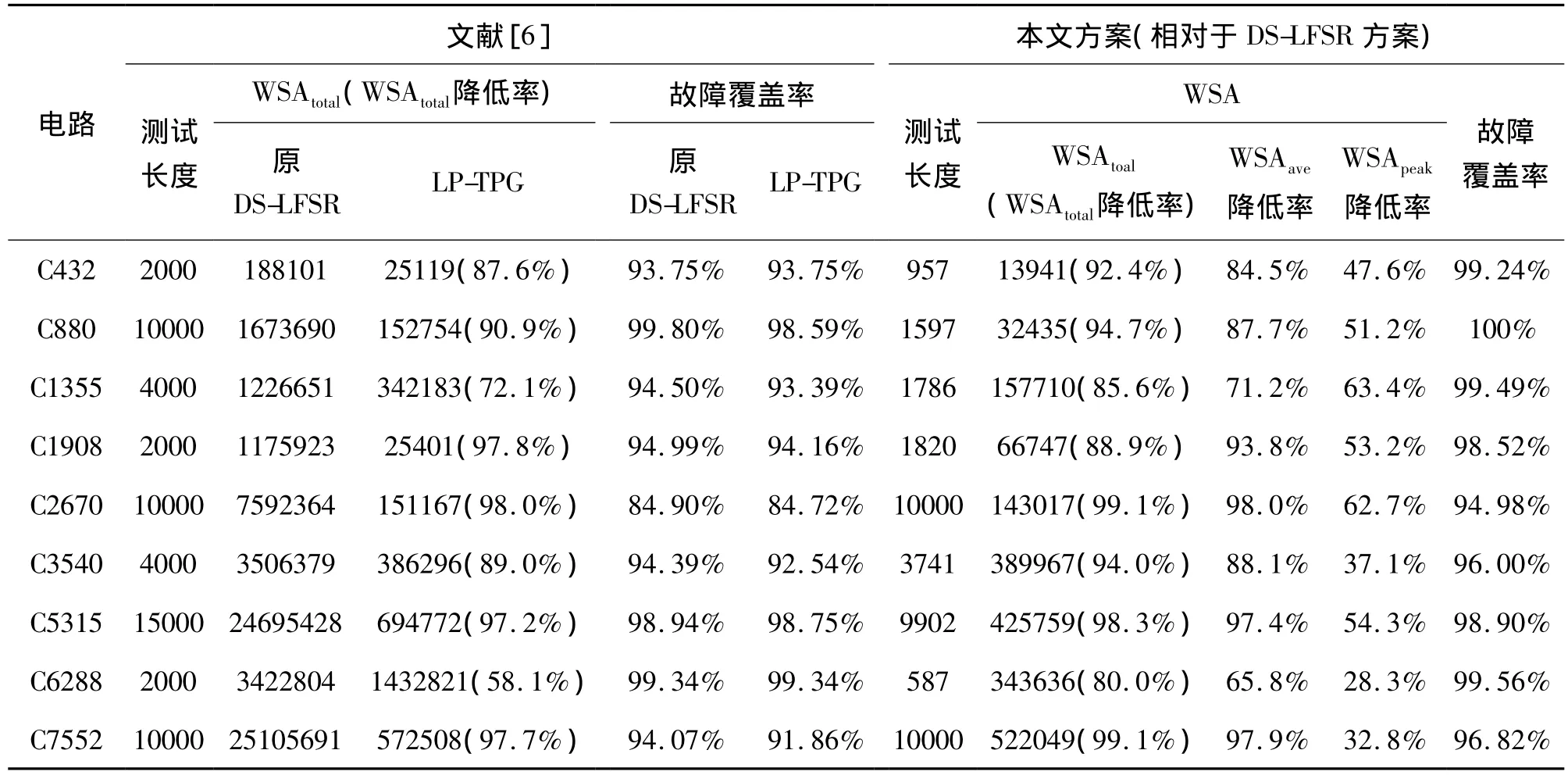

实验对组合电路集ISCAS’85的其他电路也进行了确定性矢量的模拟和单一翻转矢量的插入处理,并和文献[6]进行了测试长度、电路WSA和故障覆盖率的比较,如表4所示,实验中使用了C代码模拟了DS-LFSR测试生成过程和上述结构测试生成过程并进行WSA的计算,并应用了故障仿真工具fsim进行了故障覆盖率的计算。

实验结果表明,文中提出的低功耗测试生成方法,总功耗和平均功耗相对于DS-LFSR方案有大幅度的降低,峰值功耗也有所降低,除此之外,本文方案的测试集长度较小,故障覆盖率也有所提高。

由于本文方案使用的是确定性测试矢量的生成结构,因此相对于文献[6-7]的随机性测试,是在保证故障覆盖率的前提下,减少了大量随机测试的冗余矢量,同时插入了单一翻转的测试矢量,进而降低测试的各类功耗。该结构适合任意组合电路的测试。不足之处是本文LFSR的配置网络相对于传统LFSR额外增加了一部分硬件开销。

表4 ISCAS’85电路上的实验结果

4 结论

本文提出了一种高故障覆盖率的低功耗测试生成结构,结构利用可配置LFSR作为混合测试矢量生成器,以提高故障覆盖率,同时借助已生成矢量的现、次态异或值,按位逐一插入单跳变矢量,使得系统的各类功耗得到降低。针对LP-TPG结构,本文利用了异或矢量的分块处理方法,在不影响原LPTPG工作的前提下,减少了一部分硬件开销。经过对ISCAS’85电路的实验,表明了该结构不仅能很大程度上,降低被测电路总功耗和峰值功耗,而且能够保证在很高的故障覆盖率的情况下,减少测试集长度以缩短测试时间,提高故障检测效率,因此对推动低功耗BIST技术具有一定的意义。

[1]李鑫,梁华国,陈田,等.基于折叠计数器的低功耗确定BIST方案[J].仪器仪表学报,2011,32(12):1-5.

[2]吴义成,梁华国,李松坤,等.一种基于自选择状态的折叠计数器BIST方案[C]//第六届中国测试学术会议论文集,中国合肥,2010.

[3]Wang S,Gupta S K.DS-LFSR:A BIST TPG for Low Switching Activity[C]//IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2002,21(6):842-851.

[4]谈恩民,叶宏,施文康.低功耗BIST设计中的加权DS-LFSR测试生成方法研究[C]//中国仪器仪表与测控技术交流大会,中国四川,2007

[5]Zhang Zhe,Hu Chen,Xiang Wangxue,et al.A Low BIST Methodology Based on Two-Mode LFSR[J].Chinese Journal of Electron Devices,2004,27(4):705-709.

[6]何蓉晖,李晓维,宫云战.一种低功耗BIST测试产生器的方案[J].微电子学与计算机,2003,20(2):36-39.

[7]谈恩民,宋胜东,施文康.单/双跳变向量插入式低功耗BIST设计方法[J].微电子学与计算机,2007,24(7):183-185.

[8]孙海珺,王宣明,卢晓博,等.一种基于格雷码的电路自测试序列分配算法[J].计算机学报,2011,34(9):1697-1704.

[9]Chen C I H,George K.Configurable Two Dime-Nsional Linear Feed Back Shifter Registers for Parallel and Serial Built-In Self-Test[J].IEEE Trans,Instrumentation and Measurement,2004,53(4):1005-1014.