基于XPORT的多路数据转发单元的设计

连 洁

(河北省卫星导航技术与装备工程技术研究中心,河北石家庄050081)

0 引言

数据传输是一个系统工程中的重要环节。在物理层中的各个设备,它们的各个状态需要定时上报给计算机。计算机监视各个设备的运行状态并下发命令控制底层设备的工作。一般底层各个设备以串口进行通信。计算机实现全双工远程监控底层设备,需要把各个设备的串口数据按网络协议通过网络与计算机通信。工程中一般常用NPORT产品,它性能稳定、可配置程度高,但一个16路串口的NPORT体积大,价格昂贵,采购管理设备不便。因此,根据工程上的需求,本文阐述了基于串口转网络器件XPORT的多路数据转发的单板卡设计。针对多路并发串口的数据量大,需实时转发等特点,进行了相应的嵌入式程序设计。该设计与其他设备可集成在一个PXI机箱之中,不需外部再配置其他通信设备,方便搬移管理和使用。

1 总体设计

多路串口数据转发单元,按其功能分为2部分:①底层设备数据上报转发模块,汇总各个设备上报的数据信息为一路串口数据,通过网络转发给计算机;②计算机指令分路转发模块,把计算机下发的数据按地址分发给对应的设备。在数据转发的过程中不改变信息内容,透明转发。PXI机箱的槽位号与板卡ID号,由计算机灵活分配。板卡可不固定槽位,随意移动位置。多路串口数据转发单元根据计算机下发的地址表,在FPGA中配置板卡ID号与串口硬件端口的对应关系。在计算机下发数据时,按现在的地址分配表,把含该板卡ID号的数据帧下发到对应槽位的串口端口上。

各设备发送的数据,有帧长度不同且无时间顺序的特点,数据可能是并发或突发的,这就需要数据转发单元有足够快的顺序处理或者并行处理的能力。由于单片机工作时钟频率有限,在设备数量多且数据量大的情况下,处理的任务量容易超出其处理速度。出于以上考虑,底层设备数据上报采用FPGA并行处理。

计算机指令分路下发给底层设备,即计算机一路数据按设备地址分发给多路端口,这在时间上是一对一端口顺序传输的。此设计在单片机顺序处理实现较为方便。

1.1 硬件设计

根据设计的需求和特点,硬件在一块100 mm×160 mm的3U板卡上实现。它含有一块 FPGA、一块单片机和一个XPORT,附加串口驱动芯片等电路。

XPORT是由美国Lantronix公司于2002年研发成功,它是目前最小、最完整的串行口到以太网的转换方案。XPORT使用了Lantronix公司的DSTni系列网络芯片,10/100 M的 PHY,以及256 KB的RAM和512 KB的闪存。XPORT工作电压为3.3 V,支持TCP/IP等网络通信协议,有一个支持RS-232串行标准、速度最高可达960 Kbps的串行端口,提供一个RJ-45网络端口,可以方便快捷地实现串行设备与以太网的连接,从而实现远距离实时通信。

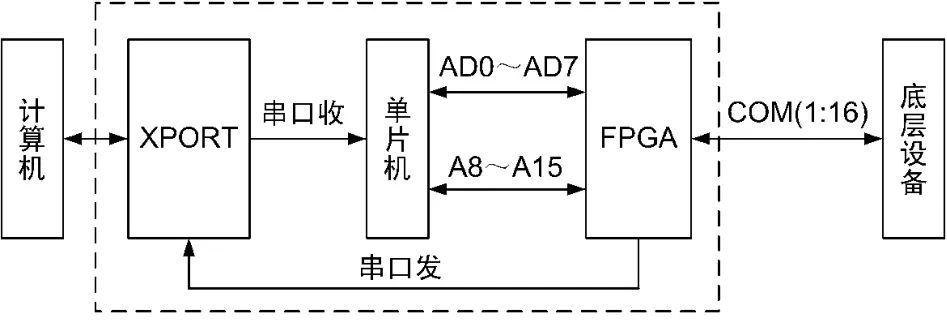

为满足需求且方便升级,FPGA选用Altera公司Cyclone II系列的EP2C35F484,逻辑单元33 216门,内存 483 840 bit[1,2]。单片机选用 ATMEL 公司的ATMEGA128L[3]。XPORT 选用型号为 XP1001001-03R。硬件设计及系统连接框图如图1所示。

图1 硬件设计及系统连接

计算机与底层各个设备之间由多路串口转发单元进行数据转发。底层设备的串口端连入FPGA。单片机的地址线和数据地址共用线均接入FPGA。单片机对计算机指令处理后,通过FPGA对各设备进行指令分发。转换单元与计算机之间的所有收发数据都通过配置 XPORT[4,5]进行串口与网口的协议转换,保证各个设备对计算机数据收发能够全双工通信。在实际工程中,设计预留了16路面对底层设备的串口。多路串口数据传输板卡与各个设备的串口为 RS232 异步传输[6-10]。

1.2 软件设计

软件设计包含的主要功能有底层设备数据汇总上报和计算机指令分路转发2部分。

其中,底层设备数据汇总上报部分的主要功能是将16路设备上报的监控业务等数据汇总为一路数据发送给监控计算机。此部分主要包括16路串口数据的并行接收处理,在上报串口空闲且有待发送的数据时,进行读取汇报的统一调度。

计算机指令分路转发部分的主要功能是将监控计算下发的指令解析出发送地址发送给相应设备的硬件通信端口。它此部分以单片机处理为主,FPGA中做地址译码和下发端口选通工作。监控计算机仅有一路数据,因此利用单片机自带的全双工串口收发处理功能解析串口数据。首先,单片机把计算机下发的串口数据,进行有效数据存储并解帧,把解出的目的地址送给FPGA。FPGA依据目的地址,把单片机输出串口端硬件连接到对应需要下发的底层设备端口上。当选通好后,待单片机判断完帧长度字节,按字节数读取缓冲区的数据,送到发送串口上。

2 需要解决的问题

各个底层设备的串口数据量大小不一,同一串口数据长度不一,各设备的各种数据发送时间不固定,会同时发送。转发延迟需要尽量小,控制在ms级。

转发监控计算机的下发数据时,下发电文数据量较大,且需要实时发送。以网络协议与计算机通信,要求板卡的集成度高、成本低,传输稳定可靠。

3 关键技术

在底层设备数据汇总上报设计中,有16路底层设备数据处理的并行模块。接收16路模块为节省存储空间,给单独开辟了适应其数据大小的存储空间。

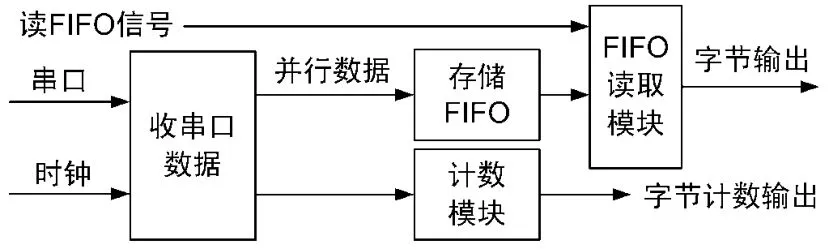

存储包含16路串口数据是并行处理且处理方式一致,其区别仅为该路串口总数据量的缓存大小,可设计单路串口数据处理模块复用成多路。串口处理模块的上一级有统一调度模块,通过判断该单路处理模块的FIFO存数情况,发出单路FIFO读取信号。一路串口上报数据处理模块的顶层设计如图2所示。该模块的主要输入端口是FIFO的读取信号、设备的串口数据和工作时钟,输出是缓存FIFO数据读出和字节计数。首先要按帧格式解包信息,判断是否为一帧的开始,并按帧信息给出的帧长度收串口数据,然后把完整的信息帧存入FIFO。需要注意的是,FIFO中的数据是以帧为单位,整帧存入、整帧取出。整帧包含帧头,且存入过程中无任何无用数据,便于发送模块准确读取整帧发送。

图2 FPGA单路串口上报处理模块顶层设计

对于存入和取出的FIFO数据有独立的整帧收发字节计数模块。当收完一整帧,帧尾标志锁存已计数的存入字节数,即为待发送整帧字节数。当按提供的字节数发送完毕,待发送字节数便减去发送字节。待发送标志就是判断待发送整帧字节数是否为0。当计算机串口空闲时,轮巡检查16个串口上报模块的待发送标志。若标志有效,占用串口,按待发送字节数读取FIFO数据,按串口规定要求发送。

防帧长度出错功能。若帧长度填错,到下一帧帧头到来也没收够数据,则以前数据加上下一帧帧头为一个整帧,存入该通道的FIFO。下一帧的判断和存储仍正确执行。这样上一个出错帧不会影响下一个正确帧的传输,不会造成漏传。这样在监控计算机收原始数据时,不完整帧尾出现2个帧头时,便能够发现该帧的错误。

在轮巡检查时刻,读取此时已准备好的整帧数据发送。发送完毕,立即巡查下一串口是否有数据待发送处理。这样的处理机制,可适应对数据传输处理时效有较高需求的系统。不因某一数据量大的设备长时间占用串口,而使其他串口等待时间过长。

计算机指令分路转发模块,面对下发数据量较大并且要求实时转发,所以设计中并没有将数据整帧全部缓存下来,再转发。在单片机的串口接收数据部分,开辟了20 byte的RAM作为缓存环形RAM使用,用于缓存一帧数据中的帧长、目的地址等关键信息。环形RAM的好处在于,不存储全部电文,实时转发且占用单片机RAM小。判断出目的地址,并给FPGA留出端口选择时间,便可把环形RAM区的数据从第1个地址开始送到单片机串口输出端。此操作有两个指针,一个为数据存储位置指针;另一个为数据读取位置指针。若两个地址重合,且数据长度计数还未够,表明数据传输暂时中断,发送完已读取的数据,等待收取数据。

对计算机的串口收发数据,均由硬件板卡上的XPORT进行网络协议的转换。将RS232数据传输接口变为网络协议传输,直接与计算机通信,使得整机设备集成度高,易便携,用户使用更简便。

4 性能测试

对多路串口数据转发单元的软硬件设计进行自测试,在极限情况下工作正常。在程序中添加16路数据发送模块,并行进行固定帧的发送,帧长度可自行调整。在16路数据总量几近115 200 bit的极限情况下,工作正常。计算机下发数据时,地址选通正确,且在传输长数据帧时可实时转发,转发延迟小于1 ms。

在实际工程进行验证,试验环境为一台通用PXI机箱,其中包含发射终端单元、下变频单元、接收终端、时频分路板卡和多路串口数据转发单元各一块。机箱内部所有板卡与监控计算机的通信均通过一块多路串口数据转发单元完成。每秒机箱各板卡上报的总数据量为17 360 bit,其中接收终端板卡上报数据量较大。该板卡每秒上报电文相关的信息达7 700 bit。以其中部分信息上报数据进行本设计的数据通信测试。

令监控计算机下发的注入信息填写固定数据。发射终端对信息也不进行处理,因此该信息是固定数,方便比对传输的正确性,即数据下发和底层数据上报形成闭环比对。令监控计算机比对上报的信息数据,便可知传输错误的bit数。各单元上报信息均有每秒上报的时标,可检查是否丢帧。监控计算机还对上报的所有原始信息进行源码存储,方便追溯查询。

5 性能测试结果分析

测试结果,如图3所示。

图3 电文数据比对

前两栏分别为接收终端单元A所上报的电文1和电文2。2种数据汇报频度均为上报5次/s。在拷机的43.27 h中,传输帧数778 906帧,总位数达1 121 624 640 bit。比对电文错误帧数,错误位数均为0。如图3中第3栏所示,多路串口转发单元在长时间的连续工作中,面对大数据量的传输,转发无误且无丢帧,工作性能稳定。

6 结束语

阐述了多路串口转发单元的硬件和软件设计。面对数据量大、数据长短不一致,且实时性要求较高的情况,本设计实现了数据的稳定可靠的转发传输。本单元对外接口以网络协议与计算机进行通信,使整机设备集成度高,方便在工程中的使用。测试中,连续工作43 h以上误码率为0。经实际工程应用,设计稳定可靠,现已形成通用化的设计,在实际工程中广泛使用。

[1] Altera Corp.Cyclone II Device Handbook [S],2008:1-3.

[2] Altera Corp.Pin Information for the Cy-cloneTMII EP2C35 Device[S],2008.

[3] Atmel Corp.ATmega128(L)Datasheet[S],2001.

[4] LANTRONIXCorp.XportUserGuide[M].USA:LANTRONIX Corp.,Part Number 900 - 270 Revision G March 2005:12-20.

[5] LANTRONIX Corp.Xport Integration Guide[M].USA:LANTRONIX Corp.,Part Number 900 - 310 Revision F March 2005:11-11.

[6] 沈金龙.计算机通信网[M].西安:西安电子科技大学出版社,2003:66-67.

[7] 刘丽格,李天保,石鑫刚.一种板间高速传输系统的设计与实现[J].无线电通信技术,2011,37(4):53 -55.

[8] 王 宇,许生旺,曹彦军,等.一种针对SSM的二层转发方法[J].无线电工程,2011,41(1):1 -4.

[9] 陈 燕,侯永彬,何朝玉,等.高速数据传输中ASI接口技术分析[J].无线电通信技术,2011,37(5):19-20,47.

[10]李 钊,李建军,李 冰,等.海量数据纹理映射技术研究[J].无线电通信技术,2011,37(4):34-36.