CPLD在电力电子控制系统中的应用

窦金生,顾月明

(1.中国人民解放军镇江船艇学院 江苏 镇江 212000;2.江苏科技大学 江苏 镇江 212000)

现代电力电子中对功率器件的驱动主要采用PWM脉冲,一般用来产生PWM的控制芯片是DSP。目前占有市场较大份额的DSP芯片是TI公司的C2000系列,典型的代表有32位定点的TMS320F2812和浮点型的TMS320F28335。其中TMS320F2812具有2个独立的三相全桥驱动电路,共12路PWM通道;TMS320F28335具有18路独立的PWM电路。随着多电平电路的发展或者希望一个控制芯片能够驱动多个功率模块,对PWM通道数的需求越来越多,为了满足上述需求,本文介绍了一种通过DSP的EMIF接口和CPLD来扩展PWM电路的方法。

1 系统硬件设计

CPLD在电子设备的设计方面有着许多优势,可以大幅度缩短设计周期,使产品可以迅速投入市场;Altera的CPLD具有很高的灵活性,可以在产品开发的任何阶段进行设计修改;拥有高性价比的集成度,以低成本实现各种功能。TI公司的C2000的DSP是一款专用于电力电子控制的芯片,本身带有AD、QEP、CAP、ePWM、外部中断等专用于电力电子及电机控制的外部接口。本系统使用的DSP型号是32位定点TMS320F2812,CPLD的型号是MAXII系列的EPM570T144I5,此CPLD的核电压和I/O管脚电压都是3.3 V,因此能够方便的和DSP的管脚相连。系统中,DSP主要负责SVPWM的算法运算,将计算出的占空比通过DSP的EMIF接口传送给CPLD。用户自己设置的PWM脉冲的死区值,频率值也都是通过DSP的EMIF接口传给CPLD的死区寄存器和频率寄存器。DSP与CPLD的硬件接口电路如图1所示,DSP的数据线(D0~D15)、低 3 位地址(A0~A2)、高 5 位地址线(A14~A18)、区域2的片选线 (XCS2)、写片选线 (WE)和输出时钟线(XCLKOUT)分别与CPLD对应的引脚相连。其中XCLKOUT为CPLD提供时钟脉冲,DSP采用30MH外部无源晶振,经锁相环后为DSP提供150 MHz的系统时钟,再经过4分频后通过 XCLKOUT输出 3.3 V的时钟脉冲。PWMAH、PWMAL、PWMBH、PWMBL、PWMCH、PWMCL 是 3 对互补的 PWM 脉冲输出引脚。

2 CPLD的软件设计

本系统主要扩展3对互补的PWM通道,需要译码保存模块,脉冲频率模块,比较模块,死区模块。译码保存模块主要将死区值,PWM脉冲周期值,以及3对PWM脉冲占空比值从DSP写入CPLD并保存。脉冲频率模块主要是根据译码保存模块输出的PWM脉冲周期值进行增减计数,产生对称三角波与各个占空比值进行比较后输出PWM脉冲。死区模块主要是对PWM脉冲进行死区延迟并生成互补的PWM脉冲。软件的整体框架图如图2所示,整个系统软件采用Verilog语言进行编写,其中比较模块可直接调用Quartus II的宏模块,当三角波的值大于占空比的值输出高电平,反之输出低电平。

图2 CPLD中软件整体框架图Fig.2 The overall framework of the CPLD software

2.1 译码保存模块的软件设计

译码保存模块的主要功能是实现DSP与CPLD的数据传输。其工作过程如下,当与CPLD相连的写信号线(WE)和区域2片选线(XCS2)变为低电平时,译码保存模块会判断地址线上的高低电平,若地址线上的高低电平与对应的初始定义值相等则将数据线上的高低电平存储在相应的reg变量中,其软件流程图如图3所示。

2.2 脉冲频率模块的软件设计

脉冲频率模块主要是根据PWM脉冲周期值和XCLKOUT产生对称的三角波,此三角波作为PWM的载波,PWM脉冲的频率由三角波的频率决定。脉冲频率模块的工作过程如下,DSP的XCLKOUT线产生一个脉冲上升沿时,脉冲频率模块中的计数器值增加1,当计数器中的值等于PWM脉冲周期值时,在下一个脉冲上升沿到来时,计数值减1,当计数器值为0时,在下一个脉冲上升沿时计数器开始增计数,如此循环就可以产生对称的三角波。其软件流程图如图4所示。

2.3 死区模块的软件设计

图4 脉冲频率模块的软件流程图Fig.4 Pulse frequency module of the software flow chart

死区模块主要根据比较模块输出的脉冲和死区时间来产生带死区时间的互补的PWM脉冲。其工作过程如下:当比较模块输出高电平时,计数器开始增计数,计数器的值达到死区时间值时PWMH产生高电平,否则PWMH为低电平。当比较模块输出低电平时,计数器开始减计数,当计数器的值为0时,PWML为高电平,否则PWML为低电平。死区模块的流程图如图5所示。

图5 死区模块的软件流程图Fig.5 Dead time module of the software flow chart

3 实验结果与分析

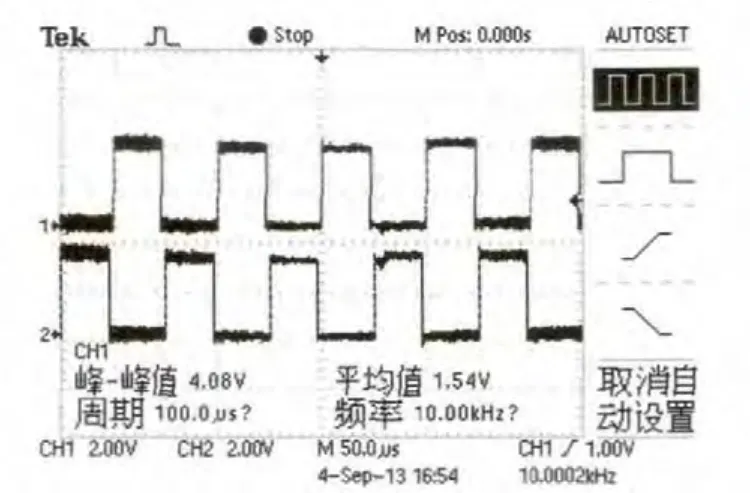

直接通过DSP向CPLD中写入PWM的频率为10 kHz,死区时间4.27 μs,占空比为 0.5时,A相上下桥臂(PWMAH、PWMAL)的实验波形如图6所示。

图6 A相占空比为0.5的PWM波形Fig.6 A phase PWM waveform duty cycle of 0.5

由DSP进行SVPWM运算然后将计算出的占空比值写入CPLD,输出的A相上下桥臂的PWM波形如图7所示,PWM的死区时间仍设置为4.27 μs,频率为10 kHz。

图7 A相SVPWM输出的波形图Fig.7 A phase waveform diagram of the SVPWM

实验结果表明,通过CPLD扩展PWM通道的方案具有很高的实时性和可靠性,理论上只要CPLD的逻辑单元足够多,可以扩展任意路PWM通道,因此基于DSP和CPLD的硬件架构在电力电子和电机控制方面具有很高的实际应用价值。

4 结 论

该硬件采用CPLD芯片作为PWM通道的扩展,CPLD的软件部分采用Verilog语言进行模块化设计,提高了系统的可靠性和可读性。该系统已在实验室中进行测试,实验表明该方案具有操作简便,实时性高的特点,达到设计的要求。

[1]周京华,等.CPLD/FPGA控制系统设计[M].北京:机械工业出版社,2011.

[2]邓伟.SVPWM算法优化及其FPGA/CPLD实现[D].广州:广东工业大学,2009.

[3]段博.三电平PWM整流器控制策略的研究[D].西安:西安理工大学,2010.

[4]彭超.永磁同步电机矢量控制MATLAB仿真研究 [J].科技信息,2012(3):87-89.PENG Chao.Permanent magnet synchronous motor vector control MATLAB simulation[J].Scientific and Technical Information,2012(3):87-89.

[5]肖咸盛.基于DSP的三相感应电动机矢量控制系统的研究[D].哈尔滨:哈尔滨工程大学,2009.

[6]王飞,刘铁湘.dsPIC30F在交流感应电机磁场定向控制中的应用[J].工业控制计算机,2009,22(7):93-94.WANG Fei,LIU Tie-xiang.Study of AC induction motor field-oriented digital control[J].Industrial Control Computer,2009,22(7):93-94.