基于内建自测试的测试向量生成方法

魏淑华 禚 永

(北方工业大学信息工程学院,北京 100144)

基于内建自测试的测试向量生成方法

魏淑华 禚 永

(北方工业大学信息工程学院,北京 100144)

内建自测试(BIST)方法是目前可测性设计(DFT)中最具应用前景的一种方法。BIST能显著提高电路的可测性,而测试向量的生成是关系BIST性能好坏的重要方面。测试生成的目的在于,生成可能少的测试向量并用以获得足够高的故障覆盖率,同时使得用于测试的硬件电路面积开销尽可能低,测试时间尽可能短。本文对几种内建自测试中测试向量生成方法进行了简单的介绍和对比研究,分析各自的优缺点,并在此基础上探讨了BIST面临的主要问题和发展方向。

可测性设计;内建自测试;测试向量生成;线性反馈移位寄存器

1.引言

近年来,集成电路设计方法和产品制造工艺发展迅速,然而,随之而来的集成电路的可测性问题,已成为提高产品可靠性和成品合格率的一个关键[1]。合理的可测性设计可以有效地降低测试生成的难度,提高故障覆盖率,缩短测试周期,降低测试成本,因此,可测性设计在集成电路测试中变得尤为重要[2]。内建自测试是近些年比较热门的一种可测性设计方法,它能较便捷地生成测试向量,并且可以保证较高的故障覆盖率和较短的测试周期,从而大大降低集成电路的测试成本。随着芯片集成度的提高,内建自测试已经在现代集成电路的测试中得到广泛的应用。

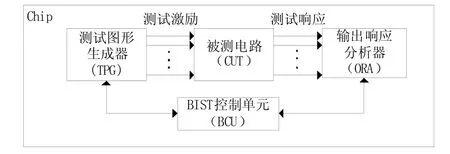

2.内建自测试(BIST)的结构

内建自测试电路一般包括测试图形生成器(激励),被测电路(circuits under Test,CUT),输出响应分析器和内建自测试控制单元。如图1所示。其测试原理为;TPG生成的测试信号加到CUT中,ORA对测试输出结果进行压缩,然后与理想结果进行比对分析,给出通过或不通过的结果,所有测试操作由BIST控制单元(BCU)控制[3]。

图1 典型内建自测试结构

3.测试响应的生成

目前应用于集成电路测试的测试向量生成方法,大体可分为两大类:一类是针对故障的确定性测试向量生成,这种测试向量生成方法需要使用专门的算法,如D算法,FAN算法,由于算法是基于故障来生成测试向量,并没有冗余的测试向量,故而测试向量长度很短,然而,因为测试向量生成需要专门的算法,所以测试向量生成比较困难。另一类是用采用特定的测试向量生成电路生成随机的或是伪随机的测试向量,对于生成的随机或伪随机测试向量,可以用足够长度的测试图形来保证故障覆盖率。

3.1 确定性测试向量生成

确定性测试向量生成的算法中,常见的有D算法,FAN算法等,都可以完成测试向量的生成。在此简单介绍D算法测试生成。

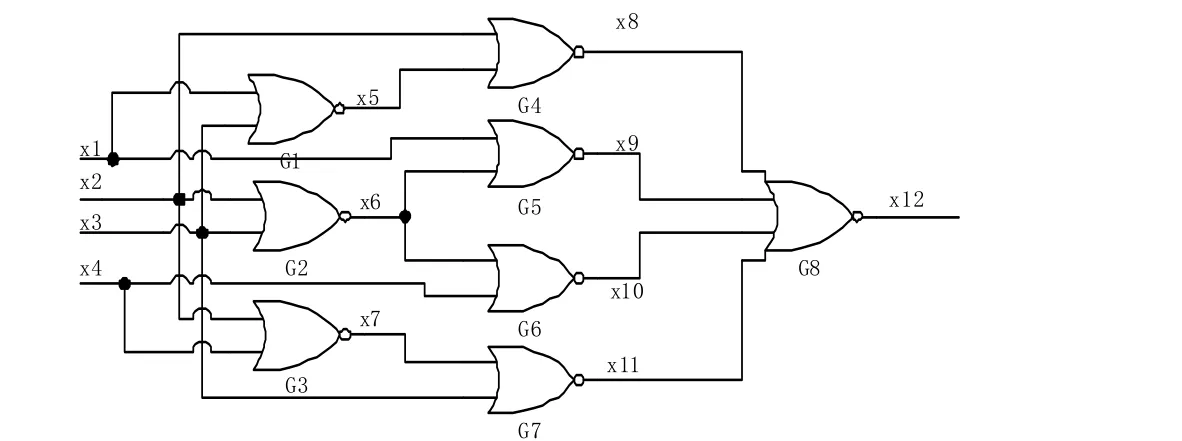

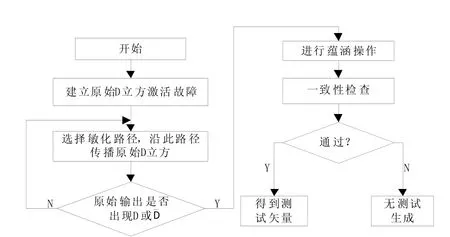

D算法的基本思路是:为了测试故障,必须使故障点的正常值与故障值产生差异,并将它们传送到输出端。另外,要先建立被测电路故障元件的原始D立方;再进行D驱赶,直到输出出现D或D非就表示已将故障点的故障传送到输出。驱赶成功之后,对电路中非敏化路径上的逻辑门进行蕴涵操作。之后进行一致性检查,判断某些线在各个过程中所赋予的值是否一致,若成功则确定测试图形,否则无测试生成。如图2所示的被测电路,为四输入但输出组合逻辑电路,用C语言编写D算法程序流程图如图3所示。

图2 被测电路图

内建自测试在集成电路测试中有诸多优点,比如:不用依赖专门的测试仪器即可在电路内部生成测试向量;可以缩短测试周期;可以大幅度降低测试成本;能实现在系统测试等[4]。

图3流程图

此向量生成法的优点有:测试向量长度较短,与其它测试生成法生成的图形相比,测试施加时间最短,并可以保证很高的故障覆盖率。缺点是测试生成方法非常复杂,测试生成时间非常长,测试开销太大,成本太高。

3.2 伪随机测试向量生成

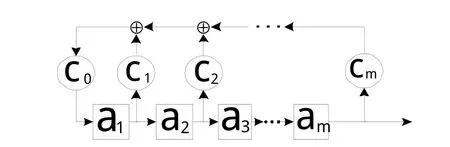

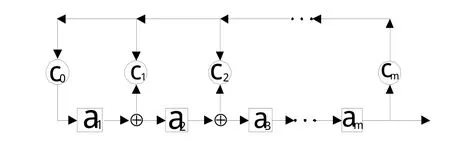

伪随机测试生成是用无输入的线性反馈移位寄存器(LFSR)构成伪随机序列生成电路,所生成的序列只与寄存器的初始状态和反馈方式有关[5]。图4和图5是线性反馈移位寄存器生成测试向量的两种反馈连接方式。图4为外部异或的LFSR,图5为内部异或的LFSR。

图4外部异或的LFSR

图5内部异或的LFSR

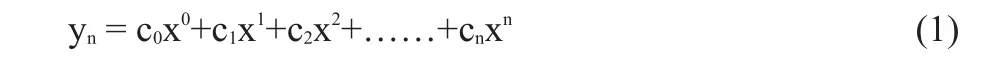

对于图4和图5,ai(i=1,2,……m)表示寄存器,ci(i=1,2……m)表示此处的异或门反馈,ci=1有异或门反馈连接,ci= 0则无异或门反馈连接,两种不同的反馈连接方式所产生的函数都可以表示为:

图6 伪随机测试故障覆盖率与测试向量数关系

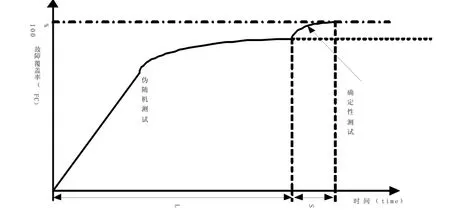

伪随机测试向量生成的优点在于,既用于组合逻辑电路,也适用于时序逻辑电路,而且不需要专门的算法,测试生成较简单。用LFSR生成测试向量,是目前BIST中应用最广的测试向量生成方法。然而这种测试向量生成法也存在难以解决的问题,如果测试向量长度太短,则测试时间也就很短,但是不能保证较高的故障覆盖率,如果想通过增加测试向量长度来保证足够的故障覆盖率,又大大增加了测试时间,即很难用较短的测试向量保证足够高的故障覆盖率。从图6中我们可以看出,刚开始时,随着伪随机测试向量数的增加,故障覆盖率会提高,但是伪随机测试向量数增加到一定程度,故障覆盖率不再有明显地提高。这就意味着,增加相同长度的测试向量数,能检测到的故障数越来越少,出现很多冗余的测试向量,这些多余的测试向量,不仅不能检测到任何故障,还会延长测试时间。另外,从整体性能上看,采用混合连接型构成的测试向量生成电路的性能要更好些[6]。

3.3 混合测试向量生成

混合测试向量生成方法,结合利用了以上两种测试向量生成方法。首先用伪随机测试法进行测试,这样被测电路中的很多容易检测到的故障会被检测出来,然后,用确定性测试向量测试难测故障,既可以实现快速测试,又可以保证故障覆盖率。这种测试方法主要是通过调节伪随机测试向量和确定性测试向量的长度,来平衡测试时间和故障覆盖率。如图7所示,L是伪随机测试向量长度,S是确定性测试向量长度。

图7 伪随机测试向量个数与故障覆盖率的关系图

混合测试向量测试方法的优点是,对于不同的实际需要,可以通过调节两种测试向量的比率,来调整测试时间和故障覆盖率。缺点是,若想进行快速测试,则不能保证较高故障覆盖率,若想提高故障覆盖率,必须增加伪随机测试向量的长度,从而增加了测试施加时间。

3.4 加权伪随机测试向量生成

加权伪随机测试向量生成方法,可以通过调节每个输入产生0或1的概率,使产生的测试代码更可能检测到难检测故障。图8是一个加权伪随机测试向量生成器,它由一个4选1数据选择器,控制两个输入,进行权重概率的选择。在伪随机测试向量生成方法中,每个输入产生0或1的概率都是0.5。在加权伪随机测试向量生成中,产生0或1的概率可以调整。

图8加权伪随机测试向量生成器

加权伪随机测试向量生成的优点在于,测试代码较短,故测试时间较短,并且能保证较高的故障覆盖率。缺点是为了保证尽可能高的故障覆盖率,要选择多个不同的权重,多个权重集合会生成很多多余的随机测试代码,从而导致了过多的硬件开销,增加了测试成本。

3.5 自反馈测试向量生成

以上几种测试生成方法都是由专门的电路生成测试向量,测试向量与被测电路无关,这些专门的测试向量生成电路须或多或少要占用一些芯片面积。现在有这么一种设计思想,选取被测电路的一些内部节点作为反馈,通过触发器,作为测试向量连接到被测电路输入端,无需专门的测试向量生成电路,而是从被测电路内部节点通过触发器生成测试向量,自反馈测试向量生成方法就是在这种思想下产生的。

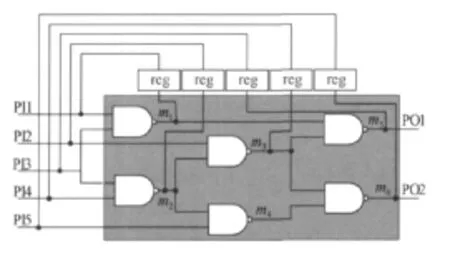

以图9为例,简单说明自反馈测试生成方法。

图9 c17电路的一种自反馈测试生成

图9中阴影部分的c17电路为被测电路(可任选其他电路作为被测电路,此处选择较为简单的c17电路是为了便于说明这种测试生成方法)。C17电路有5个输入端,6个内部节点(包括两个输出端)。从6个节点中任意找出5个,选择合适的顺序通过触发器连接到c17的输入端。在P11,P12,P13,P14,P15处导入一组原始输入作为种子,从而对c17电路施加了初始激励,在初始激励的作用下,被测电路中被选择的5个内部节点的状态作为第二组向量,通过触发器反馈被测电路的输入端,一个时钟信号周期后,被测电路内部节点状态会改变,再选取这5个节点的状态作为第三组向量,以此类推。被选取的5个内部节点,每经过一个时钟信号周期后,状态都会改变,改变后的5个内部节点状态,再次通过触发器反馈到被测电路,作为下一组测试向量。可以看出,这种测试向量是通过被测电路自身产生的,无需专门设计测试向量生成电路。然而,这种自反馈测试生成方法所面临的问题是,怎样选取内部节点,并以何种顺序反馈到被测电路的原始输入端,才能使产生的测试向量能更好更快地完成电路的测试。被测电路有6个内部节点,由排列组合可得,共有720种反馈方式,如果被测电路很复杂,则反馈方式更多,不可能一一尝试,故这种方法有待进一步完善。按照图9所示的反馈方式,并把(01100)作为种子向量施加到原始输入端,用modelsim仿真得到如图10所示的结果。

图10 c17自反馈测试仿真图

图10中的G1,G2,G3,G4,G5即选取的5个内部节点。从仿真结果中可以看出,4个时钟信号周期后,测试向量开始循环,即有4组有效测试向量。

这种测试向量生成方法的优点很明显,它可以减少BIST的面积开销,并实现全速测试。缺点是很难对故障进行诊断,即只能检测被测电路是否存在故障,而不能确定故障具体所在的位置。此外,这种测试生成很难保证较高的故障覆盖率。

4.结语

本文主要介绍了几种BIST的测试向量生成方法,分析了几种方法的优缺点。从上面的介绍可知,所有的测试向量生成方法都不是万能的,都有自己的适用条件,每种测试向量生成方法都有自己的优点和不足。针对特定的被测电路,要仔细分析被测电路的特点, 权衡各种测试向量生成方法的利弊,从而得到最合适的测试生成方法。

[1]汪昱.基于非确定门延时的瞬态电流测试生成算法研究及BIST测试产生器设计[D].长沙:湖南大学,2004.

[2]路思安,史峥,严晓浪.面向系统芯片的可测性设计[J].微电子学,2001,31(6):440-442.

[3]Wey C L.Built-in self-test(BIST)structure for analog circuit fault diagnosis[J].IEEE Transactions on Instrumentation and Measurement,1990,39(3):517-521.

[4]李立健,赵瑞莲.减少多种子内建自测试方法硬件开销的有效途径[J].计算机辅助设计与图形学学报,2003,15(6):662-666.

[5]雷绍冲,邵志标,梁峰.VLSI测试方法学和可测性设计[M].北京:电子工业出版社,2005.

[6]Wang S M.DS-LFSR:A BIST TPG for Low Switching Activity [J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2002,21(7):842-851.

Test Vector Generation Methods Based on BIST

Wei Shuhua Zhuo Yong

(North China University of Technology,Beijing 100144)

BIST is the most promising method in DFT.BIST can significantly improve the testability of the circuits,and test vector generation is one of the most important parts of BIST.The focus of test vector generation is how to generate new vectors as few as possible that can achieve fault coverage sufficiently while test circuits area overhead and the testing time should be as little as possible.In this paper,many methods for test vector generation are analyzed and contrasted.In the end,we discuss issues to be resolved and its development direction.

Design for Test(DFT);Built in Self Test(BIST);test vector generation;linear feedback shift register

魏淑华,女,山东聊城人,博士,讲师。研究方向:集成电路设计,集成电路测试。

北京市教委科研计划,项目编号:KM201410009005。