FPGA构造单向串行LVDS接口RAM存储器

宋 娟,吴荣斌,张 刚

(1.太原理工大学信息工程学院,山西太原030024;2.兰州交通大学电子与信息工程学院,甘肃兰州730070)

大数据时代,越来越多的信息转换为数据进行存储和处理,因此对控制系统中存储系统的数据快速处理能力和实时性提出更高要求,否则极易造成数据处理中的“瓶颈”现象[1-2]。并行传输方式在提升时钟频率时容易引起信号线间的互扰,导致传输错误,同时增加位宽会增加系统板布线密度,因此串行通信技术正在取代并行总线而成为高速数据接口的主流,而低压差分信号技术(Low Voltage Differential Signaling,LVDS)在各种高速串行总线得到普遍应用。

目前,嵌入式系统CPU与RAM的控制端口、读写使能、地址及数据总线相连,为节约CPU引脚资源,提高其访问内存的速度,本文使用FPGA提供的RAM IP核,设计实现了基于有限状态机的单向串行只写总线型接口RAM存储器,该存储器与CPU通过单向串行只写总线(One-way Write-Only Serial Bus,OWOSB)进行数据交换[3],并且使用低压差分传输技术抑制信号干扰,有利于提高数据访问速率和传输可靠性。不同于CPU直接通过并行线对RAM存储器进行访问的模式,该存储器以消息包的方式进行访问。

CPU与存储器之间只有两对差分数据线相连,很大程度上节约了RAM之前所需要的并行总线,因此CPU可以不受地址和数据引脚的限制,增大访问的内存容量。并且串行差分信号线间干扰较小,有利于提高CPU访问存储器的速度,具有良好的扩展性。

1 存储器的结构设计

1.1 存储器系统总体结构

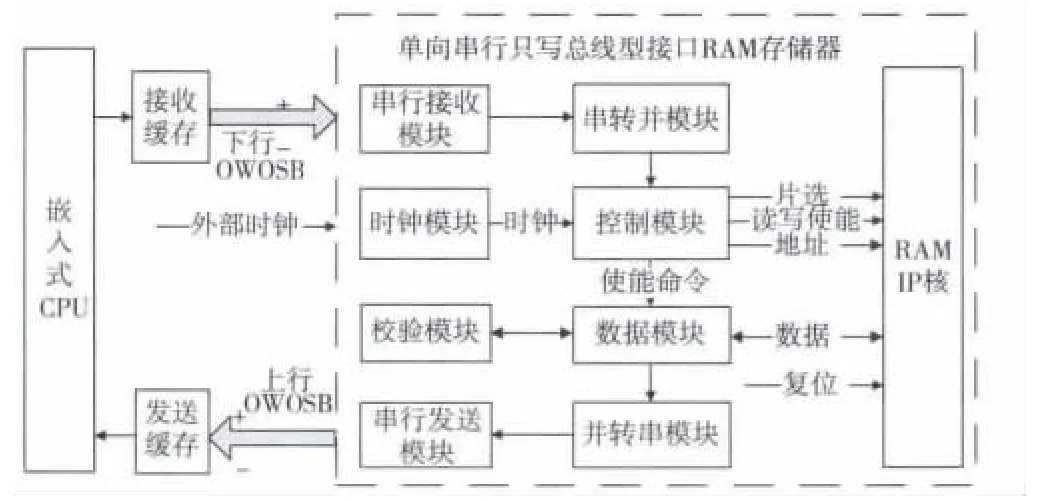

单向串行只写总线型接口RAM存储器有时钟、复位和单向串行只写上行总线3个输入和1个单向串行只写下行总线端口。主要由8个模块组成:时钟模块、串行数据接收模块、串转并模块、控制模块、数据模块、串行数据发送模块、并转串模块以及校验模块,见图1。

图1 RAM存储器系统结构框图

时钟模块:为存储器的其他各个模块提供所需时钟频率。

串行接收/发送模块:接收或发送消息包。

串转并模块:对串行数据包进行解析分包,把串行数据转为并行数据。

并转串模块:把RAM中读出的并行数据由高位到低位串行发送,并把发送数据帧头与32位校验值封装到数据包。

控制模块:从并行数据中提取出片选信号、读写使能、读写数据长度、命令和地址等信息,控制RAM读写操作。

校验模块:对数据进行校验计算。

数据模块:提供与RAM IP核的数据接口。

1.2 接收缓存模块

存储器与嵌入式CPU之间首先需要1个缓存来暂时存放CPU向RAM中写入的数据,本文所使用的缓存都是Xilinx公司提供的FIFO缓存IP核。CPU以32位为单位进行数据处理,而本文所设计的RAM存储器是以串行数据进行接收的,因此,FIFO的输入数据宽度为32 bit,输出数据宽度为1 bit。缓存读和写采用不同频率的时钟,写时钟频率与CPU相同,读时钟频率与串行传输频率相同,这是考虑到串行传输的特点,可以通过提高时钟频率来提高传输的速度,也方便数据的存取。

发送缓存模块类似,不再赘述。

1.3 时钟模块

Xilinx Virtex-5开发板内含锁相环(Phase Locked Loop,PLL)模块与8个数字时钟处理器(Digital Clock Management,DCM)模块[4-5]。PLL 是一种反馈电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,从而使得电路上的时钟和某一外部时钟的相位同步,DCM模块内部构成:延迟锁相环(Delay Locked Loop,DLL),其核心功能是消除输入时钟与输出时钟之间的延时;数字频率综合器(Digital Frequency Synthesiser,DFS):可对时钟进行倍频、分频合成新频率;PS(相位偏移):可对DCM模块的9个输出信号进行相位的偏移;状态逻辑:LOCKED信号有效时,输出时钟才可以使用,在此之前,输出时钟处于复杂不稳定状态。

该开发平台系统时钟为100 MHz,本文使用2个DCM模块和2个PLL模块进行级联,最后输出2.15 GHz提供给RAM存储器,具体如图2。

图2 时钟模块

1.4 校验模块

在高速数据采集系统中,必须保证在限定时间内有足够的数据传输速率和存储容量,而信号在总线的传输过程中不可避免的会发生突发性错误,为了提高系统的可靠性,引入数据检错机制,即循环冗余校验(Cyclic Redundancy Check ,CRC)并行算法[6-7]。

CRC是一种误码检测能力强、开销小、抗干扰性能优异的校验码,从其检错能力来看,它所不能发现的错误的几率仅为0.004 7%以下。从性能上和资源上考虑,均远远优于奇偶校验及算术和校验等方式,也是数据存储和数据通讯领域最常用的差错校验码,其特征是信息字段和校验字段的长度可以任意选定。

本文在存储器数据收发过程中均使用8位并行CRC校验法进行数据检错,其生成多项式为G(x)=1+x+x2+x3+x6+x7,系数序列记为11001111。存储器在接收数据结束后,把计算出的CRC校验值与CPU发送的校验值进行比较,如果两个值不一样,则在数据传输过程中产生错误,返回传输失败信号,请求CPU重新发送,若相同,则传输正确,返回传输成功信号。

2 存储器的实现

2.1 串行消息帧格式定义

单向串行只写总线OWOSB,其信息的传递只能沿单一方向进行传输,在本文OWOSB只用到两根,一根为上行总线,一根为下行总线。

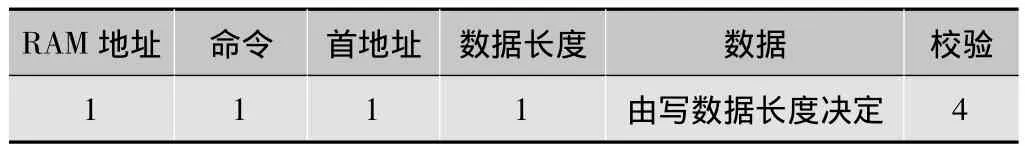

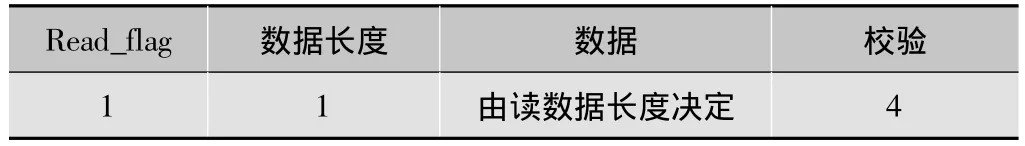

本文定义了RAM存储器OWOSB通信数据写/读帧格式,具体如表1~表2。

表1 串行写数据帧格式 byte

表2 读数据帧格式 byte

RAM地址:使用1 byte给每个RAM存储器进行编号;

命令:表示写/读命令,使用“00001111”表示写命令,“11110000”表示读命令;

首地址:代表写/读数据的起始地址;

数据:写入/读取的数据,通过数据长度决定该字段长度;

校验序列:表示帧校验;

Read_flag(读数据先导):用“10101010”表示,CPU 检测到“10101010”时,则可识别该帧为RAM中读出的数据帧。

2.2 存储器接收状态转移图

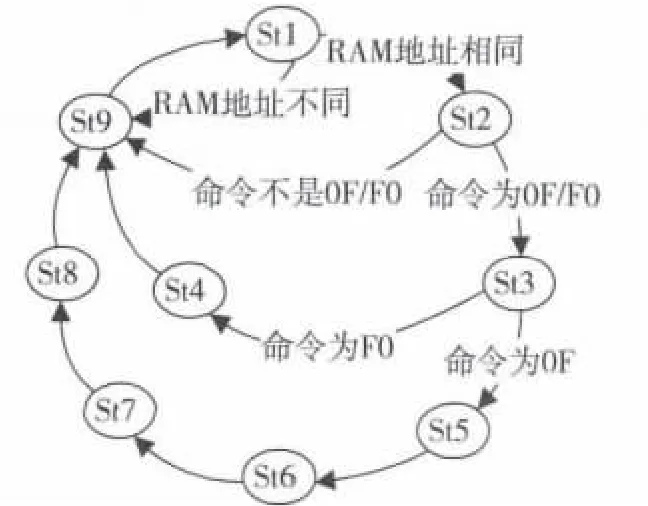

本文使用有限状态机来实现单向串行LVDS接口RAM存储器,图3是RAM存储器接收状态转移图,各个状态含义如下:

St1:空闲,等待接收数据帧;

St2:接收CPU发送的写/读数据命令;

St3:接收写/读数据的首地址;

水分含量在42.99~64.78g/100g之间,平均含量为59.12g/100g,不同部位的平均含量高低依次为颈肩肉含量61.78g/100g、后腿肉含量60.83g/100g、前腿肉含量57.85g/100g、最长肌肉含量55.35g/100g、胸腹部肉含量43.27g/100g。

St4:接收读数据长度;

St5:接收写数据长度;

St6:接收要向存储器写入的数据;

St7:接收32bit的校验序列;

St8:验证接收到的数据是否正确;

St9:接收数据结束。

图3 接收命令状态转移图

系统复位后存储器处于空闲状态;当接收到8 bit数据时,先判断该数据是否与本RAM地址相符合,如相符,说明该帧是发送到本RAM的,继续接收数据,如不符合,则跳转到结束状态;接收到RAM地址,经过8个时钟周期,判断接收到的数据,若是“00001111”或者“11110000”,则将该命令保存到cmd_s,继续下一步状态跳转,若为其他,则状态机跳转到结束状态;命令接收完毕,再经过8个时钟周期,把接收到的读写起始地址存到寄存器;如果是cmd_s是“00001111”,表示CPU写入数据,此时状态跳转到接收写数据长度;如果cmd_s是“11110000”,则表示CPU读取数据,此时状态跳转到接收读数据长度。

在接收写数据长度状态下,根据数据长度,接收来自CPU的存储数据和4个字节的校验数据,并返回一个校验标识信号。如果数据接收正确,用“1”表示;否则用“0”表示,并跳转到结束状态。最后返回空闲状态。在接收读数据状态下,接收要读取的数据长度,最后接收数据结束并返回空闲状态。

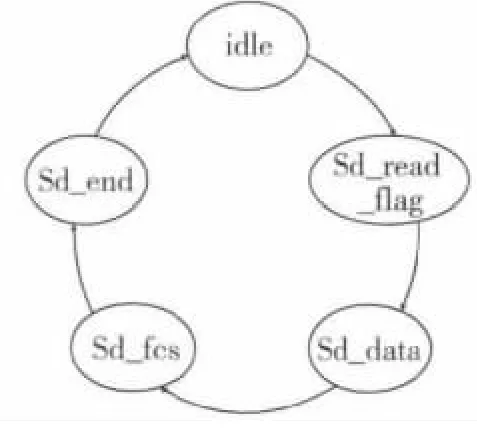

2.3 存储器发送状态转移图

复位后,存储器为空闲状态;依据发送数据帧格式,RAM存储器先发送读数据先导,之后发送从RAM内读出的数据,发送过程中要对数据进行校验计算,发送数据完毕,发送32位校验值。最后发送结束,返回等待状态。RAM存储器发送读数据状态转移见图4。

3 验证结果

3.1 测试结果

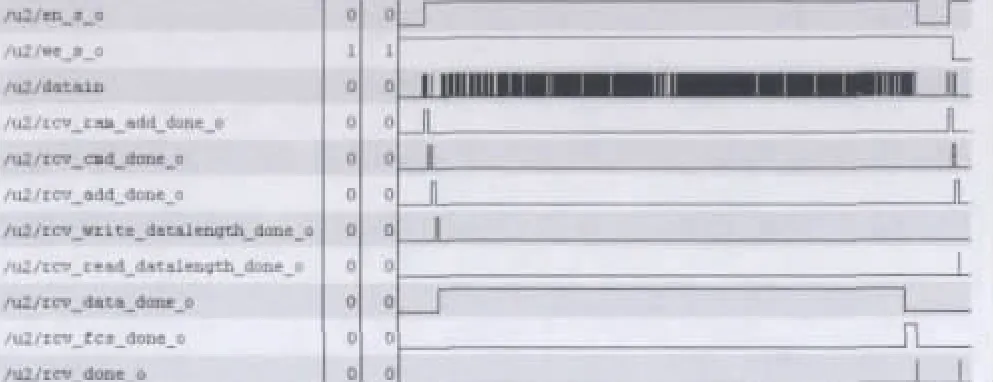

本文使用ISE在线逻辑分析仪ChipScope,采集RAM存储器写/读操作,采集所用时钟频率为2.15 GHz,RAM存储器数据宽度16,深度256。

图5中,Datain是存储器串行输入端口得到的数据,接收到RAM地址后,与本RAM地址相符合,则将本RAM的使能置高,接收到命令为“0F”即向RAM写入数据,因此将读写使能置高,接收到命令“F0”即从RAM读出数据,因此将读写使能置低,其他均为标志位,为高电平时代表成功接收帧的各个字段,rcv_done_o=1,标志着存储器接收正确。

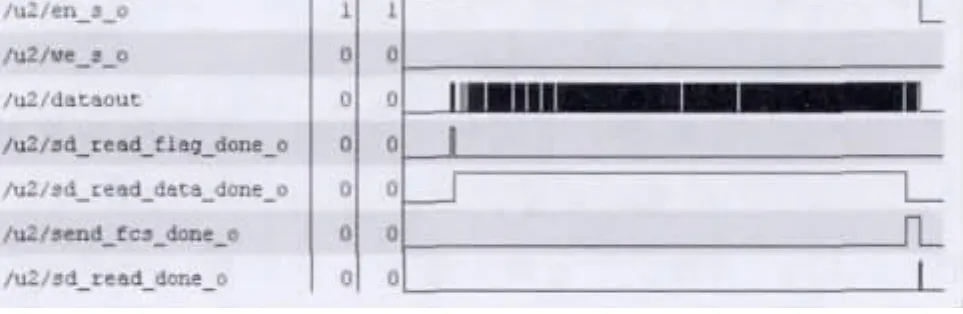

图6中,Dataout是存储器向CPU发送的串行数据,依照帧格式定义,该端口先发送读先导“10101010”,之后发送读出的数据以及32位校验值。sd_read_done_out=1,表示从RAM中读出的数据正确。

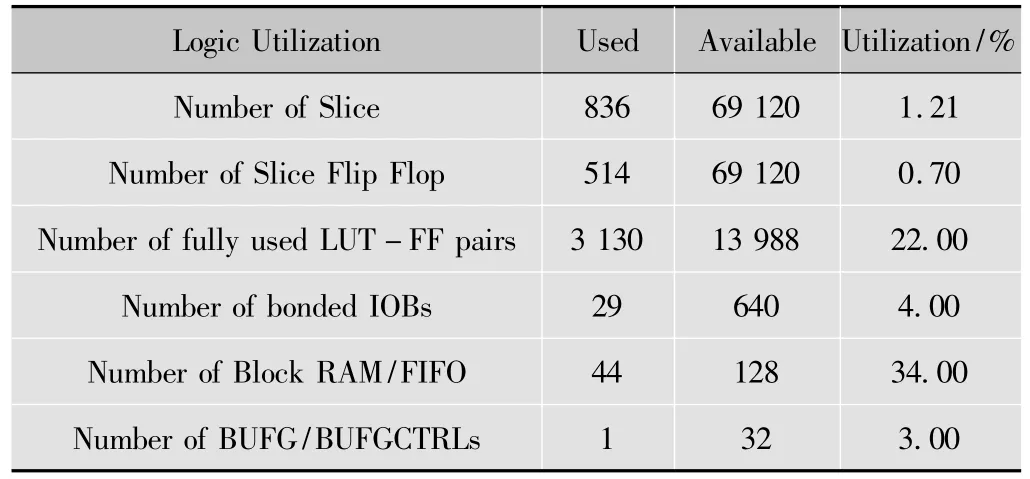

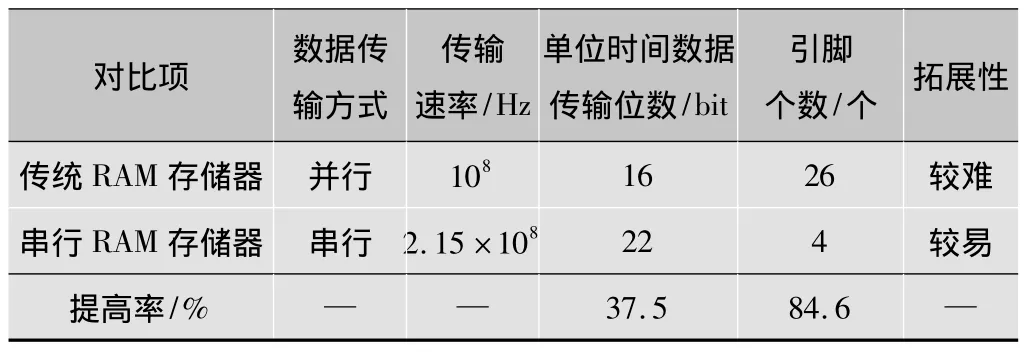

3.2 资源使用情况和分析对比

由综合报告可知该RAM存储器资源占用情况,具体如表3。由Utilization一列可以清晰地看到,本文所设计的串行接口RAM存储器使用资源比较少,引脚个数节约了84.6%,非常有效地降低了SoC的空间和成本,同时数据传输速率提高了37.5%。表4中对比了传统RAM存储器与本文所设计的单向串行只写总线型RAM存储器,具体如下。

图5 RAM存储器接收CPU发送的写和读命令结果(截图)

图6 RAM控制器向CPU发送串行数据结果(截图)

表3 串行接口RAM存储器使用资源的情况

表4 RAM存储器对比

4 总结与展望

本文应用Xilinx Vertex-5开发板上丰富的FPGA资源,利用其高速工作特性,以及内嵌的单端口RAM IP核,构造并实现了具有单向串行只写总线接口的RAM存储器,并采用LVDS技术抑制高速信号间干扰,大大提高了数据的传输速率与可靠性。通过下载验证,该存储器的设计方案正确,灵活性很高,可以很方便地进行扩展[8]。RAM为可配置软IP核,其存储容量可以根据需要定制。嵌入式CPU可以通过增加RAM节点个数形成存储阵列来达到扩展缓存容量的目的,因此在单位时间内可以访问更大的内存,处理更大规模的数据,从而加快其访问内存的速度。FPGA具有硬件逻辑可编程性、大容量、高速、内嵌存储阵列等特点,使其特别适合于高速数据采集、精确时序逻辑等场合的应用[3]。

[1]李庆诚,刘嘉欣,张金.嵌入式系统原理[M].北京:北京航空航天大学出版社,2008.

[2]秦鸿刚,刘京科,吴迪.基于FPGA的双口RAM实现及应用[J].电子设计工程,2010(2):72-74.

[3]马玉春,宋瀚涛.串行通信协议的研究及应用[J].计算机应用研究,2004(4):228-232.

[4]Virtex-5 FPGA Data Sheet[EB/OL].[2013-10-30].http://wenku.baidu.com/link?url=AeiuPIDTJ-8xJnQ4wQuxAvDetu7FPi5qtsOFPw JUcXmGaCp85oy1RL8xEV2jqlgMS7tSkMuYL2bwc_RYy8XAkhF_jeYeM-hQwbqV8GQF-NSS.

[5]封彦彪,刘兴春.基于Xilinx FPGA的时钟管理设计与实现[J].电子测量技术,2010(10):52-55.

[6]张友,郑世宝.一种SPI滤波器设计中的并行CRC算法[J].电视技术,2005,29(3):28-30.

[7]杜瑞,张伟功,邓哲,等.新型总线中并行CRC算法的设计与实现[J].计算机工程与设计,2013(1):131-135.

[8]田丰,邓建国,李巍,等.SDRAM控制器的设计与VHDL实现[J].电子技术应用,2005(2):74-79.