支持PCI总线的HDLC协议专用控制器设计

钱黎明,刘富发,魏敬和

(中国电子科技集团公司第58研究所,江苏 无锡 214005)

支持PCI总线的HDLC协议专用控制器设计

钱黎明,刘富发,魏敬和

(中国电子科技集团公司第58研究所,江苏 无锡 214005)

在地面卫星通讯中,为了满足上位机更快、更可靠的接收外部设备通信数据的要求,设计了一款支持外围部件互联(PCI,Peripheral Component Interconnect)总线的高级数据链路控制(High-level data link control,HDLC)协议专用控制器电路。详细描述了电路系统构成及具体模块的实现,并给出了仿真波形图。经仿真测试表明该电路可满足系统要求,同时PCI接口速率可达到132 Mbyte/s。

高级数据链路控制(HDLC);PCI总线;控制器

0 引 言

在地面卫星通讯领域中,大型地面通讯设备的测试数据具有传输量大、实时性要求高的特点。为了解测试设备与上位机的通信状况,需采用一种大容量高速传输的通信协议,实现数据传输过程的完全透明。设计了一款支持PCI总线的高级数据链路控制(HDLC,high level data link control)协议专用控制器,除了能够满足高速度、透明传输的要求,同时还具有差错控制、同步传输、功耗低等优点,能够应用于任何高速数据传输系统中。

1 PCI和HDLC协议简介

1.1 PCI总线概述

PCI总线是一种传输速率可高达132Mb ytes/s的高速局部外设总线,可应用在高速率和低功耗领域。该总线共有100根信号,当PCI接口作为从设备时最少应有47根,作为主设备时最少应有49根[1]。根据实际应用场合实现最基本的功能,根据信号功能可将总线信号大致分为系统信号、数据地址信号、控制信号、中断、仲裁及错误等几类。其中系统信号为CLK、RST;数据地址信号为AD、C/BE、PAR;控制信号包括FRAME、IRDY、TRDY、STOP、LOCK、ID+ SEL、DEVSEL,下面主要采用上述信号进行PCI接口通信研究设计。

1.2 HDLC协议简介

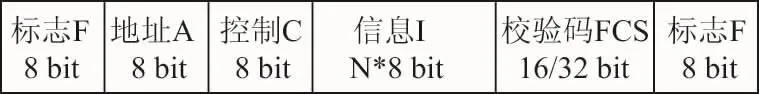

HDLC协议是在通信链路层中应用较广泛的协议,所有数据均以信息帧的形式传送,采用面向比特型规程使其具有强大的差错检测功能和高可靠、高效率透明传输的特点,该协议适用于中高速同步半双工和全双工通信领域中。典型的HDLC信息帧结构,如图1所示。

图1 HDLC帧结构

根据HDLC协议规定,所有信息帧必须以标志字“0x7E”开始和结束。接收设备不断的搜寻“0x7E”以实现帧同步,从而确定一帧的开始和结束。另外,在帧与帧的空载期间,可以连续的发送标志序列用作时间填充[2,3]。地址字段表示链路上站的地址,当站点较多时,可按字节进行扩充。控制字段表示帧类型、帧编号及命令等,也可按字节进行扩充。信息字段包含用户的数据信息和来自上层的各种控制信息。帧校验序列采用循环冗余校验(CRC)对地址、控制、信息字段进行差错控制。

在一帧数据中,HDLC协议采用“0”比特插入技术,地址、控制、信息、校验码字段中有可能出现与标志字相同的字节,为了保证标志字的唯一性,在发送除标志外的其它信息时,只要遇到连续5个“1”,在其后自动插入一个“0”。反之,在接收方遇到连续5个“1”,自动删除其后的“0”[4]。采用上述操作可实现任何代码的传送,即实现传输的透明性。

HDLC协议中加入帧校验序列来保证数据传输的可靠性,采用循环冗余校验码对所传送的数据进行检错和纠错,校验范围包括地址、控制、信息字段。HDLC规程规定了三种长度帧校验序列,即8位、16位、32位,设计中采用16位帧校验序列,对应CRC校验码的生成多项式[5]为:

P(X)=X16+X12+X5+1

2 HDLC专用控制器电路设计

HDLC协议控制器的系统框图如图2所示。电路工作在数据接收状态时,首先经过接收处理模块处理,当CRC校验正确后,数据经过串并转换后传送给FIFO,然后经过DMA方式读取后通过PCI接口传送给上位机;电路工作在数据发送状态时,首先上位机通过PCI传输控制模块将数据传送给接收FIFO,然后数据并串转换后分两路,一路进入发送处理模块进行数据的发送,另一路经过CRC模块生成CRC校验码,而后附加在数据通路进行发送。其中根据实际应用接收FIFO和发送FIFO大小均为128双字节,通过FIFO电路实现HDLC串行数据和PCI总线并行数据的交互;控制模块实现对其它模块的控制,仅在其它模块电路需要工作时才将其打开,从而达到降低功耗的目的;由于CRC校验和生成机理相似,因此在CRC校验/生成模块通过电路的复用实现差错控制,从而降低电路的功耗和减小电路的面积。HDLC协议处理部分的工作时钟由外部晶振时钟经过振荡器、波特率产生器、数字锁相环后产生的稳定时钟提供,PCI传输控制模块时钟由PCI总线提供。

图2 HDLC控制器系统框图

2.1 数据接收处理

接收处理模块由同步模块、帧头检测、比特解码、数据接收缓冲等模块电路构成,主要采用状态机完成HDLC协议数据的接收,电路状态转换图如图3所示。由于采用外部时钟作为工作频率,且HDLC协议为面向比特型,因此首先采用同步模块对接收数据作同步处理,防止亚稳态产生,提高电路的可靠性。其次进入状态机进行帧头检测,当检测到“0x7E”,开始数据的接收处理。同时比特解码模块开始检测,当检测到连续5个“1”时,产生去0标志,数据接收缓冲模块舍弃下一位的接收;CRC校验模块进行数据校验,当CRC接收完成之后进行CRC校验码的比较,若校验码正确则进入帧尾的检测。此时若检测到“0x7E”则完成一帧数据的接收操作。

2.2 数据发送处理

发送处理模块包括数据发送缓冲、帧标志生成、比特编码等模块电路构成。该过程即为数据接收处理的逆过程,同样采用状态机实现HDLC协议数据的发送,状态转换图如图4所示。当检测到上位机传来的帧发送标志时,开始一帧数据的发送,该模块从发送FIFO读取发送数据,然后依次完成帧起始标志、数据段、CRC校验码、帧结尾标志的发送,在数据发送期间使用比特编码模块对数据进行“0”填充编码。同时该模块在帧与帧的空载期还可连续发送帧标志,作为时间填充。

图3 HDLC接收模块状态机

图4 HDLC发送模块状态机

2.3 PCI接口设计

该模块电路核心部分为状态机设计[6,7],通过状态机接收并判断PCI总线上的信号确定当前状态,从而控制PCI存储器、I/O口、配置寄存器的读写和中断等主要操作。本文根据PCI总线时序逻辑定义状态机各个状态从设备状态转换图,如图5所示。该状态机共分为11个状态,分别为idle、rw_ wait1、rw_wait2、read_wait、rd_wr、last_rw、configwait1、configwait2、config、return和abort。主设备通过仲裁后选定从设备并开始通信;从设备地址译码匹配时,开始转入数据处理操作,可进行配置寄存器操作、IO/存储器的一次读写、猝发读写,以及中止传输等操作。当用户要求中止传输且Frame无效时,状态机通过return状态转到初始状态idle。

2.4 仿真和验证

图5 PCI状态转换图

采用VerilogHDL语言[8]进行了电路设计,使用VCS、DC、Encounter、Calibre等EDA工具进行电路的功能仿真、逻辑综合、布局布线和物理验证等设计。设计需对PCI配置方式迸发数据传输、PCI配置方式单个数据传输、PCI存储器方式迸发数据传输、PCI存储器方式单个数据传输、基于HDLC协议的数据发送和接收等过程进行仿真验证。

基于HDLC协议的数据发送时序如图6所示,复位后,PCI工作在从模式,FRAME拉低表示PCI一帧数据开始传输,IDSEL拉高使得PCI工作在配置方式,对PCI总线控制器内部的命令/状态、基址等寄存器进行配置;IDSEL拉低使得PCI工作在存储器方式,对HDLC协议控制器内部的全局、中断队列、中央FIFO、发送FIFO、时钟模式、发送时钟波特率、中断使能/屏蔽、发射器复位、发射描述符、请求发射等寄存器进行配置;PCI切换到主模式,根据发射描述符中的基址信息,通过DMA方式从外部存储器将要发送的数据读入内部发送FIFO,经过HDLC协议处理后以串行的方式从TXD1发送出去。

基于HDLC协议的数据发送和接收时序如图7所示,接收采用闭环方式,即接收发送端TXD1的串行输出数据,经过HDLC协议处理后,32位的并行数据写入接收FIFO中,PCI通过DMA的方式将接收到的数据存入外部存储的另一段地址空间,地址空间以及长度由接收描述符决定。

图6仿真波形表明,PCI数据传输速率132Mbyte/s,外部存储空间的数据可以被 PCI以DMA的方式读取,经过HDLC协议处理后,以串行的方式发送出去;图7仿真波形表明,外部存储空间的数据可以被PCI以DMA的方式从一块地址空间拷贝到另一块地址空间,即基于HDLC协议、数据能被正确的发送和接收。

图6 数据发送时序

图7 数据发送与闭环接收时序

2.5 整机实装测试

HDLC协议专用控制器电路采用四面引脚扁平方式封装,HDLC串行通讯模块板卡贴装了2片HDLC协议专用控制器电路,位于板卡的最左侧,如图8所示。

图9 整机实装

图8 HDLC串行通讯板

2块HDLC串行通讯模块板卡插入主机架,和其他模块板卡一起构成整机系统,如图9所示。

系统测试数据流如下,处理器通过北桥电路扩展出PCI总线,通过接插件,并行信号进入HDLC串行通讯模块板卡,通过PCI桥电路扩展出2路PCI分别接到2只HDLC协议专用控制器电路上,经过HDLC协议处理与组帧后变为串行数据,串行数据经过光藕电路隔离后从接插件输出,信号离开HDLC串行通讯模块板卡进入后IO板卡输出到外部设备。

实测结果通过串口上报给上位机,与HDLC协议专用控制器电路相关的测试结果从序号133开始到161结束,如图10所示。进行了下列类别的功能实测:PCI配置方式迸发数据传输、PCI配置方式单个数据传输、PCI存储器方式迸发数据传输、PCI存储器方式单个数据传输、基于HDLC协议的数据接收、基于HDLC协议的数据发射。测试结果证实了从前向通道输入的132 Mbyte/s并行输入数据,经过HDLC协议专用控制器电路处理后,输出了25 Mbit/s的串行数据;反之,25 Mbit/s的串行输入数据,经过专用控制器电路处理后,得到132 Mbyte/s的并行输出数据。2块HDLC串行通讯模块板卡共扩展出了4路通道,100 Mbit/s的串行数据吞吐率了满足了整机系统对带宽的要求。

图10 实测结果

3 结 语

为了满足地面卫星通讯等高速数据传输领域的要求,设计了一款支持PCI总线的HDLC协议专用控制器电路,PCI接口速率可达到132Mbyte/s,该电路可实现上位机和外部通讯设备数据的高速、透明传输,已成功应用于整机系统中。

[1]PCISpecial Interest Group.PCI Local Bus Specification Revision2.3[S].2001.

[2]ISO/IEC 13239,Information Technology+Telecommunica tion Exchange between Systems+High+Level Data Link Control(HDLC)Procedures[S].Switzerland:Jul,2002.

[3]应三丛.基于FPGA的HDLC协议控制器[J].四川大学学报:自然科学版,2008(40):116+120.

[4]谢希仁.计算机网络[M].第二版,北京:电子工业出版社,1999.

[5]HENRIKSSON T,LIU DAKE.Implementation of Fast CRC Calcul+ation[C]//Proceedings of t he Asia and South Pacific,DesignAutomatation Conference.2003:563+564.

[6]FAWCETT B K.DESIGNING PCIBus InterfaceswithPro+ grammable Logic[C].//Proceedings of the Eighth Annu+ al IEEE International,1995.321+324.

[7]张炜,沈德刚.基于FPGA的PCI总线接口设计与实现[J].计算机与数字工程,2009,37(5):174+177.

[8]IEEE.Hardware Description Language Based on the Ver+ ilog Hardware Description Language[S].IEEE Std 1364+1995,1955.

E+mail:limingic@163.com

刘富发(1987—)男,河南濮阳人,硕士,主要研究方向为ASIC设计;

魏敬和(1971—)男,安徽安庆人,博士,主要研究方向为系统芯片SoC设计。

Design of HDLC Protocol Controller w ith PCI Bus

QIAN Lin+ming,LIU Fu+fa,WEIJing+he

(The 58th Research Institute of CETC,Jiangsu Wuxi214005,China)

In terrestrial satellite communications,in order tomeet the demands of the faster PC andmore reliable receive external communicationdata,a high+level data link control(HDLC)Protocol Controller with Peripheral Component Interconnect(PCI)bus is designed.The structure of circuit system and the achieved of specific modules are described and the simulation waveforms is given.The simulation tests show that the circuit can meet the system requirements and PCI interface rates up to 132 Mbyte/s.

HDLC;PCIbus;controller

TN47

:A

:1673+5692(2014)06+648+05

钱黎明(1981—),男,安徽芜湖人,硕士,主要研究方向为系统芯片SoC设计;

10.3969/j.issn.1673+5692.2014.06.019

2014+08+19

2014+10+24