基于FPGA的机载显示系统架构设计与优化※

吴连慧,周建江,夏伟杰,陈雅雯

(南京航空航天大学 电子信息工程学院,南京210016)

引 言

现代机载视频图形显示系统对于实时性等性能的要求越来越高。常见的系统架构主要分为3种:

①基于GSP+VRAM+ASIC的架构[1]。优点是,图形ASIC能够有效提高图形显示质量和速度;缺点是,国内复杂的ASIC设计成本极高且工艺还不成熟。

②基于DSP+FPGA的架构[2]。优点是,充分发挥DSP对算法分析处理和FPGA对数据流并行执行的独特优势,提高图形处理的性能;缺点是,上层CPU端将OpenGL绘图函数封装后发给DSP,DSP拆分后再调用FPGA,系统的集成度不高,接口设计复杂。

③基于FPGA的SOPC架构[3]。优点是,集成度非常高;缺点是,逻辑与CPU整合到一起,不利于开发。

经过对比,机载视频图形显示系统的架构设计可优化空间,值得进一步深入研究,从而设计出实时性更高的方案。

本文设计一种基于FPGA的图形生成与视频处理系统,能够实现2D图形和字符的绘制,构成各种飞行参数画面,同时叠加外景视频图像。在保证显示质量的同时,对其进行优化,进一步提高实时性,减少内部BRAM的使用,降低DDR3的吞吐量。

1 总体架构设计

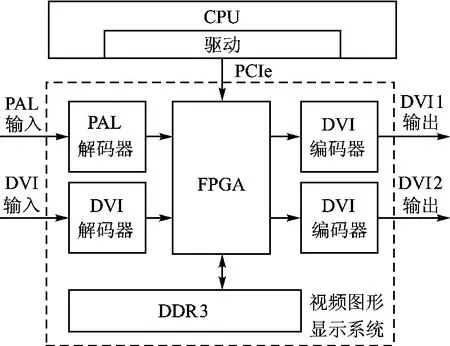

本系统总体设计方案如图1所示。以Xilinx的Kintex-7 FPGA为核心,构建出一个实时性高的机载视频图形显示系统。上层CPU接收来自飞控、导航等系统的图形和视频控制命令,对数据进行格式化和预处理后,通过PCIe接口传送给FPGA。本文主要是进行FPGA内部逻辑模块的设计和优化。

图1 机载显示系统总体设计框图

2 机载显示系统架构设计

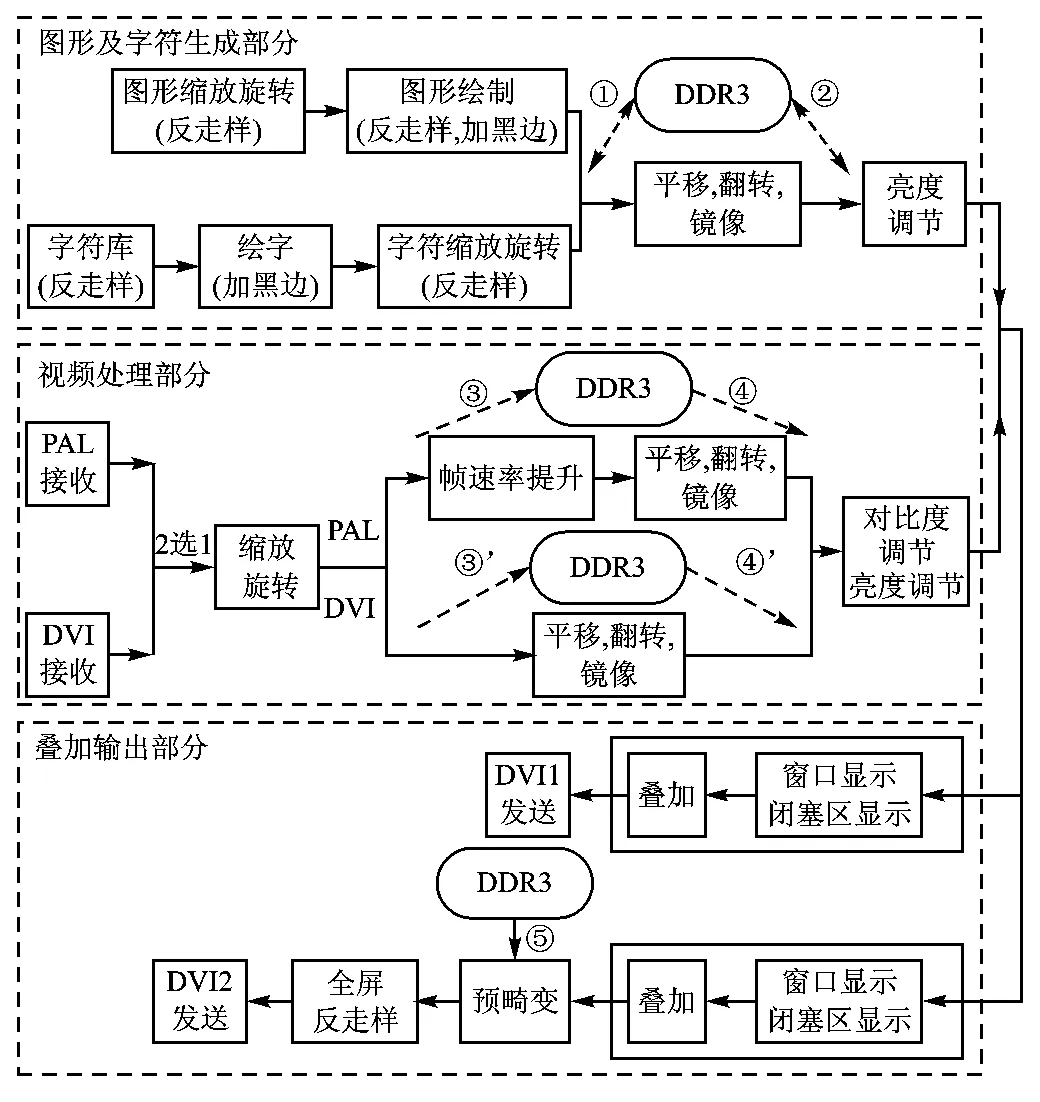

机载显示系统设计主要包括2D绘图、视频处理和叠加输出。2D绘图功能包括直线、圆、字符等的快速生成。视频处理功能包括输入视频选择、视频缩放、旋转、翻转等处理。叠加输出功能,将视频作为背景与图形叠加,送到两路DVI输出,一路经过预畸变校正后输出到屏显上,另一路直接输出来进行地面记录。

为了实现上述功能,FPGA逻辑设计的整体流程图如图2所示。

图2 FPGA逻辑设计的整体流程图

2.1 实时性分析

视频处理既要实现单纯的外视频处理,同时又要能够实现叠加后视频处理。以旋转处理为例,若在单纯外视频旋转处理后,与图形叠加,再进行叠加后旋转处理,延迟非常大。因此为了提高实时性,考虑将图形整体和外视频分别进行旋转处理后,再相互叠加。整个流程中,帧速率提升模块延迟最大。

帧速率提升指在原有的图像帧之间插值出新的图像帧。常见的帧速率提升算法[4]主要包括帧复制法、帧平均法和运动补偿法。综合考虑显示效果和实时性要求,最终选择帧复制法。帧复制法易于实现、计算量小。其表达式为:

此处输入PAL视频帧速率为25帧/s,输出DVI视频帧速率为60帧/s,即在0.2 s内将5帧图像插值到12帧。如图3所示,DDR3中开辟5帧存储空间用于存放25 Hz的原始图像,在0.2 s内输入5帧原始图像,输出12帧图像。延迟为PAL的1.5~2.6帧,最大延迟为2.6×(1/25 Hz)=104 ms。

图3 帧速率提升示意图

2.2 BRAM资源占用

机载显示系统利用1片DDR3作为外部存储器,所有图形和视频数据都需要缓存到DDR3中。为了解决数据存储冲突,需要将数据先缓存到内部BRAM中。XC7k410T共有795个36 Kb的BRAM。整个流程中,BRAM资源占用最大的是图形整体旋转和视频旋转模块。

视频旋转包括两个基本操作[5]:空间坐标变换和灰度级插值。灰度级插值算法选择双线性插值,此处重点讨论空间坐标变换的选择。空间坐标变换主要包括两种:正向映射和反向映射。由于正向映射旋转后得到浮点坐标,而图像坐标是整点,使得旋转图像存在“空洞”现象,因此采用反向映射。反向旋转映射算法的思想是:对旋转后的每行每个像素坐标(x′,y′)进行遍历,绕屏幕中心(x0,y0)沿逆时针旋转-θ角度后,得到旋转前图像坐标(x,y)。(x′,y′)与(x,y)之间的反变换公式为:

反向旋转映射的优点是,旋转后坐标反向旋转,除了超出原始坐标范围的,在旋转前坐标中都能对应到浮点坐标,并可以用该坐标邻域的像素点来唯一确定该坐标的像素值,不会出现“空洞”现象。

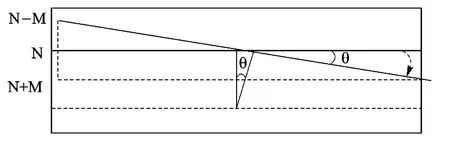

图4 视频旋转算法示意图

充分考虑项目的特殊情况,由于项目中旋转是用来校正屏幕的,旋转角度范围是-10≤θ≤10。如图4所示,对旋转后目标图像的第N行进行反向旋转获取坐标时,原始坐标在N-M~N+M行之间。分辨率为1920×1080且角度为10°时,M 为1920/2×sin(10π/180)=167行,即当计算输出第N行时,需要知道原始图像的N-167~N+167行来获取,即需要缓存334行,每行需要1920×16=30 Kb,即一共需要279个36 Kb的BRAM。

2.3 DDR3吞吐量分析

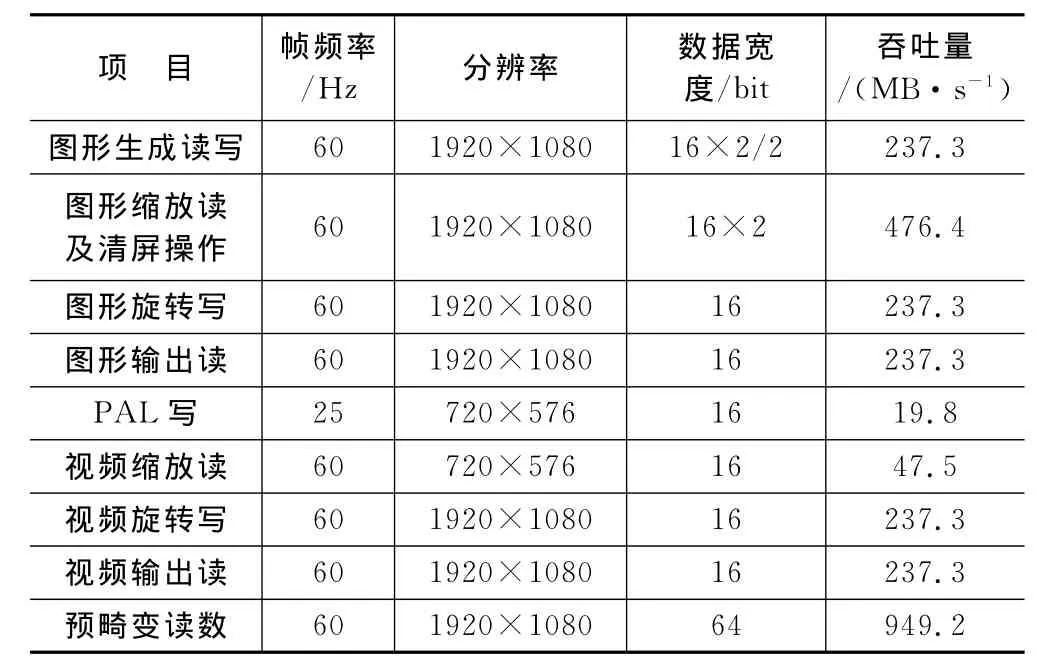

本系统处理的数据量大,FPGA内部的存储资源无法满足数据存储要求,需要配置系统外部存储器DDR3[6]。从图2可以看出,整个系统流程最多经过DDR3共9次。每次读写DDR3的必要性和数据量略——编者注。

表1为该系统数据吞吐量的汇总表,其吞吐量合计为2 677.6 MB/s。

表1 系统数据吞吐量汇总表

本设计采用DDR3作为系统外部存储器,其型号为W3H128M72E,数据宽度为72位(64位为数据位,8位为校正位),采用的时钟频率为400 MHz。由于DDR3在上升沿和下降沿都进行数据的读写操作,等效于其内部读写时钟频率为800 MHz,即数据带宽为6400 MB/s(800 MHz×64位),满足设计系统的数据吞吐量要求。

3 机载显示系统架构优化

设计的机载显示系统架构能够满足性能要求,但是还需要进一步优化。如图5所示,改变不同模块之间的顺序来优化设计,同时改进算法。具体改变如下:

①图形整体相对于屏幕的缩放和旋转功能在CPU端发送命令前实现。因为CPU端旋转和缩放是针对顶点进行的,方便快速,同时减少了FPGA的BRAM资源占用,也减少了进出DDR3的次数。

②改进帧速率提升算法,进一步减少延迟,提高实时性。

③改进视频旋转算法,进一步减少缓存区的大小,降低BRAM的占用率。

④帧速率提升和平移、翻转、镜像都需要通过读写DDR3来完成,将两者合并,同时完成,减少进出DDR3的次数。

图5 FPGA逻辑优化的整体流程图

3.1 实时性分析

实时性是机载显示系统重要的衡量标准之一。为了确保飞机运行安全,必须确保视频处理的各个模块都有较高的实时性。视频采集、视频缩放、视频校正、视频输出延迟都是几行,延迟时间在0.1 ms以内。帧速率提升模块的延迟远大于其他各个模块延迟之和,需要进一步改进,在保证显示质量的同时,进一步缩短延迟时间。

改进的帧速率提升算法仍使用帧复制法。在DDR3中,开辟4个存储空间做切换,用于存放帧速率为25 Hz、场速率为50 Hz的PAL图像。有4个场缓存区,当接收当前帧的奇场后与前一帧的偶场结合成一帧数据输出。

图6 帧速率改进算法示意图

帧速率改进算法示意图如图6所示。A场正好写完,B场正好读完,下一帧读取A场数据,这样延迟为PAL的1场(半帧);A场正好还差1行写完,B场已读完,下一帧继续读B场,这样延迟为PAL的1+(25/60)=1.42场。延迟为PAL的1~1.42场。最大延迟为1.42×(1/50 Hz)=28.4 ms。

3.2 BRAM资源占用

原设计的机载显示系统架构使用反向映射的方法实现旋转算法,每一行旋转后数据反向旋转时需要缓存334行视频旋转前数据,即需要279个36 Kb的BRAM。相对于其他模块缓存几行相比,占用了大量的BRAM空间,因此需要改进。

视频旋转算法优化的方法是,提出一种改进的旋转映射法,降低缓存空间,示意图如图7所示。对以行扫描的方式获取的视频图像,缓存两行就能开始旋转处理。先进行正向映射,根据当前两行对应的旋转后浮点坐标,找到两行内的整点坐标,再对其进行反向映射,利用当前两行来得到旋转后整点坐标的像素值。

图7 视频旋转改进算法示意图

该算法涉及原始图像中的2×2大小邻域,为了提高该模块的处理速度,设计了1组由3个双端口块存储器BRAM组成的原始图像数据缓存器。每个BRAM用来存储一行原始图像的数据,3个BRAM中存储的原始图像数据包括当前旋转计算涉及的2行原始图像数据以及下一行旋转计算涉及的1行原始图像数据。因此,需要缓存3行,使用3个36 Kb的BRAM。

3.3 DDR3吞吐量分析

从图5可以看出,优化后的系统流程最多经过DDR3共5次。每次读写DDR3的必要性和数据量略——编者注。

表2为该系统数据吞吐量的汇总表,其吞吐量合计为2 135.7 MB/s。DDR3 的 数 据 带 宽 为 6 400 MB/s(800 MHz×64 bit),满足本设计系统的数据吞吐量要求。

表2 优化后系统数据吞吐量汇总表

结 语

本文设计一种基于FPGA的机载显示系统架构,能够实现2D图形绘制,构成各种飞行参数画面,同时叠加外景视频图像。实时性方面,帧速率提升模块延迟最大为104 ms;BRAM资源占用方面,视频旋转算法需要279个36 Kb的BRAM;DDR3吞吐量方面,系统吞吐量为2 677.6 MB/s。

优化后的机载显示系统,实时性方面,帧速率提升模块延迟最大为28.4 ms;BRAM资源占用方面,视频旋转算法需要3个36 Kb的BRAM;DDR3吞吐量方面,吞吐量为2135.7 MB/s。

经过对比分析,优化后的机载显示系统实时性提高、BRAM资源占用减少、吞吐量降低,整体性能得到了提升。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1]Bailey D C.F-22 cockpit display system[C]//SPIE's International Symposium on Optical Engineering and Photonics in Aerospace Sensing.Phoenix.AZ:International Society for Optics and Photonics,1994:157-165.

[2]李孟华,牛文生,裴静静.DSP+FPGA结构的嵌入式图形处理设计[J].航空计算技术,2013(1):120-122.

[3]谢军,杜黎明,史小白.用SoC实现视频图形引擎功能的研究[J].单片机与嵌入式系统应用,2002(10):23-26.

[4]张晓燕.基于FPGA的机载视频处理与图形生成系统设计与实现[D].南京:南京航空航天大学,2012.

[5]王滨海,许正飞,陈西广,等.图像旋转算法的分析与对比[J].光学与光电技术,2011,9(2):46-49.

[6]刘德保,汪安民.多核DSP芯片TMS320C6678的DDR3接口设计[J].单片机与嵌入式系统应用,2013,13(9):53-55.