倒装芯片封装技术概论

张文杰 朱朋莉 赵 涛 孙 蓉 汪正平

1(中国科学院深圳先进技术研究院 深圳 518055)2(香港中文大学 香港 999077)

倒装芯片封装技术概论

张文杰1朱朋莉1赵 涛1孙 蓉1汪正平2

1(中国科学院深圳先进技术研究院 深圳 518055)2(香港中文大学 香港 999077)

高密度电子封装正朝着小型化、高 I/O 密度、更好的散热性和高的可靠性方向发展,传统引线键合技术已经无法满足要求。先进的倒装芯片封装技术由于具有较高的单位面积内 I/O 数量、短的信号路径、高的散热性、良好的电学和热力学性能,在电子封装中被广泛关注。底部填充胶被填充在芯片与基板之间的间隙,来降低芯片与基板热膨胀系数不匹配产生的应力,提高封装的稳定性。然而,流动底部填充胶依赖于胶的毛细作用进行填充,存在很多缺点。为了克服这些缺点,出现了非流动底部填充胶,以改善倒装芯片底部填充工艺。文章回顾了倒装芯片封装技术的发展,阐述了流动和非流动底部填充胶的施胶方式和性质。

倒装芯片封装技术;封装工艺;流动底部填充胶;非流动底部填充胶

1 引 言

电子封装有零级封装、一级封装、二级封装和三级封装。封装主要是提供电流通路,对离开或进入芯片的信号进行分配,提高导热性、耗散器件工作时产生的热量,避免外界环境对芯片和器件的影响。随着微电子产业向轻量化、薄型化、小型化、I/O 端数的增加以及功能多样化的发展,传统的引线键合互连技术已不能满足高密度的要求,倒装芯片封装技术在这种情况下应运而生。倒装芯片封装技术是把裸芯片通过焊球直接连接在有机基板上。同时还需要底部填充胶(Underfill)填充在芯片与基板之间由焊球连接形成的间隙,将芯片、焊球凸点和基板紧紧地黏附在一起,即底部填充技术,来降低因芯片与基板热膨胀系数(Coefficient of Thermal Expansion,CTE)不匹配而在焊点上产生的应力,提高焊点的热疲劳寿命[1,2]。底部填充胶对提高电子封装的可靠性有着不可忽视的作用。

2 倒装芯片封装技术起源

在 1955—1960 年的分立晶体管时代,器件封装用的是热压焊技术。但热压焊过程中容易在焊点下面产生空洞,导致焊接强度降低、电阻增加,影响封装的可靠性。另外焊接完成以后必须密封在管壳里,封装成本会相当高。

于是,IBM 公司和贝尔实验室开始探索一些不用密封芯片的方法来避免这一问题。贝尔实验室为了防止焊点的腐蚀开始利用 SiN 作为钝化层对芯片表面保护,并采用细金线来互联[3]。而IBM 公司在芯片表面和铝布线上则用玻璃钝化层来密封,然后将芯片和基板通过在芯片表面电极区制作的焊球来连接[4-6]。IBM 公司和贝尔实验室都是用将芯片的工作面向下的倒扣形式与基板连接,然后在基板上进行电路布线并贴装无源器件,最后用硅胶对芯片灌封,这种器件倒扣封装的形式就是最早的倒装焊互联技术的雏形。IBM公司将上述倒装焊技术结构开始在 360 系统的固态逻辑技术混合集成晶体管器件上进行应用,被认为是最早的倒装芯片封装形式。

3 倒装芯片封装的技术优点

倒装芯片封装技术使芯片和封装间直接通过焊球连接,省去了引线连接,在芯片和封装间形成最短的连接通路,具备以下优点:赋予了封装组件良好的电气性能;具有较高的封装速度;几乎没有封装密度的限制,能够增加单位面积内的I/O 数量;减小了封装组件的尺寸和重量;提高了信号完整性,频率特性更好;倒装凸点等制备基本以圆片、芯片为单位;与单根引线为单位的引线键合互连比较,生产效率高,降低了批量封装的成本等。它迎合了微电子封装技术追求更高密度、更小尺寸、更快处理速度、更高可靠性和更经济的发展趋势。

4 倒装芯片底部填充工艺

4.1 传统倒装芯片的底部填充工艺

早期的倒装芯片封装主要用陶瓷材料作为基板。陶瓷基板与芯片有相近的热膨胀系数,可以避免二者在运行过程中因热膨胀系数不匹配而产生较大的热应力对焊球的损害,但陶瓷基板的制作成本太高,使它的使用受到限制。纯硅基板则由于工艺原因限制了信号过桥的增加,并且纯硅基板里薄膜铝布线较大、线路较长,这些都限制了它的使用。目前倒装芯片封装中一般采用价格低廉的有机材料做基板。

使用有机基板时,一个突出问题是硅芯片与有机基板材料的热膨胀系数相差较大。芯片的CTE 约 3 ppm/℃,而基板的 CTE 约为 17~20ppm/℃,在芯片使用过程中,有机基板材料较硅芯片会产生更大的膨胀和收缩变形,会对焊球造成损坏,严重地影响芯片与基板连接的可靠性。

倒装焊技术中最具创新性的发展是有关底部填充技术的开发与使用。由此很好地解决了热膨胀系数不匹配而造成的可靠性问题,有机基板的使用成为可能。传统的底部填充技术是利用液体的毛细作用将底部填充胶(Flow Underfill)填充在芯片和基板之间的间隙中,然后在一定温度下固化。1987 年,Nakano[7]在环氧树脂基体中加入大量热膨胀系数更小的 SiO2颗粒,并填充在由焊球连接形成的芯片与基板之间的空隙,将焊点的热疲劳寿命提高了 10~100 倍,这就是最初的底部填充技术。随后,Tsukada 等[8]首次将硅芯片倒焊在 FR4 基板上,然后采用底部填充工艺对芯片、基板和焊球封装,提高了焊点的可靠性。随着底部填充胶的不断改进和提高,底部填充技术在电子产品的封装中也得到越来越广泛的应用。

传统的底部填充工艺如图 1 所示。先将一层助焊剂涂在基板上,然后将焊料凸点对准基板焊盘,加热回流,除去助焊剂,将底部填充胶沿芯片边缘注入,借助于液体的毛细作用,底部填充胶会被吸入并向芯片基板的中心流动,填满后加热固化。

目前,流动底部填充胶的组成主要有环氧树脂、球型氧化硅、固化剂促进剂和添加剂等。它除了能降低硅芯片、有机基板和焊球之间因 CTE不匹配而产生的应力和形变这一重要作用外,还可以增强倒装芯片的结构性能,防止芯片吸潮、离子污染、辐射以及其他不利的工作环境。对流动底部填充胶的性能要求主要包括:合适的流动性、固化温度低、固化速度快,树脂固化物无缺陷、填充后无气泡、耐热性能好、热膨胀系数低、玻璃化转化温度高、低模量、良好的粘接强度、内应力小和翘曲度小等。

在将底部填充胶填充到芯片和有机基板之间的狭缝的过程中,填充胶在芯片下的流速一直被认为是底部填充工艺中批量生产的瓶颈。填充胶的流动过程会直接影响到封装的可靠性,因此,了解影响底部填充胶流动性能的影响因素对倒装芯片封装工艺的优化设计和倒装芯片封装的可靠性分析具有重要的理论和经济意义。

图1 传统倒装芯片底部填充胶的填充工艺流程[9]Fig. 1. Flip-chip process using conventional underfill[9]

(1)底部填充胶施胶用量的计算

由于底部填充胶配置后通常需要低温保存,因此在底部填充胶施胶之前应首先确定底部填充胶胶水的用量。图 2 为用底部填充胶填充后的倒装芯片结构示意图。

底部填充胶胶水的用量可以用芯片底部的总体积减去凸点的体积计算。如下式所示:

其中,V 为底部填充胶总量,Vc为芯片与基板间的体积,Vb为总凸点的体积,Vf为底部填充胶固化后在芯片周围形成圆角(Fillet)的体积。

(2)填充时间的计算

底部填充胶主要靠液体的毛细作用填充到芯片和基板之间,提高液体的流动速度,降低底部填充所用的时间可有效的降低制造成本。底部填充胶填充长度为 l,所用的时间 t,可以通过Hele-Shaw 公式算出[11]:

其中,h 为芯片与基板的间距,θ 为底部填充胶在残留有助焊剂的基材上的接触角,γ 为底部填充胶液/空界面的表面张力,η 为底部填充胶的粘度。

依据公式(2),底部填充胶填充的时间与芯片长度的平方以及底部填充胶的粘度成正比,与底部填充胶的表面张力成反比,与空隙大小成反比。倒装芯片发展的趋势是芯片尺寸将不断增大,而芯片与基板之间的间隙越来越小。因此,为了减少底部填充胶填充所需的时间,提高底部填充胶的流动性,降低其粘度是至关重要的。

(3) 基板温度的控制

底部填充胶的流动性同时也受倒装芯片封装体温度的影响。填充过程中需对芯片和基板进行预热,使其保持在一定温度范围内,以提高胶水的流动性、缩短填充时间。另外,加热速率不能太快,否则封装体由于热膨胀而产生较大的应力。同时要避免对盛放底部填充胶的容器加热,以提高胶的使用寿命。

虽然传统的流动型底部填充是目前主要的倒装芯片封装技术,但它也面临着各种新的挑战。目前,互连技术向无铅焊料方向发展,意味着底部填充胶需要适应更高的回流焊温度。而高的回流焊温度会加速材料的老化和水分的进入,引起更大的机械膨胀,所以底部填充胶需要更高的热稳定性、粘结力、强度和断裂韧性。另外随着大尺寸芯片在倒装焊技术中的应用以及焊球高度的降低,使得芯片和基板间的间隙高度越小、长度越长,原有的毛细作用将使底部填充胶很难填满芯片和基板间的间隙,引起不完全充胶现象,同时增加充胶时间和成本。间距距离和间隙高度的持续减小将最终限制底部填充胶的毛细作用填充,传统的底部填充工艺也面临巨大的挑战。

图2 底部填充的倒装芯片结构示意图[10]Fig. 2. Configuration of a flip chip package with underfill[10]

4.2 倒装芯片的非流动底部填充胶填充工艺

为了克服传统毛细底部填充工艺的缺点,Wong 等[12-17]学者提出了非流动底部填充胶(Noflow Underfill)填充工艺。与传统毛细底部填充工艺相比,非流动填充不需要液体的毛细作用,它需将非流动底部填充胶在焊球回流焊之前铺好,接着在回流焊过程中同时完成焊球焊接和底部填充胶固化两个过程,省去了助焊剂分布和清除步骤,简化了工艺,提高了生产效率,其工艺流程如下图 3 所示。

非流动底部填充胶应该具备:在焊接过程中能够起到助焊剂的功能,胶的固化应晚于焊球焊点的形成;在后续的回流焊过程中能够固化完全等几个必要特点。

非流动底部填充胶通常不含有 SiO2无机填料,以避免 SiO2颗粒对焊点形成以及焊料和金属焊盘的浸润性造成影响。因此,与传统底部填充胶相比,非流动底部填充胶具有更高的热膨胀系数和低的断裂韧性,极易引起焊点、芯片、基板、胶之间的断裂失效。所以在非流动底部填充胶中加入 SiO2填料对提高封装可靠性也是非常重要的。在使用具有 SiO2填料的填充胶时,需要除去焊点周围的 SiO2填料,于是就开发出了热压回流焊(Thermo-Compression Reflow,TCR)技术[18],其步骤如图 4 所示。它是将底部填充胶放到预加热好的基板上,然后将芯片倒扣在基板上,在高温和一定的压力下保持一段时间,直到焊点形成,然后再进行固化,这样就避免了 SiO2填料对焊点造成的影响。

另一种改进方式是使用双层无流动底部填充(Double-layer No-flow Underfill)技术。首先在基板上铺展一层没有 SiO2的高粘度底填胶,对焊球形成保护,然后在上部铺展一层含有 SiO2填料的底填胶,将芯片放置到基板上后进行回流焊,形成焊点、固化底填胶,如图 5 所示。

图3 非流动填充工艺流程[12]Fig. 3. Flip-chip process using no-flow underfill[12]

图4 热压回流焊工艺流程[19]Fig. 4. Process of thermo-compression reflow for flip-chip[19]

虽然非流动底部填充胶具有很多的优势,克服了传统底充胶的一些缺点,但它需要更高的固化温度,在胶固化和温度循环过程中会产生更大的热应力,容易造成芯片碎裂。随着芯片越来越大且越来越薄,这个问题会更加突出。

总之,非流动底部填充技术极大地简化了倒装芯片底部填充工艺。为了能够填充具有 SiO2填料的底填胶,出现了热压回流焊和双层无流动底部填充技术,但这些方法与表面贴装技术不完全兼容,也没达到降低成本的目的。开发成功率较高的非流动底部填充工艺需要对材料和工艺参数进行更多更细致的研究。

4.3 晶圆级底部填充技术

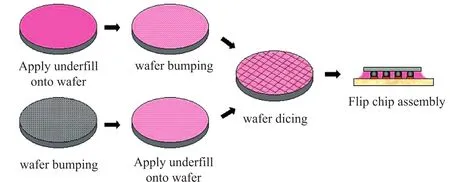

近年来,一种新的封装技术——晶圆级填充(Wafer Level Underfill),因其具有低成本、高可靠性,并且能够与表面贴装技术工艺兼容等特点,引起人们的广泛重视并得到了快速的发展。在该工艺流程中,它首先在晶圆上添加一层下填料,在晶圆上制作凸点,然后切成单个的芯片,芯片与基板通过表面贴装技术工艺相连,如图 6所示。

图5 双层非流动底部填充工艺过程[20]Fig. 5. Process of double-layer no-flow underfill[20]

图6 晶圆级填充流程[21]Fig. 6. Process of wafer level underfill

此工艺把半导体封装中前道和后道的一些工序都集合在了一起,同时随着晶圆级下填充工艺越来越广泛的应用,它需要芯片制造、封装公司以及材料供应商之间密切的配合。

5 三种底部填充工艺对比

与其他互连技术相比,倒装芯片封装技术有很多优点,并得到了广泛的应用。为了避免芯片和基板之间由于热膨胀系数不匹配而引起焊球的开裂,需要在芯片和基板之间填入底填料来提高封装的可靠性,所以下填充工艺是封装生产中的关键环节。较早使用的是传统的倒装芯片填充技术,但它靠液体的毛细管作用进行填充,已不能适应高速发展的封装技术的需求。一些新的填充技术像非流动底部填充技术、晶圆级填充技术等得到了开发和应用。

非流动底部填充技术不需要靠液体的毛细吸收作用进行填充,与传统底部填充工艺相比还简化了工艺步骤。但由于它不含有或含有很少的SiO2填料,所以非流动底部填充胶具有较高的热膨胀系数,降低了封装的可靠性。晶圆级填充技术成本低、可靠性高,把前道和后道的一些工序都集合在了封装工艺中,能够满足焊料凸点的节距、直径、高度的减小以及芯片厚度变薄等方面的发展要求。同时,晶圆级填充技术在芯片与基板之间利用硅通孔技术制作中介层,能够使芯片上细节距的焊盘与基板上较大节距的焊盘相连。带有中介层的 2.5D 或 3D 封装将能实现芯片封装更高的性能,是未来电子封装的发展趋势。

6 总 结

封装技术和封装材料是影响电子封装可靠性最重要的两个面因素,它们之间相互促进、相互制约,一方的发展都会对另一方起到推动作用。随着封装材料和封装技术的不断研究和创新,倒装芯片封装技术会在未来得到更广泛的应用。

[1] Wada M. Development of underfill material with high valued performance [C] // Proceedings of the 49th Electronic Components and Technology Conference, 1999∶ 56-60.

[2] Feustel F, Eckebracht A. Influence of flux selection and underfill selection on the reliability of flip-chips on FR-4 [C] // Proceedings of the 49th Electronic Components and Technology Conference, 1999∶583-588.

[3] Lepselter MP. Beam lead technology [J]. Bell System Technical Journal, 1966, 45(2)∶ 233-253.

[4] Davis EM, Harding WE, Sehwartz RS, et al. Solid logic technology∶ versatile high-perfonnance [J]. IBM Journal of Research and Development, 1964, 8∶102-114.

[5] Pliskin WA, Lehman HS. Structural evaluation of silicon oxide films [J]. Journal of the Electrochemical Society, 1965, 112(10)∶ 1013-1019.

[6] Totta PA, Sopher RP. SLT device metallurgy and its monolithic extension [J]. IBM Journal of Research and Development, 1969, 13(3)∶ 226-238.

[7] Nakano F, Soga T, Amagi S. Resin insertion effect on thermal cycle resistivity of flip chip mounted LSI devices [C] // Proceedings of the International Society of Hybrid Microelectronics Conference, 1987∶ 536-541.

[8] Tsukada Y, Tsuchida S, Mashimoto Y. Surface laminar circuit packaging [C] // Proceedings of the 42nd Electronic Components and Technology Conference, 1992∶ 22-27.

[9] Tong HM, Lai YS, Wong CP. Advanced Flip Chip Package [M]. USA∶ Springer, 2013.

[10] 李欣燕, 李秀林, 丁荣峥. 倒装焊器件的密封技术[J]. 电子与封装, 2010, 10(9)∶ 1-4.

[11] Han SJ, Wang KK. Analysis of the flow ofencapsulant during underfill encapsulation of flipchips [J]. IEEE Transactions on Components, Packaging, and Manufacturing Technology, Part B, 1997, 20(4)∶ 424-433.

[12] Wong CP, Shi SH, Jefferson G. High performance no-flow underfills for low-cost flip-chip applications∶material characterization [J]. IEEE Transactions on Components, Packaging, and Manufacturing Technology, Part A, 1998, 21(3)∶ 450-458.

[13] Shi SH, Wong CP. Study of the fluxing agent effects on the properties of no-flow underfill materials for flip-chip applications [J]. IEEE Transactions on Components and Packaging Technologies, 1999, 22(2)∶ 141-151.

[14] Lu JC, Smith B, Baldwin DF. Adhesion characterization of no-flow underfills used in flipchip assemblies and correlation with reliability [J]. IEEE Transactions on Electronics Packaging Manufacturing, 2001, 24(1)∶ 26-30.

[15] Luo SJ, Wong CP. Study on effect of coupling agents on underfill material in flip chip packaging [J]. IEEE Transactions on Components and Packaging Technologies, 2001, 24(1)∶ 38-42.

[16] Zhang ZQ, Shi SH, Wong CP. Development of noflow underfill materials for lead-free solder bumped flip-chip applications [J]. IEEE Transactions on Components and Packaging Technologies, 2001, 24(1)∶ 59-66.

[17] Thorpe R, Baldwin DF, Smith B, et al. Yield analysis and process modeling of low cost, high throughput flip chip assembly based on no-flow underfill materials [J]. IEEE Transactions on Electronics Packaging Manufacturing, 2001, 24(2)∶123-135.

[18] Miao P, Chew Y, Wang T, et al. Flip-chip assembly development via modified reflowable underfill process [C] // Proceedings of the 51st Electronic Components and Technology Conference, 2001∶ 174-180.

[19] Kawamoto S, Suzuki O, Abe Y. The effect of filler on the solder connection for no-flow underfill [C] // Proceedings of the 56th Electronic Components and Technology Conference, 2006∶ 479-484.

[20] Zhang ZQ, Lu JC, Wong CP. A novel approach for incorporating silica fillers into no-flow underfill [C] // Proceedings of the 51st Electronic Components and Technology Conference, 2001∶ 310-316.

[21] Pala RA, White J, Barnard E. Design of plasmonic thin-film solar cells with roadband absorption enhancements [J]. Advance Material, 2009, 21(34)∶3504-3509.

An Introduction to Flip-Chip Packaging Technology

ZHANG Wenjie1ZHU Pengli1ZHAO Tao1SUN Rong1WONG Chingping21

( Shenzhen Institutes of Advanced Technology, Chinese Academy of Sciences, Shenzhen 518055, China )2( The Chinese University of Hong Kong, Hong Kong 999077,China )

As the high density package is moving towards miniaturization, high I/O density, better thermal and high reliable system, the conventional wire bonding technology can not satisfy the product need already. The advanced flip chip technology is highly expected due to its high area array I/O interconnection, short signal path, high thermal dissipation, high electrical and thermal performance. In order to enhance the reliability of a flip-chip on organic board package, underfill is used between the chip and the substrate to redistribute the thermo-mechanical stress created by the coefficient of thermal expansion (CTE) mismatch between the silicon chip and organic substrate. However, the conventional underfill relies on the capillary flow of the underfill material and has many disadvantages. In order to overcome these disadvantages, no-flow underfill has been invented to improve the flip-chip underfill process. This paper reviews the development of flipchip technology and expounds the behavior of flow and no-flow underfill.

flip-chip packaging technology; flip-chip process; flow underfill; no-flow underfill

TN 305.94

A

2014-07-16

广东省引进创新科研团队计划(2011D052);深圳市孔雀计划团队(KYPT20121228160843692);深圳市电子封装材料工程实验室(深发改【2012】372 号)

张文杰,硕士,研究助理,研究方向为电子封装材料; 朱朋莉(通讯作者),博士,副研究员,研究方向为电子封装用无机纳米材料的制备与性能研究,E-mail:pl.zhu@siat.ac.cn;赵涛,硕士,高级工程师,研究方向为氧化硅纳米材料的制备与产业化;孙蓉(通讯作者),博士,研究员,研究方向为高密度电子封装材料与产业化,E-mail:rong.sun@siat.ac.cn;汪正平,美国工程院院士/中国工程院外籍院士,研究方向为聚合物纳米复合材料与高密度电子封装材料。