高速缓存单元原理及设计实现

孙佳佳,刘财坤

(中国电子科技集团公司第四十七研究所,沈阳110032)

高速缓存单元原理及设计实现

孙佳佳,刘财坤

(中国电子科技集团公司第四十七研究所,沈阳110032)

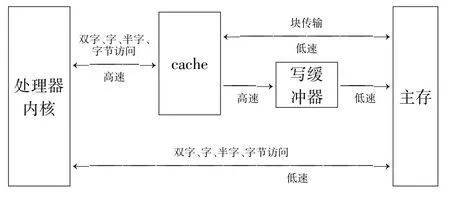

Cache是一种容量小、速度快的存储器阵列,位于主存和CPU内核之间,保存着最近一段时间处理器涉及到的主存块内容。为了改善系统性能,CPU尽可能从Cache中读取数据,减小慢速存储器给CPU内核造成的存储器访问瓶颈问题的影响。

高速缓存;处理器;主存

1 引 言

高速缓存(Cache),位于主存储器和CPU之间,用来提高存储系统的性能。高速缓冲存储器是全部用硬件来实现的,不仅对应用程序员是透明的,对系统程序员也是透明的。cache与主存储器之间以块(cache Line)为单位进行数据交换。当CPU读取数据或者指令时,同时将读取到的数据或者指令保存到一个cache块中。这样当CPU第二次需要读取相同的数据或指令时,可以从相应的Cache块中得到相应的数据或指令。因为cache的速度远远大于主存储器的速度,因此系统整体性能就得到很大提高。

图1 带cache的系统

2 Cache的工作原理

在cache存储系统中,把cache和主存储器都划分成相同大小的块。因此,主存地址可以由块号B和块内地址W两部分组成。同样,cache的地址也可以由块号B和块内地址W组成。当CPU要访问cache时,CPU送来主存地址,放到主存地址寄存器中。通过地址变换部件把主存地址中的块号B变换成cache的块号B,并放到cache地址寄存器中。同时将主存地址中的块内地址W直接作为cache的块内地址W装入到cache地址寄存器中。如果变换成功(称为cache命中),就用得到的cache地址去访问cache,从cache中取出数据送到CPU中。如果变换不成功,则产生cache失效信息,并且用主存地址访问主存储器。从主存储器中读出一个字送往CPU,同时把包含被访问字在内的一整块都从主存储器读出来,装入到cache中去。这时,如果cache已经满了,则要采用某种cache替换策略把不常用的块先调出到主存储中相应的块中,以便腾出空间来存放新调入的块。由于程序具有局部性特点,每次块失效时都把一块(由多个字组成)调入到cache中,能够提高cache的命中率。图2为cache工作原理图。

图2 cache工作原理

3 Cache的设计实现

3.1 地址映像方式设计

Cache一般多采用组相联映像设计方式。在组相联的地址映像和变换方式中,把主存和cache按同样大小划分成组(set),每一个组都由相同的块数组成。由于主存储器的容量比cache的容量大得多,因此,主存的组数要比cache的组数多。从主存组到cache组之间采用直接映像方式。在主存中的一组与cache中的一组之间建立了直接映像关系之后,在两个对应的组内部采用全相联映像方式。

3.2 替换算法设计

在把主存地址变换成cache地址的过程中,如果发现cache块失效,则需要从主存中调入一个新块到cache中。而来自主存中的这个新块往往可以装入到cache的多个块中。当可以装入这个新块的几个cache块都已经装满时,就要使用cache替换算法,从那些块中找出一个不常用的块,把它调回到主存中原来存放它的那个地方,腾出一个块存放从主存中调来的新块。替换算法一般有两种:随机替换算法和轮转法。

随机替换算法通过一个伪随机数发生器产生一个伪随机数,用新块将编号为该伪随机数的cache块替换掉。这种算法很简单,易于实现。但是它没有考虑程序的局部性特点,也没有利用历史上的块地址流分布情况,因而效果较差。同时这种算法不易预测最坏情况下cache的性能。

轮转法维护一个逻辑计数器,利用该计数器依次选择将要被替换出去的cache块。这种算法容易预测最坏情况下cache的性能。但它有一个明显缺点,在程序发生很小变化时,可能造成cache平均性能急剧变化。

3.3 结构设计

Cache有两个重要组成部分:Cache控制器和Cache存储器。Cache存储器是一个专用存储器阵列,它由3部分组成:目录存储段、状态信息段和数据项段,其访问单元称为Cache行,每一个Cache行都由这3部分组成。

Cache必须知道Cache存储器中每个Cache行所对应于每个主存中的位置,Cache使用目录存储段来记录每个Cache行是由主存的什么地方拷贝得来。该目录项就是Cache标签(tag)。同时,Cache存储器必须存储来自主存的信息,这些信息被存放在数据项段里。在Cache存储器里还有记录状态信息的状态位,比较常见的状态位是有效位(valid)和脏位(dirty)。有效位用来标记当前的Cache行是活动的,即有效的;脏位用来标记Cache行中所含的内容与主存中相应的内容是否一致。Cache结构如图3所示。

图3 Cache的结构

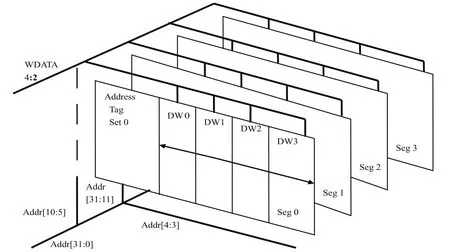

图4为以8Kb大小为例,每路cache有2Kb大小,每块(Line)cache有8字大小,所以每片cache的块(Line)数为64Cache。组相联Cache存储器的一般结构设计如图4所示。

Cache控制器是完全由硬件实现的,将主存中的数据或者代码自动拷贝到Cache存储器中,这个过程自动完成,对应用软件完全透明。

首先,读写存储器的请求在被传送到存储器控制器之前,会被Cache控制器截获,Cache控制器将该请求的地址信息分为3部分:标签域、组索引域和数据索引域,控制器通过组索引域在Cache存储器中确定可能包含所要求代码或数据的Cache行位置,Cache行中还包含标签和状态位,Cache控制器就是通过他们来确定数据的实际存储位置。

接下来,控制器检查有效位,以确定寻址到的Cache行是否有效,并且将请求地址的标签域值与Cache行的标签域进行比较,如果Cache行当前有效,并且标签域的比较结果相等,则Cache命中,否则Cache失效。在Cache失效的情况下,控制器从主存中拷贝整个Cache行到Cache存储器中,为CPU提供相应的代码或数据。Cache控制器的结构设计大致如图5所示。

图4 Cache存储器组相联的一般结构

图5 Cache控制器的一般结构

4 Cache功能验证

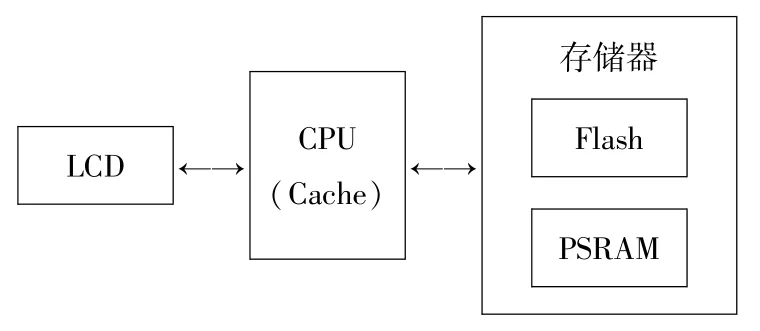

对于功能验证,采用的验证平台为能够组成的最小系统,连接CPU、Flash存储器、PSRAM存储器和LCD等部件。验证过程是在复位之后进入工作状态,将Flash中的程序搬运到PSRAM中,然后执行PSRAM中的程序。在程序运行过程中,通过开关Cache来验证Cache在系统中起到的作用。可以看到,在打开Cache之后,程序的运行速度明显加快。图6为验证平台结构图。

图6 验证平台结构框图

4 结束语

通过仿真验证,实现了cache的功能,结构合理。文中的设计思想,对带有cache的嵌入式CPU的设计,具有非常大的实用价值。

[1]Steve Furber.ARM SoC体系结构[M].田泽,于敦山,盛世敏,译.北京:北京航空航天大学出版社,2002.

[2]杜春雷,编著.ARM体系结构与编程[M].北京:清华大学出版社,2003.

Theory and Im plementation of Design on Cache

SUN Jia-jia,LIU Cai-kun

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

The cache,as amemory array with low capacity and high speed,is located between the main memory and CPU,which storages the latest contents of the main memory block processed by the processor.For improving the performance of storage system,CPU reads data or instructions from the corresponding Cache block to decrease the effect caused by the low speed of themain memory.

Cache;CPU;Main memory

10.3969/j.issn.1002-2279.2014.03.003

TN4

:B

:1002-2279(2014)03-0008-03

孙佳佳(1980-),女,辽宁沈阳人,工程师,主研方向:集成电路设计。

2013-12-27