深亚微米大容量PROM芯片ESD保护技术

裴国旭,邓玉良,樊利慧,李晓辉,彭锦军

(深圳市国微电子股份有限公司,广东 深圳 518057)

深亚微米大容量PROM芯片ESD保护技术

裴国旭*,邓玉良,樊利慧,李晓辉,彭锦军

(深圳市国微电子股份有限公司,广东 深圳 518057)

摘要:从全芯片角度出发,采用多电源ESD架构和全芯片ESD设计,对整颗芯片提供全方位的ESD保护,介绍了基于0.18 μm CMOS工艺设计的大容量PROM芯片的ESD设计技术。同时,通过对高压编程引脚的ESD加固设计,提高了芯片的整体抗ESD能力。最终产品ESD测试满足项目要求。

关键词:静电放电(ESD);可编程只读存储器(PROM);全芯片

在IC(集成电路)产业中,静电放电ESD(Electro-Static Discharge)是影响IC芯片可靠性的主要因素之一,通过ESD保护电路设计,可以提高IC芯片的可靠性[1]。ESD保护电路的保护强度可通过ESD测试来确定。在一款IC产品定型或出厂前都要经过ESD测试,以确定其可靠性[2]。

随着CMOS工艺尺寸的不断缩小,进入到深亚微米尺寸后,器件栅氧化层减薄,PN结变窄,导致器件击穿电压降低,性能易退化,可靠性降低。因此,深亚微米CMOS工艺的ESD保护设计受到更大挑战,需从全芯片的角度来设计优化ESD保护结构[3]。

本文首先介绍了深亚微米CMOS工艺ESD保护设计的基本概念和原理,接着阐述了基于0.18 μm CMOS工艺的大容量PROM芯片的全芯片ESD保护的设计方法,重点介绍了芯片中高压编程引脚的ESD保护设计和优化。样品通过了人体模型2 kV的测试。

1 深亚微米CMOS工艺中的ESD保护设计

CMOS工艺进入深亚微米后,受“等比例缩小”规则限制,随着器件尺寸缩小,栅氧化层不断减薄,为克服小尺寸器件严重的热载流子效应,设计了LDD结构。这些都导致了ESD保护器件抗ESD性能的退化。因此,深亚微米CMOS工艺中对ESD保护器件在工艺和结构上都做了优化和完善[4]。

1.1工艺优化

为提高深亚微米CMOS工艺中ESD保护器件的抗ESD性能,在深亚微米CMOS工艺中出现了一些新的工艺,如双栅氧工艺、ESD离子注入、扩散电阻及N阱电阻等。双栅氧工艺可以为ESD保护器件选用比内核器件更厚的栅氧化层,提高ESD保护器件的可靠性;ESD离子注入技术可以抑制器件的表面穿通,增强器件的抗ESD性能;扩散电阻可以限制发生ESD事件时器件内PN结上的峰值电流,防止PN结的击穿,而N阱电阻因为与衬底接触良好,散热性好,是ESD保护网络中重要的限流及隔离元件[4-6]。

在PROM芯片的设计中,我们主要采用了厚栅氧器件作为ESD保护器件。

1.2结构优化

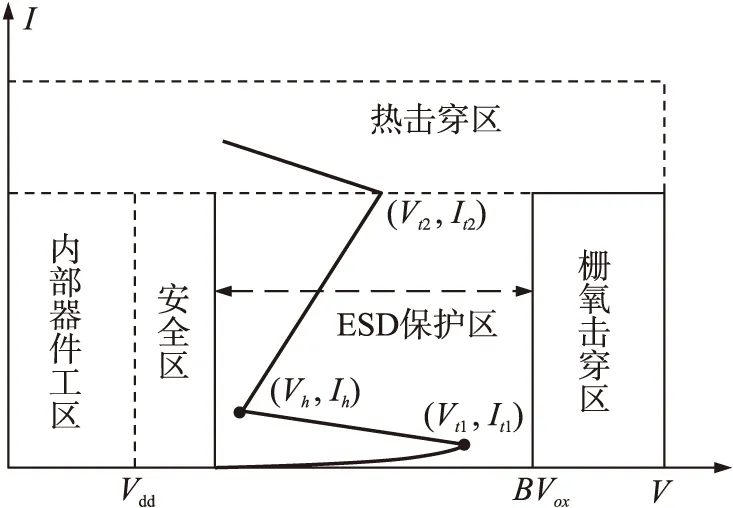

测试ESD器件的保护性能主要是测试器件的回扫特性。ESD保护器件的回扫特性曲线如图1所示。设计优良的ESD保护器件在ESD保护区内可承受多次的ESD应力,在ESD事件到来时,具有足够快的开启速度和足够低的导通电阻,使I/O端口的电压钳位,保护内部电路不受损伤。

图1 ESD保护器件回扫曲线

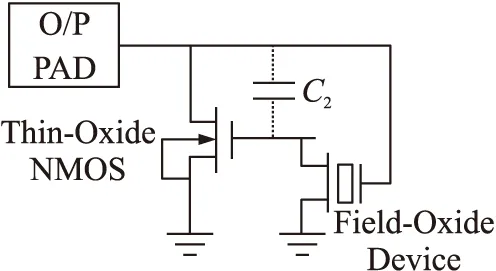

为提高深亚微米CMOS工艺中ESD保护器件的抗ESD性能,在CMOS器件结构上出现了一些新的技术,如改进的栅耦合技术、衬底和门级触发技术。常规的栅耦合技术采用RC网络,不但占用版图面积大,而且容易出现“过栅驱动”效应。改进的栅耦合技术是一种采用场氧器件和薄栅氧器件的动态栅耦合技术,如图2所示。在P型衬底上,集成了场氧器件和薄栅氧器件,发生ESD事件时,通过漏极-栅极寄生电容的耦合作用耦合到两器件,电压足够大时,场氧器件开启,通过薄栅氧器件迅速放电,场氧器件可以导通大电流,不会出现“过栅驱动”效应,同时利用器件本身寄生电容进行耦合,有效减小了版图面积。在栅耦合技术的基础上,给ESD保护器件增加一个衬底偏压可有效降低其触发电压,提升器件的ESD保护能力,称为衬底和门级触发技术[7]。

图2 栅耦合ESD保护电路

在PROM芯片的输出引脚主要采用了这种动态栅耦合的ESD保护电路。

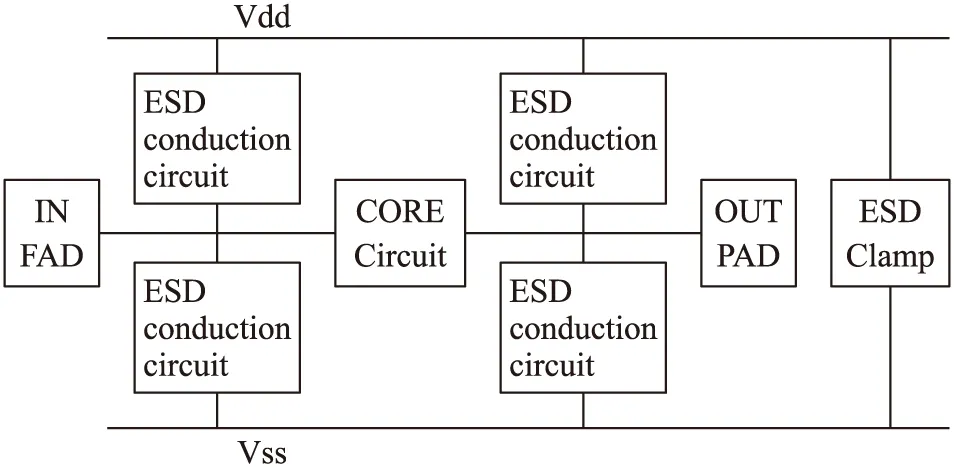

2 全芯片ESD保护技术

ESD可以发生在芯片的任意2个引脚之间,而且I/O PAD间的ESD事件常会转而跨在电源线和地线之间,如果没有电源和地之间的ESD保护设计,这会导致内部电路的损伤,造成电源和地之间的漏电和短路。所以,深亚微米CMOS IC中,ESD电路的设计要从全芯片的角度来考虑。全芯片的ESD保护电路安排如图3所示。

图3 全芯片ESD保护电路安排

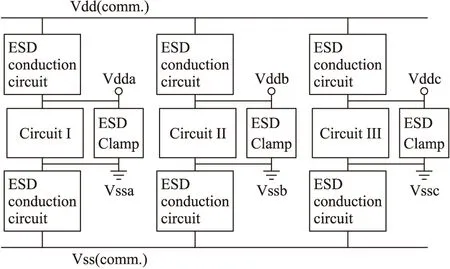

本公司的PROM芯片有3个电源对:数字电源对、模拟电源对和编程电压。因此我们采用了如图4所示的全芯片的ESD设计架构。先对每对电源对进行ESD保护,然后每个电源对分别通过ESD保护电路接到公共的电源线和地线。

图4 全芯片多电源ESD保护构架

通过做好每个电压域的ESD保护和各个电压域与公共电压域间的ESD保护,可以保证整颗芯片ESD放电通路的畅通和安全,为整颗芯片提供全方位的ESD保护。

3 高压编程引脚VPP的ESD保护设计

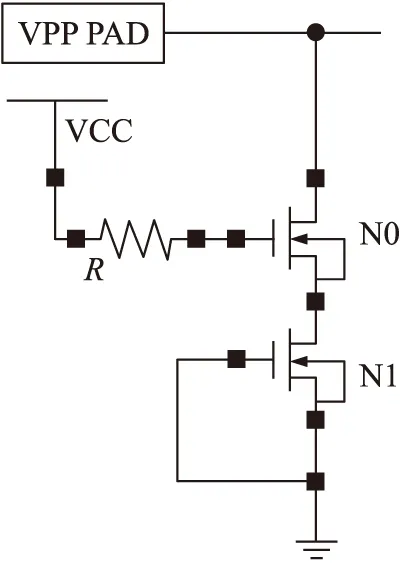

在PROM芯片中有一个比较特殊的PAD,就是高压编程引脚VPP。芯片的ESD失效阈值定义为芯片引脚在各种测试条件下最低的ESD耐压值,而VPP引脚的ESD保护能力是制约PROM芯片整体ESD保护能力的一个重要因素[8]。VPP引脚是用来给存储器件编程用的,编程电压高达8.5 V。VPP端口的ESD保护结构,不能采用PMOS管对电源保护。由于VPP端口在编程时输入的电压信号高于芯片的电源电压,PMOS会导致高压端口对电源通过寄生的二极管漏电,VPP输入的电压信号将被拉低,导致无法对存储单元编程。因此VPP端口ESD保护结构设计为串联NMOS接地结构。

高压编程引脚VPP的ESD保护电路结构如图5所示。为了保证ESD保护器件的耐压能力,NMOS管的长度L设计为0.8 μm。编程时,VRR输入8.5 V电压,此时,N0处于导通状态。VPP端口电压信号经过器件N0后,在N0上存在压降。这样采用NMOS的串联结构就避免了高压信号VPP直接施加在GGNMOS管N1器件的漏端,可有效提高高压端口VPP的直流耐压能力。该结构可以避免高压端口在编程时发生误操作。

图5 高压编程VPP引脚ESD结构电路图

4 测试结果

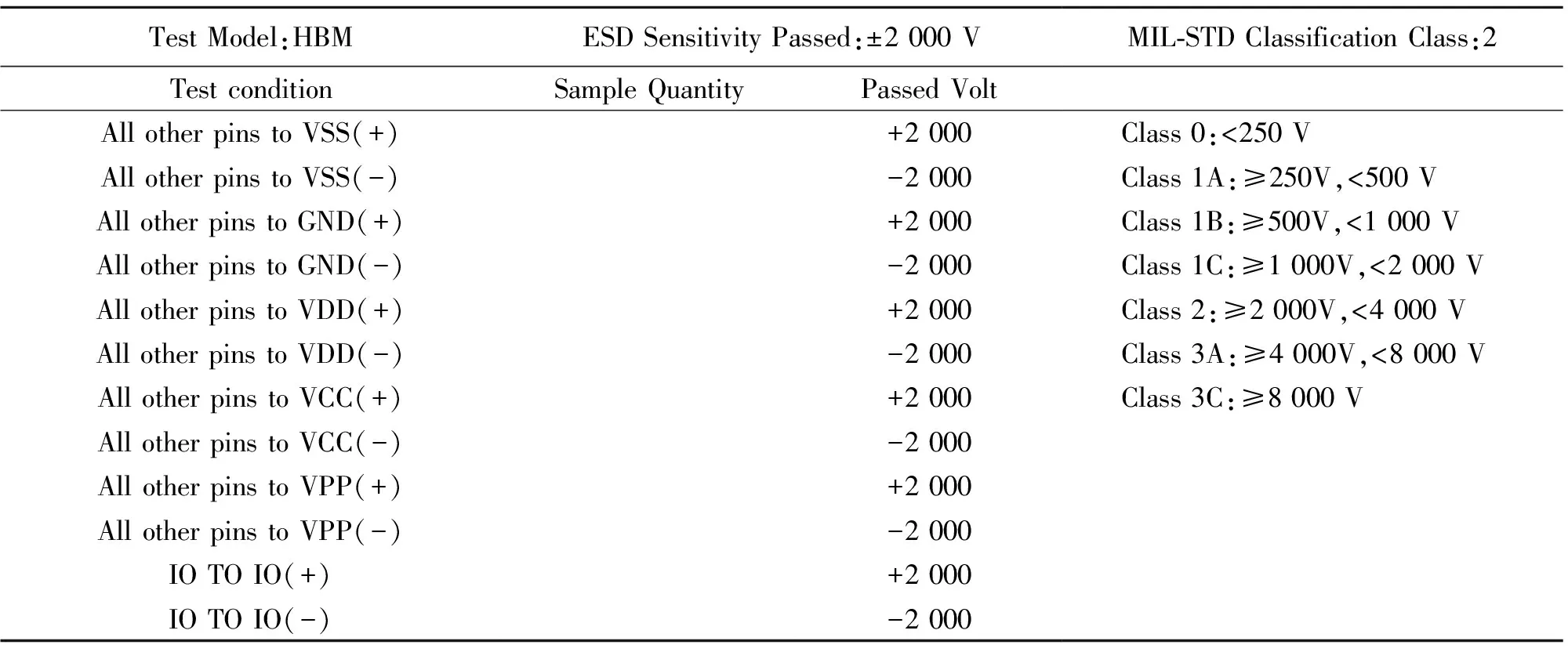

采用0.18 μm CMOS工艺流片,流片后的样品可以正常编程和读出数据,ESD器件不影响芯片的正常功能。对流片后的PROM芯片样品进行了ESD测试,测试结果如表1所示。

表1 ESD测试结果

测试结果表明,芯片通过了人体模型2 kV的测试,这满足了本项目的要求。

5 结论

随着CMOS工艺的不断发展,器件抗ESD能力却在下降。但是,通过改进工艺和ESD器件的结构,可以在一定程度上提升器件的抗ESD能力。同时,全芯片的ESD架构为越来越多先进工艺的IC器件所采用,可以真正提升整颗芯片的ESD防护能力。

采用多电源域ESD防护架构和全芯片ESD电路安排,从全芯片的角度进行了大容量PROM芯片的ESD防护设计,保证了PROM芯片整体的ESD放电通路的畅通。同时,对PROM芯片中的高压编程引脚做了ESD防护电路的加固设计,提升了芯片的ESD失效阈值。

参考文献:

[1]王颖.MOS集成电路ESD保护技术研究[J].微电子技术,2002,30(1):24-28.

[2]孔学东,恩云飞.电子元器件失效分析与典型案例[M].北京:国防工业出版社,2006

[3]臧佳锋,薛忠杰.深亚微米CMOS IC全芯片ESD保护技术[J].电子与封装,2005,5(6):26-30.

[4]蒋玉贺,王爽.CMOS集成电路ESD设计[J].微处理机,2008,29(3):19-21.

[5]Xie H,Feng H,Zhan R,et al.A New Low-Parasitic Polysilicon SCR ESD Protection Structure for RF ICs[J].Electron Device Letters,IEEE,2005,26(2):121-123.

[6]纪宗江,李冬梅.深亚微米混合信号全芯片ESD电路设计[J].半导体技术,2009,34(5):506-509.

[7]王颖.MOS集成电路ESD保护技术研究[J].微电子技术,2002,30(1):24-28.

[8]易峰,万颖.E2PROM工艺的ESD保护电路失效分析[J].电子与封装,2008,8(12):17-19.

裴国旭(1972-),男,汉族,吉林省人,学士,高级工程师,主要研究方向为集成电路抗辐照加固设计;

邓玉良(1969-),男,汉族,辽宁省人,博士,高级工程师,主要研究方向为高性能微处理器、存储器和可编程逻辑器件。

ESDProtectionTechnologyforDeepSubmicronMassPROMIC

PEIGuoxu*,DENGYuliang,FANLihui,LIXiaohui,PENGJinjun

(Shenzhen State Microelectronics CO.,LTD,Shenzhen Guangdong 518057,China)

Abstract:The ESD protection circuit design of PROMs is introduced based on 0.18μm CMOS process.From a whole-chip’s point of view,the whole chip is protected in the round using multiple power and whole-chip ESD protection design.At the same time,the high voltage programming port’s ESD protection design is optimized.Final products pass the ESD testing and satisfy the project required.

Key words:electro-static discharge(ESD);programmable read-only memory(PROM);whole-chip

doi:EEACC:257010.3969/j.issn.1005-9490.2014.04.001

中图分类号:O472.8

文献标识码:A

文章编号:1005-9490(2014)04-0587-04

收稿日期:2013-10-24修改日期:2013-12-05