基于CORDIC算法的DDS调频信号源设计

冒洋洋

(河海大学 江苏 南京 211100)

基于CORDIC算法的DDS调频信号源设计

冒洋洋

(河海大学 江苏 南京 211100)

为了实现可调频信号源的设计,提出了一种基于CORDIC算法的DDS调频信号源的设计方案,本中首先介绍了DDS的工作原理,同时对基于CORDIC算法的相幅变换方法进行了详细叙述,利用计算正弦值的CORDIC算法在FPGA上设计数字调频波信号源,可输出高精度数字调频信号,最后对整体模块进行了仿真和实验,输出中心频率23.5 MHz,带宽 1.5 MHz的调频信号,验证了文中提出的方案可行,并且结构简单易于实现。

DDS;CORDIC;调频波;FPGA

直接式数字合成技术 (DDS)是一种全新的数字幅相可控波形 的合成技术。由于现今大规模集成数字电路技术的飞速发展 ,DDS作为数字电路技术相对于以前模拟波形合成技术具有体积小、容量大、功耗低、速度快等特点,特别是在输出波形的频率分辨率、频率转换时间和相位噪声这些方面有非常大的提升。目前市面上有很多高性能和多功能的DDS芯片,其内部信号抖动较小,输出信号的效果也比较好。然而由于专用的DDS芯片的控制方式是固定的,故在工作方式、频率控制等方面会与一些系统的要求有偏差,采用高性能的FPGA器件设计DDS电路就是一个很好的解决方法,控制灵活并能够方便的实现信号调制功能,具有很好的实用性和灵活性[1]。

DDS电路由于数字电路的一些局限性会使输出信号产生较多的杂散分量,这些杂散分量主要是相位截断误差、幅度量化误差和DAC的非理想特性误差,其中相位截断误差会占到比较大的比例。因为在DDS电路中,为了达到较高的频率分辨率,通常将相位累加器的位数N设定的很大,但是在进行查找表寻址的时候,由于ROM表的容量受到限制,存储位数肯定小于地址位数,这时只能舍去地址位的低B位,用高位进行寻址,这就不可避免的引入了截断误差[2]。为了降低DDS的杂散,引入CORDIC算法进行实时正弦信号计算来代替ROM查找表是一个很不错的方法。

1 DDS调频信号源的基本原理

一般DDS主要由相位累加器,存储器ROM,数模转换器DAC构成。DDS基本思想是在ROM中存入正弦波的若干个均匀间隔的样值,在时钟频率的控制下把这些样值输出到数模转换器,将其变成模拟信号,原理图如图1所示。

基本原理组成框图如图所示,其中相位累加器是DDS的核心模块,其作用是负责将输入的频率控制字按时针频率不断进行累加,当累加器的输出溢出时就已经完成了一个周期的波形地址数据,输出的地址数据代表正弦函数的相位值,通过查找波形存储器就可以实现从相位到幅值的转换。相位控制字和幅度控制字则是分别通过相加与相乘运算来实现对输出波形的初始相位和幅度的控制。

设频率控制字为K,系统时钟为fc,累加器字长为N,则DDS输出波形的频率为f,根据DDS输出频率的计算公c式,可以通过改变频率控制字的方式来实现调频波的输出[3]。图2是调频波(FM)的实现原理图。

图2 调频波(FM)实现原理图Fig.2 Schematics diagram of FM wave

所以DDS输出的调频波可以表示为:

2 基于CORDIC算法的相位幅度转换

上述DDS电路需要大量的波形数据预先存在波形存储器ROM中,占用硬件资源较大并且会引入截断误差。所以本文提出基于CORDIC算法的相位幅值转换方法,只需要对输入数据进行简单的加减和移位,在硬件实现比较方便。采用流水线结构的 CORDIC算法,可以大大提高运算速度,减少传统DDS所占的硬件资源,且在FPGA中容易实现。

图3 CORDIC基本原理坐标图Fig.3 Coordinate diagram of CORDIC

上图为CORDIC原理图,在一个直角坐标系中,初始向量为 v(x,y),经过角度 θ的旋转后得到向量 v′(x′,y′)。 由图中可以看出:经过变换可以得到:

为了方便于在硬件实现,设定每次旋转的角度θ的正切值都是2的倍数,即θi=arctan(2-i),这样在硬件中实现乘法运算只需要将数据位移就可以[4]。

图4 CORDIC算法每一级基本运算单元Fig.4 Block diagram of CORDIC algorithm for each one basic computing unit

实现CORDIC算法一般使用由n个算法单元组成的n级流水线结构,CORDIC算法流水线结构基本单元如图4所示。CORDIC算法的精度受到流水线级数的影响,只有增加流水线级数才能提高算法的精度,而增加流水线级数之后系统的速度也会相应降低,因此必须选取合适的流水线级数。

按J.S.Walther提出的迭代序列最大角度,当迭代次数达到14次之后可以获得最大的角度99.88°[5],由于正弦波正负半周只是极性不同,取值是完全一样的,而0~π/2和π/2~π的取值是完全对称的,只要将相位求其π的补,就可得到其对称的取值,因而只要计算出四分之一周期波形的幅度值即可,于是只要在相位累加器用于波形寻址的有效输出A位中,高两位被用作确定象限,低A-2位用来参与运算。图5为单象限幅度转换结构示意图。

3 模块的设计

图5 单象限幅度转换结构图Fig.5 Construction diagram of single quadrant amplitude conversion

文中采用VHDL硬件描述语言进行设计,运行的软件环境是ISE12.4。使用16级并行流水线结构的CORDIC算法模块完成输出信号的相位幅度转换,而每次迭代计算都需要输入旋转角度的正切值,这里就直接在程序中声明一个包含16个角度正切值的数组。在控制字产生模块中,由于对调制信号的精度要求不高,所以前端调制信号是通过传统相位累加、ROM寻址来产生波形数据的,这里的ROM表位数相对较低。

4 仿真及实验

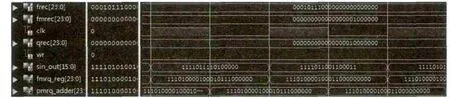

为了验证本文推导的具有调频功能的DDS结构的正确性,利用MATLAB对算法进行了仿真 ,同时用硬件描述语言VHDL[6]对算法进行了实现 ,最后导入ISIM对该结构进行了仿真,仿参数设置信号中心频率23.5 MHz,带宽 1.5 MHz,调制度为15%,DDS作时钟(fc)为100 MHz,仿真结果如下:

图6 调频波MATLAB仿真图Fig.6 MATLAB simulation diagram of FM wave

通过仿真后对比分析,要实现一个相同指标的DDS,使用CORDIC算法相比使用查找表方法的频率捷变速度不够理想,由于CORDIC使用迭代流水线结构,其频率捷变速度只有使用查找表方法的一半。但是使用CORDIC算法系统运行时间较快,系统的最大延迟只有后者的四分之一,并且CORDIC算法在减少相位截断误差,提高幅值精度,改善杂散性能方面有一定优势。

图7 基于查找表DDS调频波ISE仿真图Fig.7 ISE simulation diagram of DDS FM wave based on look-up table

图8 基于CORDIC算法DDS调频波ISE仿真图Fig.8 ISE simulation diagram of DDS FM wave based on CORDIC

5 结束语

文中介绍了一种用CORDIC算法模块替代DDS中ROM表的方法。使用这种方法可以在CORDIC模块精度允许的条件下尽量提高DDS相位截断后的保留字长,这样可以减小杂散,并且调整了CORDIC的算法模块,避免了在CORDIC运算时存在的死角。这种方法可以用于解决ROM表的存储容量限制给DDS性能提高带来的瓶颈,有较好的实用价值。

[1]李中阳,苏广川.基于DDS技术的高性能雷达信号源的设计[J].军民两用技术与产品,2006(9)29-32.

LI Zhong-yang,SU Guang-chuan.Design of high-performance radar based on DDS technology[J].Military and Civilian Dual-use Technology and Products,2006(9):29-32.

[2]Lionel Cordesses.Direct digital synthesis[J].IEEE Signal Processing Mag,2004(1):50-54.

[3]Vankka J.Method of Mapping from phase to Sine Amplitude in Direct Digital Synthesis [J].IEEE Transactionson Ultrasonics,Ferroelectrics and Frequency Control,March 1997,44:526-534.BIAN Jivnian,XUE Hong-xi.Design electronic circuits based on VHDL[M].Tsinghua University Press,2002.

[4]SWalther J.A unified algorithm for elementary functions[M].SFIPS Spring Joint Comput.Conf,1971:379-385.

[5]胡国荣,孙允恭.CORDIC算法及其应用[J].信号处理,1991(12):229-242.

HU Guo-rong,SUN Yun-gong.CORDIC algorithm and its application[J].Signal Processing,1991(12):229-242.

[6]边计年,薛宏熙.用VHDL设计电子线路[M].北京:清华大学出版社,2002.

Design of DDS FM signal source system based on CORDIC algorithm

MAO Yang-yang

(Hohai University, Nanjing 211100, China)

In order to satisfy the design of FM signal source,the design of DDS FM signal source system based on CORDIC algorithm is presented in this paper.This paper introduced the direct digital synthesis (DDS)technology,while described the methods of amplitude and phase transformation based on the CORDIC algorithm in detail,The system used the CORDIC algorithm to design digital FM signal source in FPGA.It can output high-precision digital FM signals.Finally completed the simulation and experiments of overall module.The output center frequency is 23.5 MHz,and bandwidth is 1.5 MHz.It verify the proposed scheme is feasible,and the structure is simple and easy to implement.

DDS;CORDIC;FM wave;FPGA

10.14022/j.cnki.dzsjgc.2014.16.040

TN99

A

1674-6236(2014)16-0132-03

2013-11-02 稿件编号:201311017

冒洋洋(1987—),男,江苏南京人,硕士。研究方向:信号与信息处理。