锁相环频率合成器相位噪声改善方法研究*

廖小健

(1.华中科技大学 武汉 430074)(2.武汉军械士官学校 武汉 430075)

1 引言

频率合成器以一个高稳定度、高准确度的标准频率作为参考,通过对参考频率进行倍频、混频、分频等处理产生大量与参考频率具有相同稳定度和准确度的不同频率的系统。频率合成器在电子设备中发挥着重要作用,直接影响着电子设备的性能,所以被称为电子设备的心脏。

目前用于实现频率合成器的技术主要有三种:直接模拟频率合成技术(DAS)、锁相环频率合成技术(PLL)、直接数字频率合成技术(DDS)。锁相环频率合成技术相比于DDS和DAS具有更高的杂散抑制,频谱更加纯净。相对于DDS,锁相环频率合成技术的频段更宽;相对于DAS,锁相环频率合成技术又具有结构简单的特点[1]。鉴于锁相环频率合成技术的以上优点,锁相环式频率合成技术已成为目前通信、仪表、雷达等电子设备中应用最广泛的一种频率合成技术。

但相对于另两种频率合成技术,锁相环频率合成技术的相位噪声较大。相位噪声会影响电子设备的各项性能。在通信系统中相位噪声会使话路信噪比下降,误码率增加;在雷达系统中影响雷达对目标的分辨能力;而混入接收机本振中的相位噪声,当接收机遇到强干扰信号时,会产生“倒混频”使接收机有效噪声系数增加。所以随着电子技术的发展,改善相位噪声是锁相环频率合成器研制的关键。

2 锁相环频率合成器的结构及相位噪声分析

锁相环频率合成的基本方法是:采用锁相环路对高稳定的参考振荡器锁定,利用环内所连接的可编程程序分频器,通过改变程序分频器的分频比N,获得N倍参考频率的输出频率。

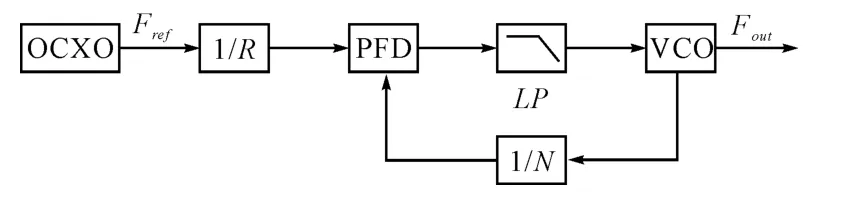

锁相环频率合成器结构如图1所示。

图1 锁相环频率合成器结构

锁相环频率合成器由参考晶振(OCXO)、鉴频鉴相器(PFD)、环路低通(LP)、压控振荡器(VCO)、R分频器和N分频器组成。由上图可知,VCO 经过N分频和参考晶振经过R分频后的信号都输入PFD 进行相位和频率比较,如果这两个频率不相等,PFD 的输出会改变,而VCO 的输出频率是由PFD 的输出控制的,所以VCO 的输出频率也会改变,直到两个频率相等,环路稳定工作。输出信号的频率为

式中Fref是参考晶振输出的参考频率,Fout是频率合成器的输出信号。如果要改变输出频率,只用改变分频比N就可以了。

按照上述方法构成的单环锁相频率合成器是锁相环频率合成的基本单元,这种基本单元在电子设备中有广泛的应用。但是,对于信号质量要求高的电子设备,这种频率合成器输出信号的相位噪声很难满足要求。

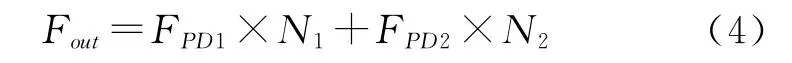

锁相频率合成器对参考晶振、R和N分频器引入的相位噪声表现为低通,而对VCO 引入的相位噪声表现为高通特性。现在主流的锁相环芯片都集成了鉴频鉴相器、R、N分频器,而参考晶振的相位噪声性能一般可以做得很好,所以通带内锁相环芯片(鉴频鉴相器、R、N分频器)产生的相位噪声占锁相频率合成器相位噪声的主导[2]。锁相环芯片产生相位噪声为

PNtotel表示锁相环芯片(鉴频鉴相器、R、N分频器)对输出信号贡献的相位噪声,PNSYNTH是鉴频鉴相器(PFD)1Hz归一化相位噪声基底,FPD是鉴相频率,其值由式(3)给出,N为锁相环的分频比。

由式(2)可知,锁相环芯片产生的相位噪声随着N值的增加上升速度是鉴相频率FPD上升的两倍。由式(1)和式(3)得到,输出频率一定时,分频比N和鉴相频率FPD的乘积是一定的,所以选用更大的鉴相频率可以降低鉴相器产生的相位噪声。鉴相频率提高一倍,相位噪声降低3dB。但单环锁相频率合成器的鉴相频率必须等于输出频率的频率步进,所以不能通过增大鉴相频率来降低相位噪声。

由式(2)可知,在鉴相频率一定的情况下,输出信号的相位噪声还取决于分频比N。频率合成器的相位噪声增加量为20logN,频率合成器要输出高频段信号,则分频比N会很大,必然造成噪声增加量20logN也很大,这时相位噪声往往很差,达不到工程应用的要求。通过上面的分析,可看出输出频率的相位噪声受分频比N的影响较大。为了解决这一问题需要对频率合成器的基本单元进行改造,使锁相环的分频比N减小。目前比较常用且能减小分频比N从而有效降低相位噪声的锁相频率合成器结构有以下五种:双锁相环环内混频结构、锁相环+分频器结构、DDS 激励锁相环结构、DDS内插锁相环结构和小数分频结构。下面逐一介绍它们的结构及适用的场合。

3 低相位噪声锁相环频率合成器结构

由于频率合成器相位噪声对电子设备的性能有着重要的影响,所以降低相位噪声是频率合成器设计和制作的一个重点。下面对当前流行的低相位噪声锁相环频率合成器结构进行分析研究,最后总结各结构对相位噪声的改善值及结构的优缺点。

3.1 双锁相环环内混频结构

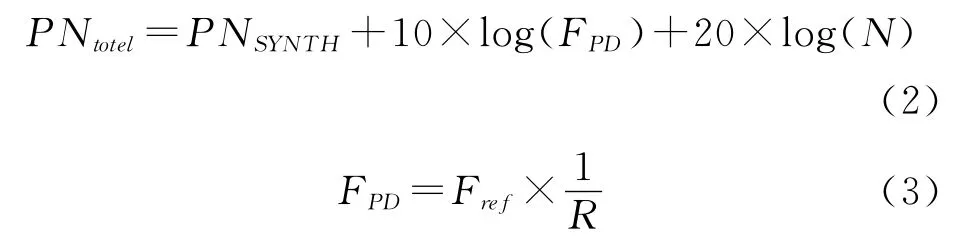

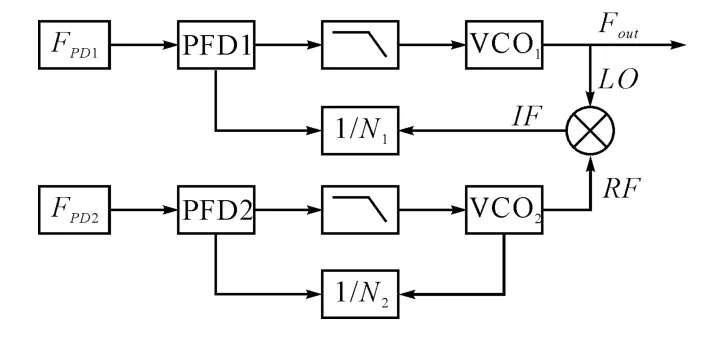

如图2所示,双锁相环环内混频结构由两个锁相环和一个混频器组成,主环和辅环输出频率关系为

其中,FPD1、FPD2分别是主环和辅环的鉴相频率,N1、N2则分别为主环和辅环的分频比[3]。

主锁相环输出的信号作为LO 信号和辅锁相环信号进行下变频,混频输出较低频率的IF 信号,降低主锁相环分频比N1。主锁相环的鉴相频率等于频率步进,这样只用通过改变N1就可以实现跳频。辅环输出的频率为定频信号,所以它的鉴相频率可以随意选取。

图2 双锁相环结构

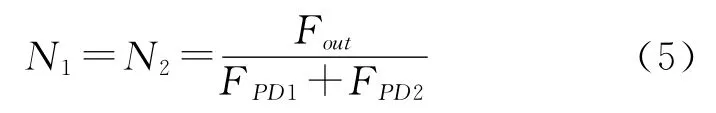

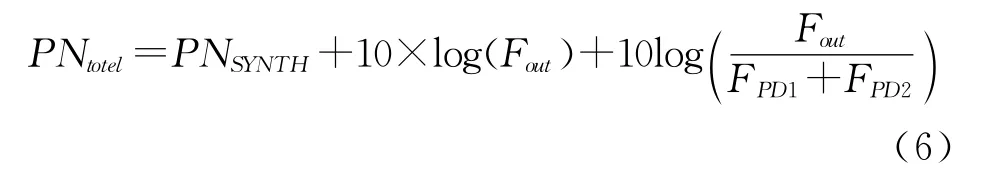

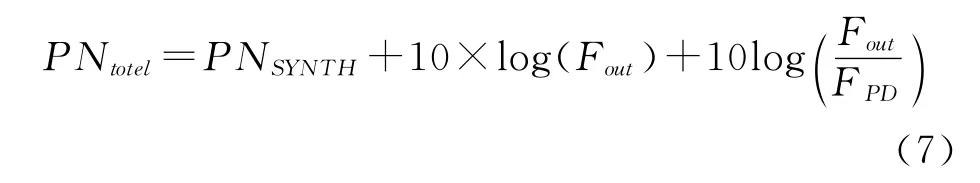

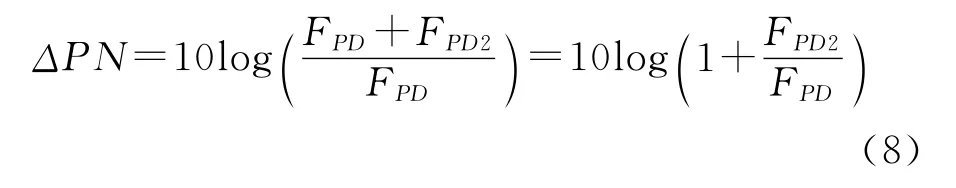

对双环的相位噪声进行计算得出,当两环的分频比为

双环的相位噪声取得最小值,为

单环频率合成器的相位噪声公式也可以改写为

而单锁相环的鉴相频率FPD=FPD1,式(7)与式(6)相减得到双环相对于单锁相环的相位噪声改善为

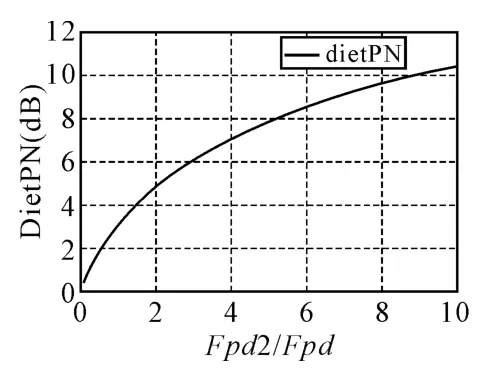

图3 ΔPN—FPD2/FPD

图3给出了双环结构相位噪声改善效果和鉴相频率比值之间的关系。如图3所示,比值越大,改善效果越好。但这种结构也有其缺点,首先,尽管通过辅环降低了主环的分频比,当频率步进很小时,主环的相位噪声仍然会很大;相对于单锁相环,这种结构需要的器件多了一倍;辅环的信号通过混频器可能会给输出信号带入一个大的杂散。

3.2 锁相环+分频器结构

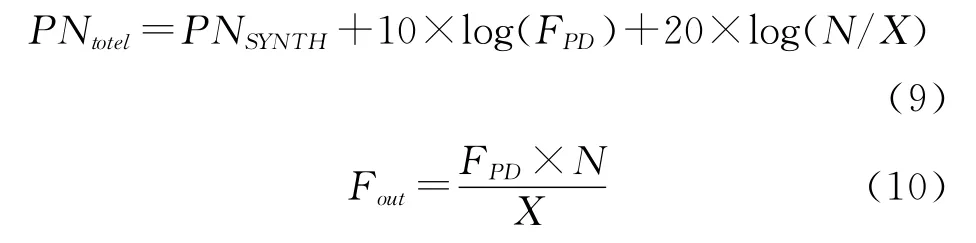

锁相环+分频器结构如图4所示。这种结构就是在锁相环后面加一个分频器[4]。输出信号的相位噪声为

由式(10)得到,使FPD和X同比例地增加时可保持输出频率不变;由式(9)得到,输出相位噪声却降低了。X每增大一倍,FPD也增大一倍,PNtotel则降低3dB。

图4 锁相环+分频器结构

但这种结构也有其不足之处,通过原理可知,这种方案间接提高了锁相环的输出频率,增加了锁相环芯片的选择和设计的难度;同时跟结构一类似,当频率步进很小要求的输出频率又很高时相位噪声仍然会很大。

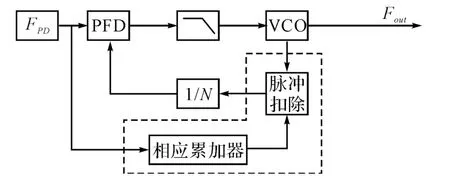

3.3 DDS激励锁相环结构

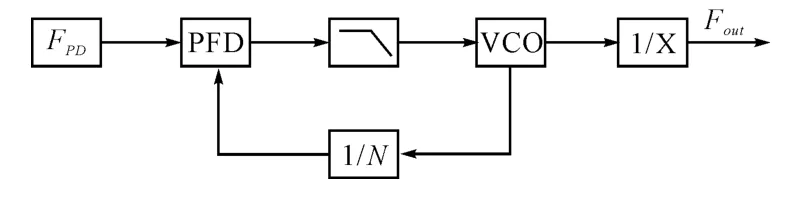

DDS激励锁相环结构如图5所示。

图5 DDS激励锁相环结构

这种方案利用DDS 作为锁相环的参考频率。工作时,保持锁相环的分频比N不变,通过改变DDS的输出频率来实现跳频[5]。这样在较低的分频比N的情况下可以得到较低的频率步进;而锁相环不仅可以增大DDS的输出频率范围,也可以对DDS产生的杂散进行滤除。实现了低相噪、高杂散抑制和宽频率范围的频率合成。但这种结构也有一个缺点就是如果DDS产生的杂散落在环路低通带内,就无法通过锁相环滤除。

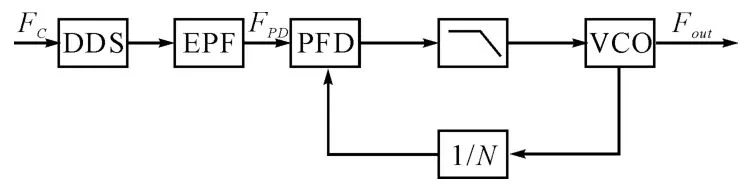

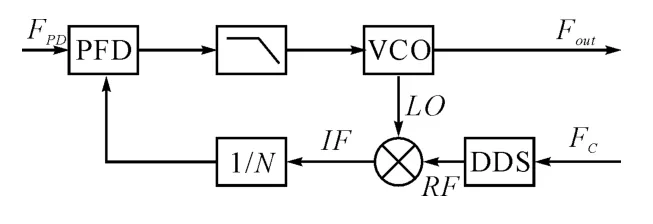

3.4 DDS内插锁相环结构

DDS内插锁相环结构如图6所示。跟结构三相似,DDS改进了锁相环的相位噪声和频率步进,而锁相环则滤除了DDS 的杂散[6];而且由于锁相环没有对DDS的信号进行倍频,DDS的相位噪声和杂散不会被锁相环放大,保证了输出信号的频谱纯度。

图6 DDS内插锁相环结构

相对于结构三,这种结构中混频器会给输出信号带入一个大的杂散。

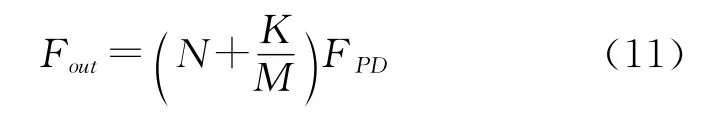

3.5 小数分频锁相环结构[7]

小数分频的结构如图7所示。它的结构基本和整数分频锁相环相同,但在分频器部分增加了相位累加和脉冲扣除的功能[8~9],这实现了锁相环的小数分频。式(11)给出了输出频率的计算公式

其中N代表整数部分,M是模数,K是小于等于M的整数,最小频率步进为Fr/M。在小数分频鉴相器中M可以取到很大的值,比如AD 公司的ADF4159为225。

对于整数分频锁相环,鉴频鉴相频率必须等于频率步进,当频率步进很小的时候,分频比就会很大,相位噪声会恶化。小数分频锁相环解决了这个问题,在比较大的参考频率下,仍可以实现小的频率步进,降低了相位噪声。但小数分频锁相环引入的脉冲扣除会产生小数杂散。

图7 小数分频锁相环结构

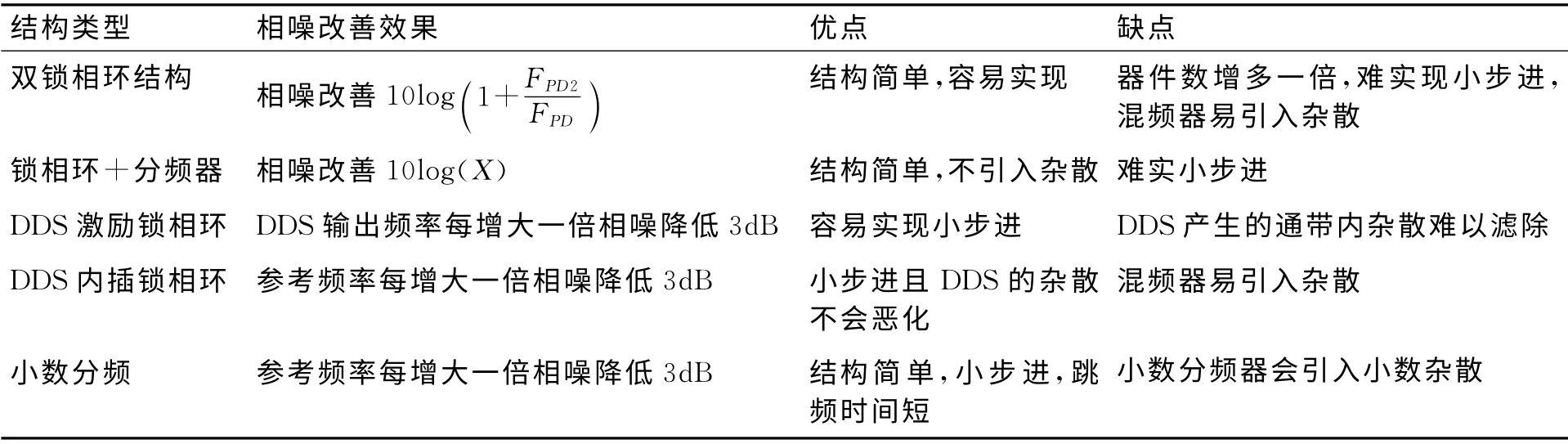

前面对目前比较常用且能有效降低相位噪声的锁相频率合成器结构做了具体的分析,现在将他们的相噪改善效果、优点、缺点做如下总结。

表1 锁相频率合成器相噪改善效果、优缺点表

4 结语

以锁相环为基础构成的频率合成技术是目前通信、仪表、雷达等电子设备中广泛应用的频率合成技术。频率合成器相位噪声的好坏对设备的性能有很大的影响。本文介绍了目前比较常用且能有效降低相位噪声的锁相频率合成器结构,这些结构都是通过降低分频比N实现相位噪声的降低。通过分析可以看出采用这些结构的频率合成器对相位噪声都有改善,同时由于结构不同,他们又有各自的优缺点,所以在设计频率合成器时,要根据不同的系统要求采用不同的结构。

[1]卢炳.Ku波段低相噪频率源的设计与仿真[J].舰船电子工程,2013,33(5):83-85.

[2]陈刚.锁相环路的相位噪声分析[J].科技信息,2009(3):112-113.

[3]李晋,刘光祜.C 波段宽带低噪声频率源的研制[J].现代电子技术,2008(274):53-55.

[4]Mike Curtin.Design a Direct 6-GHz Local Oscillator with a Wideband Integer-N PLL Synthesizer.USA:Analog Device,2001:33-39.

[5]Jaehung Choi,Minsu Kim,Seungha Shin,et al.Low Phase Niose S-band PLL Frequency Synthesizer Using DDS and Offset Mixing Techniques[C]//APMC,Singapore,2009:1409-1412.

[6]Li Yongke.The Design of Wide BW frequency synthesizer based on the DDS&PLL hybrid method[C]//ICEMI,Beijing,2009:689-692.

[7]赵伟波,管凤仁,祁佑光.S频段小数分频锁相环频率合成器实现与应用[J].飞行器测控学报,2011,30(4):31-34.

[8]N.Fatahi,H.Nabovati.Design of Low Noise Fractional-N Frequency synthesizer Using Sigma-Delta Modulation Technique[C]//International Conference on Microelectronics Proceedings,Serbia,2010:369-372.

[9]Jun Zhao,Yong-Bin Kim.A Novel All-Digital Fractional-N Frequency Synthesizer Architecture with Fast Acquisition and Low Spur[C]//International Symposium on Quality Electronic Design,CA,2010:213-216.