基于FPGA的数字多道梯形成形算法的实现

(成都理工大学,四川成都,610059)

基于FPGA的数字多道梯形成形算法的实现

王晓帆,任家富,操礼志,张俊文,谢加鹏,石 维,郭兰芳

(成都理工大学,四川成都,610059)

核能谱测量技术在核技术和核物理实验中有着非常广泛的应用,多道脉冲幅度分析技术是核能谱测量的关键技术。针对数字化多道脉冲幅度分析器的要求,研究并实现了数字化多道中的梯形成形算法。对梯形成形算法从数学理论上进行论证,并在MATLAB中进行仿真。采用FPGA作为核心芯片对该梯形成形算法进行建模,并通过modelsim进行仿真,实现了数字化多道中的梯形成形算法。该算法可以减少白噪声的干扰,有利于提高系统的性能,具有一定的意义和价值。

数字化多道;梯形成形算法;FPGA

核能谱测量技术已呈现数字化趋势,数字化的核能谱仪的处理速度快,抗干扰能力比较强,滤波和成形是数字化核能谱测量技术的重要环节。对于模拟的核能谱测量技术,影响其性能的因素主要有:弹道亏损、基线恢复、脉冲堆积、幅值提取及噪声等。而将核能谱测量技术数字化后能够减小这些因素所带来的影响。梯形成形算法能够减少脉冲堆积,弹道亏损,适应成形要求,有效地代替了模拟的滤波成形电路,从而改善了系统的性能。

1 梯形算法的实现

1.1 梯形成形滤波原理

梯形成形滤波在数字成形滤波中较为常用,该算法具有简单、快速等特点。与三角形成形算法相比,虽然三角形成形算法有较好的噪声抑制,但弹道亏损严重,不利于后面幅度提取。而梯形成形算法,适当的增加梯形的平顶宽度,就能提高系统对弹道亏损的免疫性能。

多道脉冲幅度分析器是核能谱测量技术的重要部分,通过核探测器将核信息转化成电信号。核探测器输出的信号是随机信号,该随机信号的幅值不等,间隔不等,波形不尽相同。虽然不同的探测器输出的信号不相同,但是它们具有相似的波形,都是上升沿陡峭,下降沿缓慢,类似于指数衰减信号。梯形成形就是将输入的指数衰减信号转换成同幅度的等腰梯形信号,其中等腰梯形的斜边宽度和平顶宽度是可调的。假设探测器的输出信号经过调理电路后的输出信号为理想的指数信号,其时域表达式由式(1)所示。

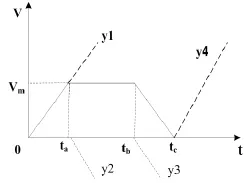

图1 梯形成形脉冲

输出的梯形成形脉冲的时域信号波形如图1所示,设梯形上升沿宽度为,底宽为,平顶宽度为,其时域表达式可用分段函数表示为:

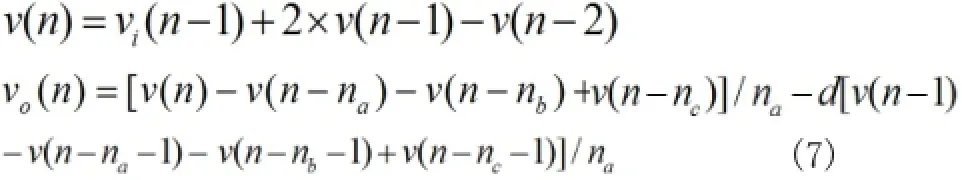

对式(5)进行Z的逆变换可得梯形成形算法的时域表达式:

图2 梯形成形滤波器的输入与输出脉冲信号

1.2 MATLAB及FPGA仿真实现

根据式(6),在MATLAB中编写指数信号和梯形成形滤波器的程序。当输入是理想的指数衰减信号时,经过梯形成形滤波器后得到的输出波形是梯形脉冲如图2所示。图2中假设采样频率为

平顶宽度越宽,对后续的幅值提取越有利,因为在实际系统中会有噪声的干扰,平顶的高度有一定起伏,如果只选取一个点作为峰值,会影响系统的可靠性,因此可选取平顶上的几个点的平均值作为峰值,可减少噪声的影响。理论上只要平顶宽度大于最大电荷收集时间就可以消除弹道亏损对系统的影响。但是选取的平顶宽度过宽会增加堆积脉冲的概率。所以要综合考虑弹道亏损和堆积脉冲的影响来选取合适的平顶宽度。

本设计采用xilinx的Spartan-6系列的FPGA来实现梯形成形算法,该FPGA具有丰富的I/O资源,时钟管理模块,嵌入式硬IP核等。用户可以通过硬件描述语言来实现各种逻辑功能。本文采用Verilog HDL硬件描述语言在来实现梯形成形算法。

由式(6)可知,梯形成形滤波器为一个特殊的IIR滤波器,虽然该滤波器的阶数较高,但实际参与运算的输入数据个数并不多,因此此设计具有可行性。在设计过程中,首先在MATLAB中生成理想的指数衰减序列,用来代替AD采样后的序列,并将这些序列写入coe文件中,在ISE中建立一个ROM,导入初始化coe文件,然后通过梯形成形模块对该序列进行成形处理,并进行modelsim仿真,仿真结果如图3所示。

图3 信号无噪声时梯形成形算法的modelsim仿真图

在FPGA实现中,使用了多个寄存器来缓存数据,调用了ISE自带的IP核进行了运算,运算的结果放入寄存器中缓存。由于实际情况,输入的衰减指数信号会含有噪声,因此需要对有噪声的信号进行成形处理,并进行modelsim仿真,仿真如图4所示。

图4 信号有噪声时梯形成形算法的modelsim仿真图

仿真结果表明,根据式(6)的梯形成形算法对理想的指数衰减信号具有很好的成形效果。但当信号中含有白噪声时,通过该算法得到的输出信号会有基线偏移,显然这不利于后续的处理。通过分析可知,白噪声在两次的累加过程中没有被滤除反而放大了,因此造成了基线偏移。由于梯形成形滤波器是线性移不变系统,即使级联子系统的顺序发生改变,总的输出结果也不会发生变化。因此将两次累加顺序提前,差分运算在后,新的梯形成形算法:

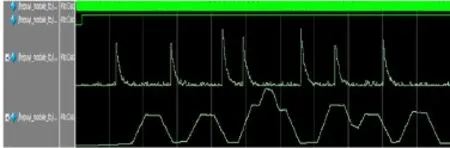

对改进后的梯形成形算法的modelsim仿真如图5所示。

图5 改进后梯形成形算法的modelsim仿真图

2 结论

本文对梯形成形算法进行了分析,并通过MATLAB验证了该算法的可行性。采用FPGA作为主控芯片设计了梯形成形算法。该梯形算法具有参数可调,灵活度更大等优点,能更好的抑制弹道亏损,具有实用价值。

[1] 王敏.数字核能谱测量系统中滤波与成形技术研究[D].成都:成都理工大学,2012.

[2] 肖无云,魏义祥,艾宪芸.数字化多道脉冲幅度分析中的梯形成形算法[J].清华大学学报(自然科学版),2005,45(6):810-812.

[3] 朱玉玉,杨露,杨民.基于LabVIEW的数字梯形成形算法仿真研究[J].核电子学与探测技术.2014,34(2):190-193.

[4] 周清华,张软玉,李泰华.基于MATLAB的数字化梯形滤波器的研究[J].核电子学与探测技术,2008,28(1):85-88.

[5] 陈亮.核素识别算法及数字化能谱采集系统研究[D].北京:清华大学,2009.

[6] 王敏,方法,曹建宇,等.基于FPGA的数字脉冲成形技术的研究[J].电子技术应用,2013,39(7):87-92.

王晓帆,男,1991年生,硕士,主要研究方向:嵌入式系统设计。

任家富,男,1963年生,教授,主要研究方向:核测量仪器研究。

Implementation of digital multi - channel trapezoid shaping algorithm based on FPGA

Wang Xiaofan,Ren Jiafu,Cao Lizhi,Zhang Junwen,Xie Jiapeng,Shi Wei,Guo Lanfang

(Chengdu University of Technology,Chengdu,Sichuan,610059)

Nuclear energy spectrum measurement technology has a very wide range of applications in nuclear technology and nuclear physics experiments.Aiming at the requirement of digital multi-channel pulse amplitude analyzer,the paper studies and realizes the ladder shaped algorithm in the digital multi-channel. The formation algorithm of the ladder is demonstrated from the mathematical theory and Simulation in MATLAB.FPGA is used as the core chip to model the trapezoidal shaping algorithm,and through the simulation of Modelsim,the trapezoidal shaping algorithm is realized.The algorithm can reduce the interference of white noise,and it is beneficial to improve the performance of the system,which has a certain significance and value.

digital multi-channel;trapezoidal shaping algorithm;FPGA

TN713+.7

A