抗单粒子效应的动态逻辑电路版图加固方法

(河海大学物联网工程学院,江苏常州,213022)

抗单粒子效应的动态逻辑电路版图加固方法

王海滨,杨云楼

(河海大学物联网工程学院,江苏常州,213022)

在高速电路设计中,动态逻辑电路应用十分广泛。但由于缺乏内在的上拉恢复路径,动态逻辑电路对单粒子效应极其敏感。因此,相比静态逻辑电路,它们在可靠性要求较高的应用中缺乏吸引力。因此,基于版图布局技术,提出了两个抗单粒子效应的动态逻辑电路设计。因为敏感节点之间的电荷共享效应,单粒子瞬态脉冲得到抑制。仿真结果和实验数据验证了它们具有更高的防止单粒子效应错误的能力。

动态逻辑;抗辐射加固;单粒子效应;软错误;脉冲窄化

0 引言

在自然环境中,无论是在外层空间或海平面,都存在有各种各样的辐射粒子。当这些粒子穿过半导体材料时,会有电荷沉积并产生额外的电子和空穴对,这跟入射粒子的LET值密切相关。在集成电路(IC)中,这些电荷的积累可能会引起被打击节点的电压或电流的瞬态脉冲,并波及相邻节点。从电路功能的角度来说,这可能会因此产生一个逻辑或者存储错误。这种现象被成为单粒子效应。

作为一个流行的逻辑电路设计方法,动态逻辑电路被用来实现各种高速运算单元。例如,在英特尔64位Itanium 2处理器中,利用动态逻辑电路实现了8输入的动态多路复用器。然而,动态逻辑电路对单粒子效应高度敏感。同时,随着半导体制造工艺的发展,电荷存储电路节点电容也变得越来越小,从而使得极小的扰动都可以改变它的状态。

各种动态逻辑辐射加固技术被提出并得以验证,大多数是门级的加固方法。例如,通过引入的168%的开销和182%的功耗,采用双冗余的电路结构的软错误率降低了4.5倍到6倍。尽管这些门级的加固方法可以有效屏蔽或纠正软错误,但它们经常带来各种其他方面的开销,如速度、面积和功率损耗等。

因此,我们提出了基于版图结构的方法,在保持降低各种开销的情况下,同时来提高动态逻辑电路抗单粒子效应的能力。论文其余部分的内容组织如下:第二节介绍了动态逻辑电路的单粒子效应问题和基础布局加固技术;第三部分说明了加固设计的工作原理;第四部分展示了TCAD工具的仿真结果;第五节给出实验结果和分析获得的数据并且比较提出的设计,第六部分是结论。

2 背景

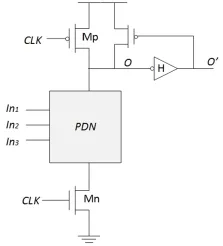

N型动态逻辑门的基本结构如图1所示,下拉网络采用与静态CMOS逻辑电路相同的方式构建。动态逻辑的运行机制包括预充电阶段和评估阶段。在预充电阶段,时钟的 pMOS (Mp) 打开并且下拉路径被禁用,输出(O)变为高电位。在评估阶段, Mp关闭且nMOS (Mn)打开。输出保持在高或低电位取决于下拉网络和输入。

图1: N型动态逻辑门

由于这两个不同的运行阶段, 动态逻辑与静态逻辑相比,对高能粒子的打击具有截然不同的反应。单粒子瞬态脉冲可能发生在任一阶段,并导致不同类型的电路错误。如作者在文献[10]中所讨论的,一个N管打击在预充电阶段或评估阶段发生对动态逻辑电路的损害比其他情况更加大,并且可能会导致粒子翻转。因此,本文侧重研究针对这两种情况的加固方法。

版图级的加固技术, 在速度和面积上带来的开销相对较小。保护环技术是一种布局方法,它长期被用于保护CMOS电路的正常工作,以前的工作证明它在降低pMOS器件电荷收集上有效果。另一种技术被称为保护漏极的技术在文献[12]中被第一次公开。保护漏极技术适用于nMOS 设备, 软错误率比保护环技术小30%-40%。

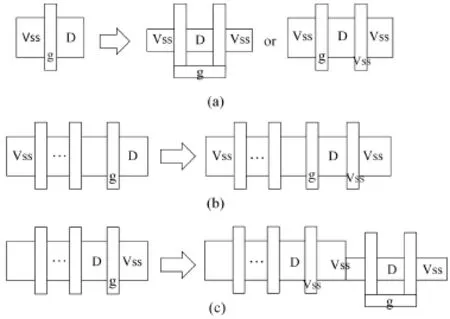

[13]中提出的源极扩展技术采用与保护漏极类似的机制来减少nMOS的电荷共享。这种技术的实现可分为三种形式,具体形式取决于设计的原始布局。如果漏极和源级仅仅被栅极隔开,可以用双指结构,如图 2 (a) 所示。双指结构的优点是减少的漏极区域降低了粒子击中漏极的可能性,并且沉积在漏极上的电荷能够被漏极侧面的源极共享。由于制造的限制,在漏极宽度要切成两半显得太窄的情况下,额外的源极区域可以放在漏极的另一边,并由一个永远关闭的栅极隔开。这种结构也可用于源极和目标漏极之间存在多个栅极的时候,如图 2 (b) 所示 。图2(c)描述的方案是,将漏极放置在布局的中心,将前面所述的方法都被组合,使得全部都能够被利用。

图2: 基于不同版图布局的源极扩展方案(a)漏极和源极被单个栅极隔开(b)漏极和源极被多个栅极隔开(c)漏极不在布局的边缘

额外的源极同样可以连接到VDD而不是VSS,这样的实施方案在[14]中被称为“漏极扩展”。漏/源扩展技术能够应用于大多数组合逻辑单元。标准库单元的报告表明,对于INV, NAND2和 AOI21而言, 大约有30%到40%的开销。根据[13]中的仿真结果显示,漏极和源极扩展方法分别获得18.75% 的12.60%单粒子瞬态脉冲宽度的减少。

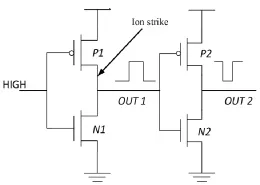

另一种适用于动态逻辑电路的加固方法是脉冲窄化。脉冲窄化的概念在[15]中被首次提出,用来描述单粒子瞬态脉冲宽度通过多级逻辑链的缩减现象。以图3为例,当粒子打击第一个反相器的漏极,从而引起反相器的输出(OUT1)产生单粒子瞬态脉冲,脉冲传播到第二个反相器并且导致其输出(OUT2)产生一个相反极性的脉冲。另一方面,当P2靠近 P1时,粒子撞击存储的电荷能够轻易扩散到P2,并且引起OUT2的由低到高的转变,结果是OUT2的脉冲有效缩短或窄化。

图. 3: 两个反相器之间传播的单粒子瞬时脉冲

实验结果表明,脉冲窄化在先进工艺下更加有效,这是因为电路组件距离更近,同时,粒子撞击呈一定角度,也更容易引起电荷共享。[16]中的研究利用促进脉冲窄化的方法提出了一种加固技术。

脉冲窄化设计方案的优点是减小了面积和功耗开销。在示例中或门的额外 pMOS 增加 N -well 40%的面积。在设备的总面积比补充部分大得多,面积带来的危害减小。同时功耗增加因为X节点电容增加,电容的增加由额外的晶体管引起。

3 设计实现

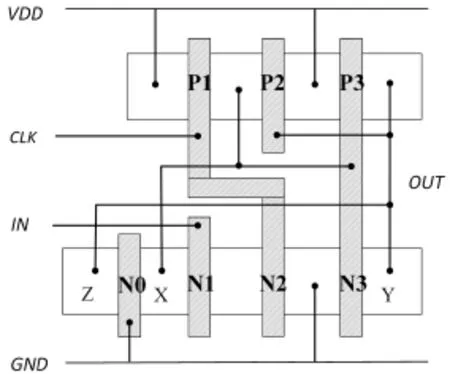

以多米诺缓冲器为应用电路对象,我们使用漏极扩展技术、脉冲窄化技术和常规布局等3种方法进行设计,并进行比较,以研究单粒子瞬态脉冲的缓解效果。采用常规布局方法的设计是我们的参考设计,如图 4所示。在采用常规方法设计的一个多米诺骨牌缓冲器的版图布局中,其中晶体管之间的扩散区域尽可能共享以使总面积最小。

图. 4: 传统多米诺缓冲器布局

图. 5: 采用漏极扩展的多米诺缓冲器布局

图. 6:采用漏极扩展的多米诺缓冲器实际原理图

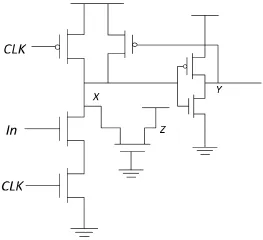

如上所述, 动态逻辑电路无论是在预充电阶段还是在评估阶段都特别容易受到N管打击的影响。因此,加固的主要目的是使nMOS设备中的相邻节点变得更加可靠,例如图4中的X和Y。带漏级扩展的多米诺缓冲器的布局如图5所示,漏极X和扩散区的Z之间的栅极N0与GND相连,有效的关闭了栅极。扩散区的Z 与 VDD相连,目的是提升节点X的电荷共享。这个设计的原理图在图6中给出。

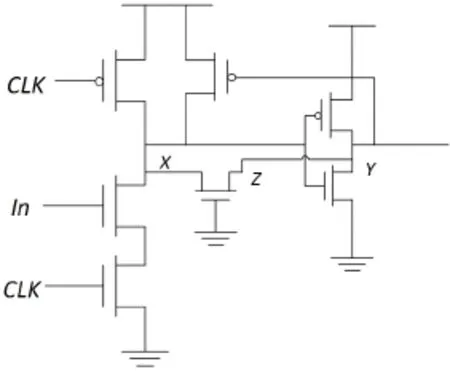

利用脉冲窄化的多米诺缓冲器在图7中给出。非反向的多米诺逻辑使它能够适合于利用脉冲窄化。这是由于节点X和节点Y之间有相反的逻辑值,他们的电荷共享有益于单粒子瞬态脉冲的脉冲窄化。该方法不是在关键节点的左边放置一个额外的晶体,而是仅仅加入一个额外的扩散区域Z,这和漏极扩展方法一样。不同于漏极扩展的是这个额外的扩散区与Y相连而不是VDD,这么做的目的是促进X和Y之间的脉冲窄化。有效的电路示意图如图 8 所示。

图7: 采用脉冲窄化的多米诺缓冲器

图8:采用脉冲窄化的多米诺缓冲器的原理图

4 单粒子效应仿真

为了分析辐射效应对布局实现中的影响,用Synopsys的新一代TCAD工具Sentaurus建立了三种布局(常规,漏极扩展,和脉冲窄化)的3D设备模型。考虑到三个布局在nMOS部分有所不同,所以只有nMOS设备才在TCAD中模拟,测试平台中的其他设备都使用 SPICE 模型进行实例化,并电连接到 TCAD 模型。

通过重离子模拟来分析单粒子效应效果对设备的影响。采用的电路结构是:四个多米诺缓冲器首尾相连,然后连接到 D 锁存器的输入。锁存器和缓冲器共享一个时钟信号。因此,当CLK为低电压,缓冲器处于预充电状态,缓冲器的最后一个状态输出将关闭锁存器。当CLK为高,输入信号(IN)传输到锁存器的输出,混合模式通过第一级多米诺缓冲器的关键nMOS设备在3D的TCAD模型中仿真,其他的电路用SPICE模型进行建模。

4.1 预充电阶段

在预充电阶段,一个nMOS的漏极的粒子打击能够导致单粒子脉冲的产生。因为预充电的pMOS晶体管是导通的,输出电压将最终恢复。但是,如果下一个评估阶段在输出电压完全恢复之前开始,一个单粒子翻转错误可能可能因此产生。因此,单粒子瞬态脉冲越宽,越可能发生一个软错误。

图9 显示了在预充电阶段N管打击的单粒子瞬态脉冲的脉冲宽度。不出所料,高的LET导致宽的脉冲宽度。所有设计中,单粒子瞬态脉冲的脉冲宽度随LET的增长接近线性。与采用参考版图的设计相比,漏极扩展和脉冲窄化设计在28MeV*cm2/mg的情况下大约有33%的脉冲宽度减小。

图9:预充电阶段中单粒子瞬态脉冲宽度

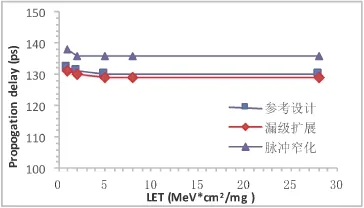

4.2 评估阶段

图10描述了评估阶段垂直入射的离子对N管打击下的单粒子脉冲脉冲传播延时。脉冲窄化方法比其他两种方法的延时要高一些。如该图所示,脉冲窄化的传播延时和LET之间的关系为接近线性的关系。这是由于脉冲窄化对单粒子瞬态脉冲的抑制作用。在评估阶段,延长的传播延时会降低粒子翻转的可能性。

图10:评估阶段垂直入射打击N管情况下的传播延时

5 实验结果

这两种设计,连同参考结构被设计在一个130纳米工艺的测试芯片中。每个单元的晶体管以最小距离放置。为了保持粒子打击的机会相等,关键节点漏极的面积在设计中保持不变。

测试芯片安装在PCB版上并且放置在重离子束下接受辐照。在测试中,测试芯片被三种粒子轰击(Ne, Ar, Kr) ,它们的LET值分别为2.7, 8.4 和28.3 MeV*cm2/mg。重离子采用垂直辐照的方式,测试链的时钟频率为1MHz。

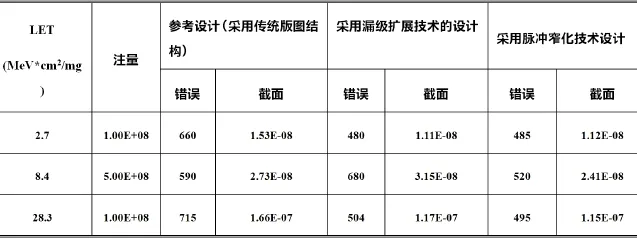

辐照实验结果总结于表1,列出了重离子的LET,粒子翻转的错误总数和错误截面。可以明显看出,我们提出的2个设计,在错误截面方面,与参考设计相比,降低了大雨20-30%。所以,我们的设计具有更好的防辐射性能。

6 结束语

表1: 重粒子测试结果

我们提出了两种基于版图结构的动态逻辑电路的加固技术。通过利用电荷共享现象,电路的防辐射性能得到了提升,实验数据表明,与参考设计相比,错误截面降低了大约20-30%。另一方面,我们提出的设计在面积和功耗方面的开销并不显著。

[1]P.Dodd,L.Massengill.Basic mechanisms and modeling of single-event upset in digital microelectronics [J].IEEE Transactions on Nuclear Science,2003, 50(3):583–602.

[2] P.Gronowski,W.Bowhill,R.Preston,M.Gowan,R. Allmon.High-performance microprocessor design[J].IEEE Journal of Solid-State Circuits,1998,33(5):676–686.

[3] S.-C.Chang,C.-H.Cheng,W.-B.Jone,S.-D.Lee,J.-S. Wang.Charge-sharing alleviation and detection for cmos domino circuits[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2001,20(2):266–280.

[4] C.-C.Wang,C.-C.Huang,C.-L.Lee,and T.-W.Cheng.A low power high-speed 8-bit pipelining CLA design using dual-threshold voltage domino logic[J].IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2008,16(5):594–598.

[5] J.Warnock,Y.-H.Chan,S.Carey,H.Wen,P.Meaney,G. Gerwig,H.Smith,Y.Chan,J.Davis,P.Bunce,A. Pelella,D.Rodko,P.Patel,T.Strach,D.Malone,F. Malgioglio,J.Neves,D.Rude,and W.Huott.Circuit and physical design implementation of the microprocessor chip for the zenterprise system[J]. IEEE Journal of Solid-State Circuits,2012,47(1): 151–163.

[6]S.Naffziger,G.Colon-Bonet,T.Fischer,R. Riedlinger,T.Sullivan,and T.Grutkowski.The implementation of the Itanium 2 microprocessor [J].IEEE Journal of Solid-State Circuits,2002, 37(11):1448–1460.

[7] D.Erstad.Dual redundant dynamic logic:美国,7,679,403 [P].Mar.16 2010-3-16.

[8] X.She,N.Li,D.Erstad.SET tolerant dynamic logic [J].IEEE Transactions on Nuclear Science,2012, 59(2):434–438.

[9]J.Kumar,M.Tahoori。A low power soft error suppression technique for dynamic logic[C].20th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, 2005.

[10] H.-B.Wang,M.-L.Li,L.Chen,R.Liu,S.Baeg,S.-J.Wen,R. Wong,R.Fung,J.-S.Bi.Single Event Resilient Dynamic Logic Designs[J].Journal of Electronic Testing, 2014,30(6):751–761.

[11]J.D.Black,A.L.Sternberg,M.L.Alles,A.F. Witulski,B. L.Bhuva,L.W.Massengill,J.M. Benedetto,M.P.Baze,J. L.Wert,M.G.Hubert.HBD Layout Isolation Techniques for Multiple Node Charge Collection Mitigation [J]. IEEE Transactions on Nuclear Science,2005,52(6): 2536–2541.

[12] B.Narasimham,J.W.Gambles,R.L.Shuler,B.L. Bhuva,L. W.Massengill.Quantifying the Effect of Guard Rings and Guard Drains in Mitigating Charge Collection and Charge Spread[J].IEEE Transactions on Nuclear Science,2008,55(6):3456–3460.

[13] J.Chen,S.Chen,Y.He,Y.Chi,J.Qin,B.Liang,B.Liu. Novel Layout Technique for N-Hit Single-Event Transient Mitigation via Source-Extension[J]. IEEE Transactions on Nuclear Science,2012,59(6): 2859–2866.

[14]J.Ahlbin and L.Massengill,Single-event transient pulse quenching in advanced CMOS logic circuits [J].IEEE Transactions on Nuclear Science,2009, 56(6):3050–3056.

[15] N.M.Atkinson,A.F.Witulski,W.T.Holman,J.R.Ahlbin, B.L.Bhuva,L.W.Massengill.Layout Technique for Single-Event Transient Mitigation via Pulse Quenching[J].IEEE Transactions on Nuclear Science, 2011,58(3):885–890.

Single Event Hardened Dynamic Logic Based-on Layout Techniques

Wang Haibin,Yang Yunlou

(College of IOT, Hohai University,Changzhou Jiangsu,213022)

Due to the intrinsic lack of restoring paths,dynamic logic circuits have significant singleevent susceptibility,and thus,they are not preferred in applications requiring high reliability when compared to static logic.However,in high speed applications,this circuit family is still very attractive. Therefore,this papers presents two layout-based single-event resilient dynamic logic designs.The resultant SET pulse is suppressed because of charge-sharing in the layout-level.Simulation results verify that they enjoy higher single event tolerance.Experimental results validate the fact that approximately 20%~30% of magnitude reduction in cross-section is achieved for both designs.On the other hand, the increase in single-event performance is achieved at the expense of non-significant power and area overhead.

dynamic logic;radiation hardening;single event effect;soft error;pulse quenching

****

A

10.3969/j.issn.1006-2475.

国家自然科学基金(61504038)

王海滨(1980年),男,山东济宁人,讲师,在加拿大University of Saskatchewan获得博士学位并任该校博士后,现任河海大学物联网工程学院讲师,主要研究领域为集成电路中的辐射效应和防辐射加固技术;

杨云楼(1991年),男(苗),贵州松桃人,硕士研究生,在河海大学获得工学学士学位,现在是河海大学物联网工程学院在读硕士研究生,主要研究领域为自动化与智能化。