基于IEEE 1500的NoC资源节点Wrapper设计*

王建喜,许川佩,王 光

(桂林电子科技大学电子工程与自动化学院,广西自动检测技术与仪器重点实验室,桂林 541004)

NoC是借鉴计算机网络技术设计[1]的片上网络芯片,路由节点组成的通讯架构实现数据的路由[2]和分组交换[3],资源节点通过与路由节点的一对一通信实现各种不同功能的资源节点在通讯架构中的交互通信,NoC系统由此实现各项复杂功能。

分布式的网络体系结构[4]和集成电路复用技术使得NoC在面对功能需求增多时,通过增大NoC系统规模即可集成更多的资源节点。但伴随着系统规模的增大以及集成度的提高,如何应对可能出现的故障导致的测试需要成为NoC进一步发展亟待解决的问题。

从NoC的基本结构来看,主要测试对象包括路由节点、互连线以及资源节点,其中路由节点全部相同的特点方便了对其测试方案的设计,而且所构建的通讯架构成为路由节点测试的最直接方法[5];互连线是节点之间的数据交换路径,完成的功能单一,而且制造工艺的进步使得互连线出现开路、短路、串扰[6]等故障的概率大为降低;与路由节点和互连线相比,NoC系统中的资源节点各不相同,这给测试带来极大的困难,如何为资源节点建立统一、高效的测试方案[7]成为NoC测试研究中的一大难题,本文即针对资源节点的测试展开研究。

1 NoC资源节点测试特征分析

NoC系统中资源节点各不相同,相比复用率高、具有一定结构的路由节点和互连线,资源节点的测试较为繁杂。在资源节点设计验证阶段,对重要节点部位引出测试点信号可方便故障侦察,但在NoC系统集成阶段不可能将测试点信号引出。

NoC的设计思想着重于资源的复用,不可能所有的资源节点都从底层开始设计,而且由于知识产权的问题,诸多资源节点的内部具体结构并不公开,因此对资源节点的测试主要以输入端口施加测试矢量、输出端口捕获测试响应的方法进行。

整合考虑组合逻辑、时序逻辑的资源节点输入、输出端口类型,主要包括数据信号、时钟信号、复位信号、功能设置信号、功能指示信号等,不难发现对于工作时序复杂的资源节点,时钟信号端、功能设置端往往需要频繁的信号变化,而数据信号可能在多个工作时钟或多数时间内并不变化。因此,针对不同端口的测试特征构建测试机制是提高测试效率的有效手段。

2 NoC资源节点测试方法分析

NoC系统中,资源节点连接于路由节点的本地端口,如何建立资源节点测试的数据施加机制决定着测试效率的高低。在NoC系统中,资源节点的测试方法大致有3种:

(1)复用NoC通讯架构 测试矢量数据只需经由某路由节点的通信端口发送到路由节点网络中,即可按照网络的路由协议到达并施加于待测资源节点,测试响应数据同样以路由通信的方式经NoC通讯架构返回。

(2)边界扫描测试 为NoC系统中的资源节点设计边界扫描结构,利用边界扫描链路将测试矢量数据串行移位到待测资源节点的边界扫描单元[8],即可施加于待测资源节点,测试响应数据经边界扫描单元捕获后从链路中串行移位输出。

(3)IEEE 1500 Wrapper 为资源节点设计基于IEEE Std 1500 的 Wrapper[9],测 试 矢 量 数 据 通 过Wrapper提供的测试接口施加于待测资源节点,测试响应数据同样由测试接口输出。

复用NoC通讯架构的方法,只需将测试访问设备或BIST测试逻辑连接于NoC某路由节点的通信端口,此外不需要围绕NoC构建测试结构,但复用NoC通讯架构的方法必须确保通讯架构的可靠性,以保证测试矢量数据准确、快速地完成路由,而随着通讯架构复杂度的增大,通讯架构自身、路由算法带来的未知因素增多,如拥塞、丢包、延迟等严重影响测试结果的不确定性因素,因此复用NoC通讯架构的方法一般仅用于功能测试。边界扫描测试方法和基于IEEE 1500 Wrapper的测试方法避开通讯架构建立了测试访问机制,其中边界扫描测试方法应用扫描链[10]实现测试功能,而IEEE Std 1500定义的Wrapper为可测性设计提供了标准化、模块化、可扩展[9]的技术方案,两者最大的区别是:①IEEE 1500 Wrapper具有扩展并行访问端口的设计机制,而边界扫描只有一位的串行测试数据接口[11];②IEEE 1500 Wrapper的技术优势在于嵌入式内核的可测性设计和测试,而边界扫描测试的技术优势在于互连测试。基于以上因素,对于NoC片内的资源节点,设计IEEE 1500 Wrapper更具有技术优势。

3 IEEE 1500 Wrapper设计

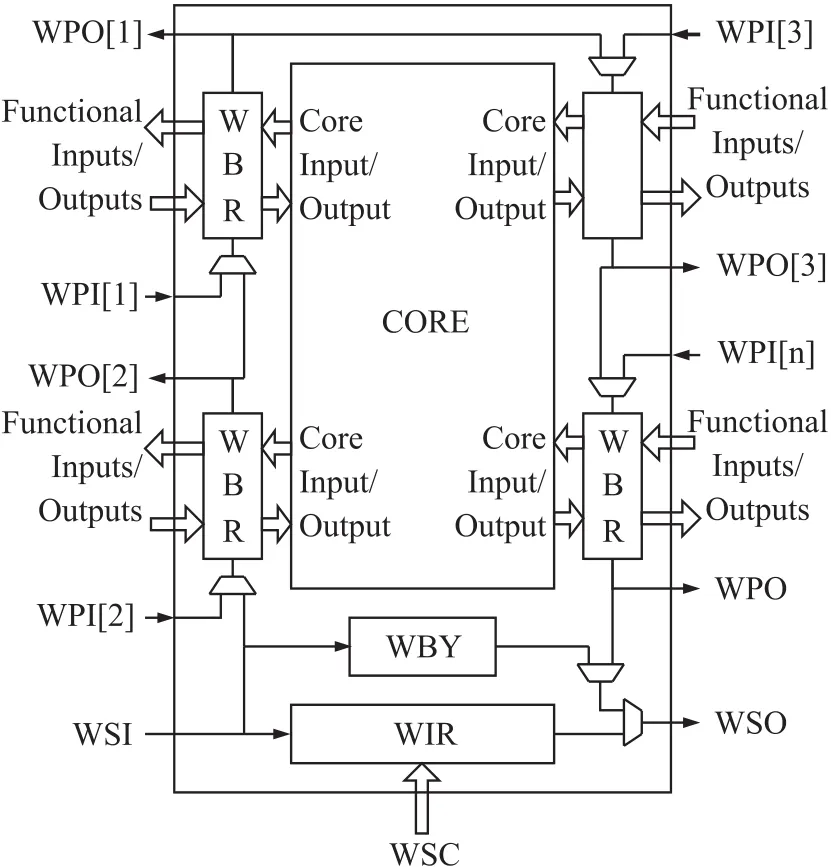

IEEE Std 1500主要从寄存器单元和测试接口两方面对Wrapper硬件结构进行定义。寄存器单元包括边界寄存器WBR、指令寄存器WIR和旁路寄存器WBY;测试接口包括串行接口WSP、可选并行接口WPP。WSP接口由串行输入WSI、串行输出WSO,以及一组串行控制接口WSC组成;WPP接口由并行输入WPI、并行输出WPO,以及一组并行控制接口WPC组成,由寄存器单元和测试接口组成的Wrapper结构如图1所示。

图1 IEEE 1500 Wrapper

WSC接口用于控制Wrapper从WSI/WSO串行移入/移出测试指令或测试数据并进行一系列的测试操作,包含一系列接口信号:WRCK、WRSTN分别用于Wrapper的工作时钟和复位信号,Selec⁃tWIR、ShiftWR、UpdateWR、CaptureWR 分别用于Wrapper WIR选通、指令/数据移位、指令/数据更新、指令/数据捕获的基本测试操作[9]。在特定情况下设计的WBR寄存器可能需要一个或多个辅助时钟以及数据翻转信号TransferDR以具备更多的测试操作功能。

由于WPC接口对WPI/WPO和Wrapper的控制作用和WSC接口的功能非常类似,因此多数情况下,在需要设计并行测试接口时,仅为Wrapper设计WPI/WPO接口,而相关指令和数据的并行测试操作由WSC接口控制。而且,并行测试接口WPP的设计理念一般遵循“分段并行”的思想,即在输入、输出端口较多时,设计WBR链的分段并行输入、输出端口,每段WBR链内依旧依照串行方式。

3.1 IEEE 1500 WBY设计

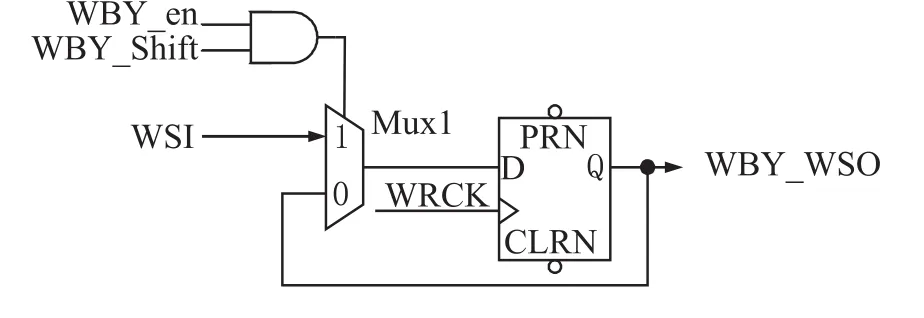

如图1所示,旁路寄存器WBY位于WSI、WSO之间,其作用是为WSI和WSO提供一条最短的移位路径,实现对WBR链的旁路。一般情况下,WBY按1位长度设计,如图2所示,特殊情况下可设计为多位长度。

图2WBY寄存器

图2中,使能信号WBY_en取决于WIR选择信号SelectWIR和Wrapper指令,当SelectWIR=0且当前有效指令选择WBY作为WSI-WSO之间的移位路径时,WBY_en有效。

3.2 IEEE 1500 WBR设计

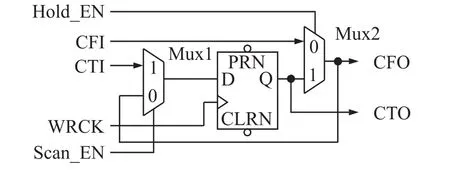

WBR是Wrapper执行测试的关键部分,其由一系列位于内核逻辑输入、输出端的基本单元组成,典型的WBR单元[12]如图3所示。

图3 典型的WBR单元

典型WBR单元的功能如表1所示,表中“FF”代表触发器Q端的输出值,“(WRCK)”表示需要WRCK的上升沿触发。

根据图3和表1,典型WBR单元可完成的各项基础功能如下:

(1)正常工作

(Hold_EN,Scan_EN)=(0,X),信号 CFI→CFO的选通使得WBR相当于“透明”状态,不对正常输入、输出信号产生影响;

(2)Shift操作

(Hold_EN,Scan_EN)=(X,1),在 WRCK 上升沿,CTI端的数据向CTO端移位,即实现WBR单元之间的数据串行移位;

(3)Update操作

(Hold_EN,Scan_EN)=(1,X),触发器FF的值经CFO端更新输出,即输入端WBR单元中的数据向内核输入端施加,输出端WBR单元中数据向外部互连电路激励输出;

(4)Capture操作

(Hold_EN,Scan_EN)=(0,0),在 WRCK 上 升沿,CFI端的数据捕获进触发器FF,即输入端WBR单元捕获外部输入互连线路的信号,输出端WBR单元捕获内核输出端的信号。

典型WBR单元具备以上操作功能即可完成基本指令操作,但在实际的测试操作中不可避免的问题如下:

(1)在 Shift操作中,Hold_EN=0,CFI直通CFO端;Hold_EN=1,CFO输出WBR中的数据,在数据移位过程中CFO总经受新移入数据的影响。而对于输入端WBR单元,CFO直接影响到内核输入端,对于输出端WBR单元,CFO直接影响到相连的外接电路,即在Shift操作中CFO端具有不安全性输出,可能会对电路造成破坏。

(2)选择器Mux2的选择信号Hold_EN=1时,Shift操作和Update操作的条件重合,导致每一步Shift操作均伴随着Update操作,Update操作缺乏可控性,给测试操作带来极大的不便。

(3)在Capture操作中,CFI端信号需在传递到CFO端后方可被捕获进WBR单元,这给CFO带来不必要的信号变化,同样有不安全性的问题。

文献[13]中改进设计的WBR单元如图4所示,加入了安全值选择器Mux3。但Mux2的选择信号设计为UpdateWR,涵盖了对Update操作、Capture操作的控制,在诸多应用场合受到一定的限制。

图4 文献[13]设计的WBR单元

文献[14]中改进设计的WBR单元如图5所示,加入D触发器FF2用于执行Update操作。此设计方案存在的问题是:在WRCK上升沿总会触发Shift操作、Capture操作之一,虽然本身支持Shift操作、Cap⁃ture操作、Update操作没有问题,但当WSC接口信号控制的其他WBR单元(可在同一个或多个Wrapper中)需要执行Update操作或Transfer操作时,此设计方案的WBR单元将错误发生Capture操作。因此,应当避免Shift操作、Capture操作在WRCK上升沿作用下的“互补关系”。

图5 文献[14]设计的WBR单元

文献[15]同样对WBR单元的设计作了改进,但仍然仅是一种设计方法,由于被测对象端口的工作时序复杂程度不同,单纯一种WBR单元的设计方法有待改进。本文在IEEE Std 1500的基础上,分别设计1位移位长度的WBR单元和2位移位长度的WBR单元,其中1位移位长度的设计如图6所示,D触发器DFF_1构成CTI与CTO之间的1位移位单元。

图6 1位移位长度的WBR单元

图6中,DFF_1负责响应Shift操作或Capture操作,DFF_2负责响应Update操作。Work_Mode信号由WRSTN和相关指令(WS_BYPASS等)控制,用于选择“正常工作”或“测试工作”状态。本文所设计的WBR单元具备安全和钳位功能,在WS_SAFE测试指令有效时,CFO输出安全值Safe_Value,在WS_CLAMP指令有效时,CFO钳位输出WBR单元值(即DFF_1的存储值)。

根据本文前述分析,资源节点在某一特定时序下完成工作时,功能设置和时钟等特殊功能端往往需要在“0”和“1”之间多次反复切换。使用Wrapper对此类资源节点进行测试时,移入一组测试数据后,仅因为需要将功能设置端或时钟输入端WBR单元中的值“由0变1”或“由1变0”,就需要再次移入测试数据,而新移入的测试数据仅在这些特殊位上有变化,重复的串行移位显然会耗费过多的测试时间。为提高测试效率,本文为此类特殊功能端设计图7所示的2位移位长度的WBR单元。

图7 2位移位长度的WBR单元

图7中,DFF_3和DFF_1构成CTI和CTO之间串联的两位移位单元,其中DFF_1扮演“主要”操作单元,DFF_3扮演“预备”操作单元,Transfer操作可实现DFF_1和DFF_3中数据的交换。例如,假设测试数据移入后,DFF_1中为0,DFF_3中为1,Update操作可使CFO端为0,触发Transfer操作,DFF_1中变为1,DFF_3中为0,再进行Update操作即可使CFO端为1,即实现了CFO端由0到1的变化,与此类似,特殊功能端的复杂时序输入即可通过多次Transfer操作实现,而减少测试矢量序列的代价仅仅是测试矢量长度的少量增加。

3.3 IEEE 1500 WIR设计

指令寄存器WIR用于校验测试指令码,配置WBR、WBY,其组成结构包括指令码移位寄存器、指令码译码逻辑、指令更新寄存器。如图8所示,WIR受WSC端口信号控制,在指令寄存器选择信号Se⁃lectWIR=1时,指令码移位寄存器位于WSI-WSO之间的移位路径中,指令码经WSI串行移入或经WIR_PI并行捕获,译码逻辑译码产生的Wrapper指令被指令更新寄存器更新锁存后,新指令对Wrap⁃per的配置有效。

图8 WIR寄存器及工作结构

本文设计的Wrapper指令及其功能如表2所示。表中IF模式是指在INTEST指令的配置下,资源节点的输入端由WBR控制,输出端由WBR观测,OF模式是指在EXTEST指令的配置下,Wrapper功能输出端WFO由WBR控制,Wrapper功能输入端WFI由WBR观测。

表2 Wrapper指令

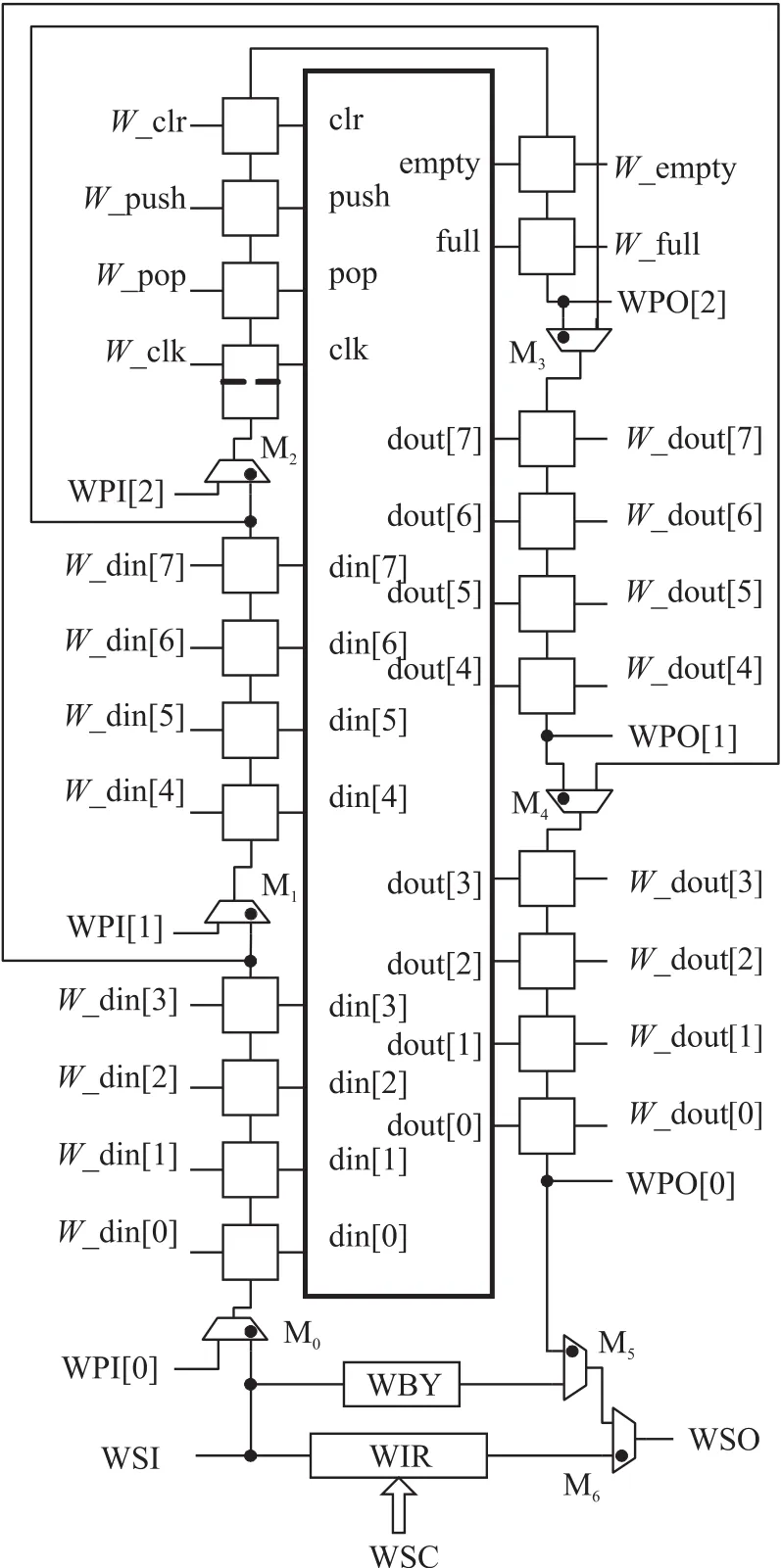

3.4 LIFO资源节点Wrapper设计

实验为10 byte的堆栈(LIFO)资源节点设计的Wrapper如图9所示,其中clk端是2位移位长度的WBR单元,其余是1位移位长度的WBR单元。

指令对Wrapper的配置通过7个二选一选择器实现,如图9所示M0~M6,标有黑原点的输入端在选择信号为1时选通。Wrapper指令对M0~M6的配置如表3所示,其中“X”表示任意。

图9 LIFO资源节点Wrapper设计

表3 Wrapper指令的配置数据

4 实验结果分析

本文以10 byte的LIFO为实验对象,分别进行正常工作、测试工作的实验。正常工作的实验截图如图10所示,压栈状态(W_push=1)下,在10个W_clk时钟作用下,10 byte数据依次压入栈中,栈指针IP_sp从递增到4′ha时,栈满信号W_full置1;出栈状态(W_pop=1)下,在10个W_clk时钟作用下,10 byte数据依次出栈,栈指针IP_sp递减到0时,栈空信号W_empty置1。实验表明,在设计了IEEE 1500 Wrapper后,LIFO资源节点的正常工作未受影响,此时Wrapper默认处于旁路模式(WS_BYPASS=1)。

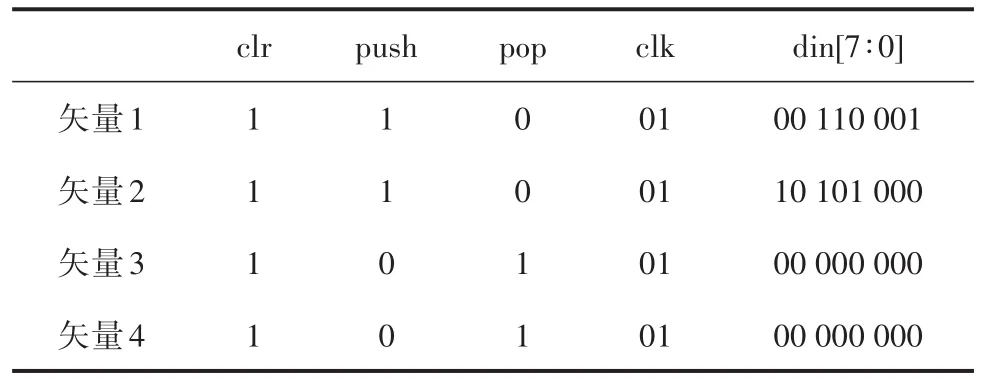

LIFO测试工作实验如图11所示,测试矢量如表4所示。WS_INTEST指令(0001)以低位优先方式移入Wrapper并更新有效后,在Shift操作状态下将表4中的矢量1移入Wrapper WBR单元,经过“Update-Transfer-Update”的操作,字节31h被压入栈中,再以同样方式将矢量2中的A8h压入栈中。在矢量3移入Wrapper,经过“Update-Trans⁃fer-Update-Capture”的操作,输出端WBR捕获到出栈数据A8h,矢量4施加后,输出端WBR捕获到出栈数据31h。实验表明,本文所设计Wrapper能够能够准确无误的对LIFO资源节点进行测试。

图10 LIFO资源节点正常工作实验

图11 LIFO资源节点测试工作实验

表4WS_INTEST测试矢量

本文针对LIFO的时钟端设计2位移位长度的WBR单元,而对其他端口设计1位移位长度的WBR单元,相比目前常见的纯1位移位长度的设计方案,本文的优势如表5所示。由于入栈、出栈的次数相同,表中N为偶数;测试时间指WRCK时钟数,计算范围是在移入测试矢量到捕获测试响应之间,目的是比较设计方案的差异性部分。

表5 设计方案的优劣比较

由表5可见,在LIFO测试矢量L=12的情况下,本文设计方案的测试时间相比纯1位长度WBR的方案减少10N个WRCK时钟,随着N的增大,本文的测试时间优势更加显著。所以,本文对LIFO的时钟端设计2位移位长度的WBR单元,可减少测试时间,提高测试效率。

在N固定,L大于等于3时,本文的设计方案即具有时间优势,且随着L的增大,优势逐渐增大,由于在一般情况下资源节点输入端的数目不会少于3,所以对任意资源节点应用本文的设计方案均有实质性的测试时间优势。此外,对功能复杂的资源节点,时钟端、功能设置端均设计2位移位长度的WBR单元后,可以更大程度上减少测试时间。

5 结论

资源节点的测试是NoC测试的主要热点问题之一,且由于资源节点各不相同,如何构建统一的测试机制成为首要问题。本文分析了可能的测试方法,选择为资源节点进行IEEE 1500 Wrapper可测性设计,并通过对资源节点测试特征的分析,提出可针对资源节点不同端口工作时序复杂程度不同的特征设计不同的WBR单元。以LIFO资源节点为例的实验表明,设计IEEE 1500 Wrapper能够有效地对资源节点进行测试,而且本文的Wrapper设计方法相对目前常见的设计方法能够有效缩短测试时间,具有一定的实用价值。

[1]高明伦,杜高明.NoC:下一代集成电路主流设计技术[J].微电子学,2006,(4):461-466.

[2]欧阳一鸣,韩倩倩,梁华国,等.面向非全互连3D NoC可靠通信的分布式路由算法[J].计算机辅助设计与图形学学报,2014,(3):502-510.

[3]Sayankar B B,Agrawal P,Dorle S S.Routing Algorithms for NoC Architecture:A Relative Analysis[C]//International Conference on Emerging Trends in Engineering and Technology,ICETET,2013:105-106.

[4]Ouyang Yiming,Han Qianqian,Liang Huaguo,et al.A Distribut⁃ed Routing Algorithm for Reliable Communication in Vertically Partially Connected 3D NoC[J].Jisuanji Fuzhu Sheji Yu Tuxingx⁃ue Xuebao/Journal of Computer-Aided Design and Computer Graphics,2014,26(3):502-510.

[5]许川佩,姚芬,胡聪.基于云进化算法的NoC资源节点优化测试研究[J].电子测量与仪器学报,2012,(3):192-196.

[6]方亮亮,胡庆生.基于HERMES NoC的片上网络容错方法研究[J].电子器件,2010,(1):27-31.

[7]欧阳一鸣,贺超,梁华国,等.NoC架构下异构IP核的并行测试方法[J].电子学报,2013,(12):2391-2396.

[8]IEEE Std 1149.1-2013,IEEE Standard Test Access Port and Boundary-Scan Architecture[S].IEEE,2013.

[9]IEEE Std 1500-2005,IEEE Standard Testability Method for Em⁃bedded Core-Based Integrated Circuits[S].IEEE,2005.

[10]韩可,邓中亮,闫华.基于边界扫描技术的Flash测试技术研究[J].电子器件,2008,31(2):568-571.

[11]邓中亮,韩可,邹德君.基于并行机制的边界扫描技术[J].电子器件,2008,31(5):1611-1614.

[12]ILVA Francisco da,MCLAURIN Teresa,WAAYERS Tom.The Core Test Wrapper Handbook:Rationale and Application of IEEE Std.1500[M].2005.147-155.

[13]谈恩民,金锋.基于IEEE 1500标准的嵌入式ROM及SRAM内建自测试设计[J].微电子学与计算机,2013,(7):115-119.

[14]李广进,陈圣俭,牛金涛,等.数字IP核的IEEE Std1500外壳架构设计研究[J].微电子学与计算机,2012,(10):42-46.

[15]孙元,颜学龙,李鹏.基于IEEE Std1500标准的互连检测构架设计[J].电子器件,2013,36(5):618-622.

王建喜(1989-),男,汉族,江苏东台人,桂林电子科技大学在读硕士,主要研究方向为集成电路测试理论与技术,mzfx⁃wjx@163.com;

许川佩(1968-),女,汉族,广西合浦人,桂林电子科技大学硕士研究生导师,博士,教授,主要研究方向为集成电路测试理论与技术,xcp@guet.edu.cn。