基于Verilog HDL的IIC总线IP核设计

朱诚诚,石晶晶,陈 斯,张 萌

(1.东南大学电子科学与工程学院,南京 211189;2.东南大学国家ASIC中心,南京 210096)

IIC总线是PHILIPS公司开发的一种实用、双向、同步串行通信标准[1-2],目的在于解决各个串行设备间的通信,具有接口线数目少、通信效率高等优点。通用的IIC总线接口器件在视频处理、移动通信等领域的应用已经非常普遍。除此之外,IIC总线接口器件,如带IIC总线RAM,ROM,A/D,D/A等,也越来越多地应用于计算机及自动化控制系统中。

设计的IIC总线IP核仅需要两条总线线路,一条串行数据总线SDA,一条串行时钟总线SCL。连接到相同总线的IC数量只受总线的最大容量400 pF限制,是一种多主机总线[3]。串行8 bit双向数据传输位速率,在标准模式之下可达到100 kbit/s,快速模式之下可达400 kbit/s,高速模式下可达到3.4 Mbit/s。从设计IIC总线的顶层模块开始,在实现IIC总线传输的全部功能之后,将IIC总线模块以固核的形式封装。基于所设计的IIC总线IP核,只需将外部PAD引线端与IP核接口相连就可以很便捷地进行IIC通信。

采用硬件描述语言(HDL)[4-5]进行IP核设计,硬件描述语言是一种形式化方法来描述数字电路和设计数字逻辑系统的语言,它是硬件设计人员与EDA工具之间沟通的桥梁,用来编写设计文件,建立电子系统行为级的模拟类型。之所以选择Veril⁃og HDL,是因为Verilog HDL更加简洁明了,灵活高效,完成同一功能Verilog HDL的程序条数一般只为VHDL的1/3。此外,Verilog HDL在底层描述,即开关级描述方面比VHDL功能更强。

此外,在Xilinx ISE V13.4设计平台上进行IIC总线IP核的设计,设计更加便利化。

1 IIC总线的IP核设计

1.1 IIC总线的接口设计

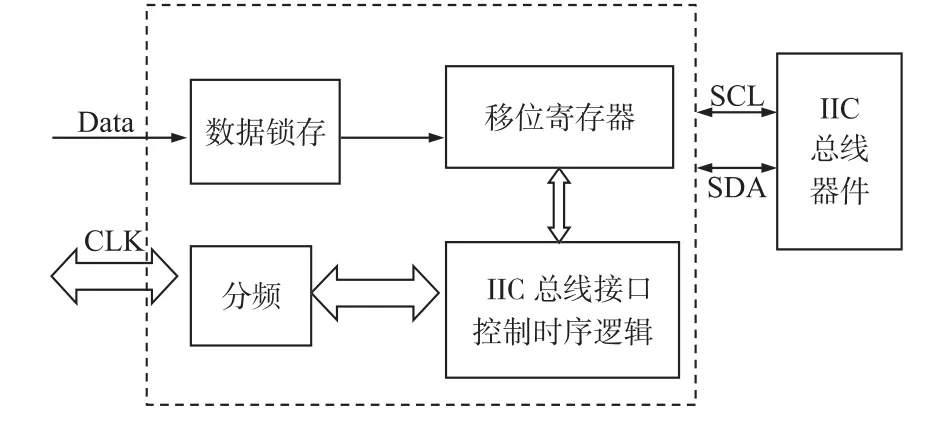

IIC总线接口主要包括以下4大单元,其框图如图1所示,图中SDA为串行数据线,SCL为串行时钟线,Data为传输数据,CLK为处理器时钟频率。

分频器 由FPGA的锁相环输出的稳定时钟信号,由于频率很高,所以必须经过分频模块从而输出满足IIC总线要求的传输速率。

IIC总线接口控制时序逻辑块 IIC总线数据传输的所有时序控制逻辑都由它产生,是这个IIC模块的核心。

数据锁存器 根据读写使能信号(r/w)存储IIC己接收的或待发送的数据。

移位寄存器 在时序控制逻辑模块的控制下,根据读写使能信号(r/w)对数据进行正确地处理。

图1 IIC总线接口框图

1.2 读写功能的实现

写操作[6-7]过程:

①主端向总线发送一个开始信号;

②主端向总线发出需要写数据器件的器件地址以及写信号并等待器件产生应答信号;

③主端向总线发送所要写的存储地址并等待设备产生应答信号;

④主端向总线发送所要写的数据;

⑤等待器件产生应答信号,主端向总线发送结束信号,完成一个字节的写过程。

IIC总线写操作的功能是将数据写入到总线上,即将并行数据装换为串行数据。

读操作过程:

①主端向总线发送开始信号;

②主端向总线发送要读数据器件地址以及写信号并等待器件产生应答信号;

③主端向总线发送所要读数据的地址并等待产生应答信号;

④主端向总线发送开始信号和所需读数据器件的器件地址以及读信号并等待器件产生应答信号;

⑤主端按从高到低位的顺序接收总线上的数据;

⑥产生停止信号结束数据的读取。

IIC总线的读操作的功能是读取总线上的串行数据,即将串行数据转换为并行数据。

1.3 IP核设计

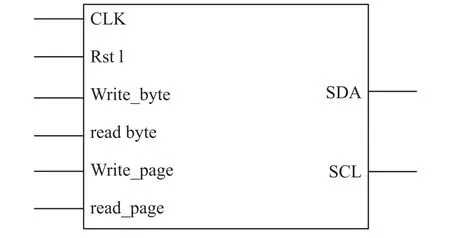

设计的IIC总线的单主IP核,能够实现读写操作及连续地址的读或写操作(图2),由于它是单主模式,故总线没有竞争与仲裁。

图2 IIC总线IP核简图

IP(Intellectual Property),即知识产权。它是一段硬件描述语言程序,具有特定电路功能,是指可用来生成 ASIC(Application Specific Integrated Cir⁃cuit)和PLD的逻辑功能块,且该程序与集成电路工艺无关,它可以移植到不同的半导体工艺所生产的集成电路芯片。本文设计的IP核中,rst_n为复位信号,当rst_n为低电平时,IIC总线处于空闲状态,此时无数据的传输;syn_sign为同步信号,当syn_sign为高电平时,IIC总线可以进行数据的传输,否则,IIC总线处于空闲状态;Byte_Write为写信号,当其为低电平时,IIC总线可以进行写操作;Byte_Red为低电平时,IIC总线可以进行读操作;Page_Write为低电平时,IIC总线可以进行连写操作;Page_Red为低电平时,IIC总线可以进行连读操作。

1.4 IIC总线状态机转换

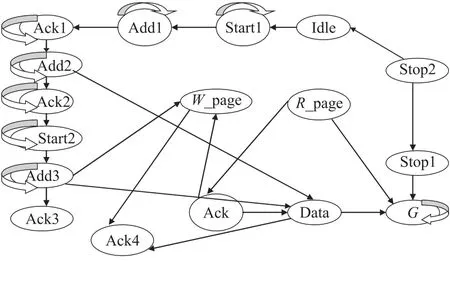

由IIC总线传输协议可知,IIC在传输过程中存在着几个固定的状态[8],因此采用同步状态机来设计IIC模块。主状态机从的大的方面共有5个状态:空闲,开始,发送数据,接收数据,停止。

所设计的总线状态机转移图如图3示。

图3 状态机的转换示意图

当无数据传输时,IIC总线处于空闲状态(Idle),IIC总线在起始信号(Start)的触发下,开始进行数据的传输。首先,总线接受器件地址,在得到应答信号(Ack)后,传输数据存储地址,在接到应答信号后,开始传输数据(Data)。若无连写(W_page)、连读(R_page)信号的输入,总线在读写后将会处于空闲状态,并等待下一次起始信号。

基于这种状态机的转换,总线按照设计者的要求进行数据传输。

2 仿真和实现

采用自上而下的流程对IIC总线主模块进行设计,对所有模块用Verilog HDL语言进行描述,在ISE V13.4和Basys2设计平台上进行仿真与硬件验证。ISE V13.4是Xilinx公司的FPGA集成开发环境,不仅包括逻辑设计所需的一切,还具有大量简便易用的内置式工具和向导,使得I/O分配、功耗分析,HDL仿真等步骤变得简单而直观。围绕着Xilinx Spartan-3E现场可编程门阵列,Basys2板提供完整的、随时可用的硬件适合电路实现从基本逻辑器件到复杂的控制器。拥有一系列板上I/O设备和所有需要支持的FPGA电路,可以创造无数无需任何其他元件的设计。

2.1 仿真检测

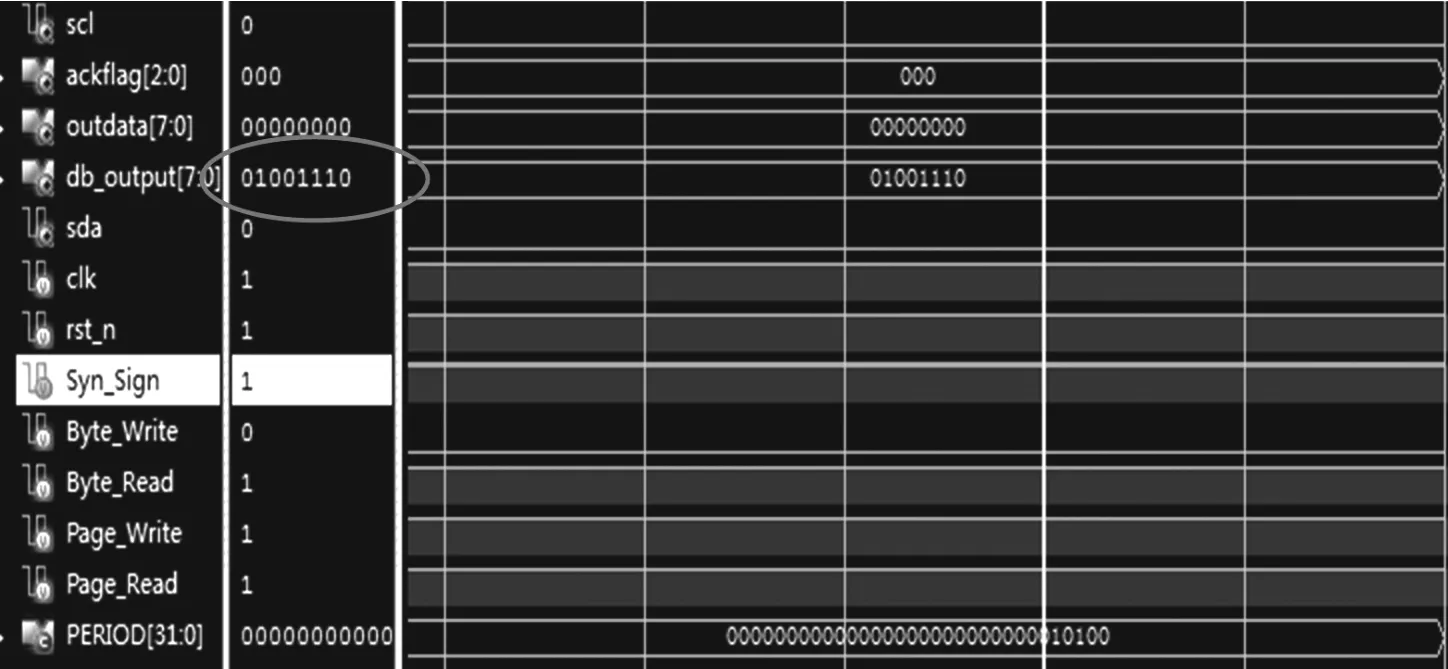

首先,将写操作信号Byte_write置0,主端检测到写信号后,开始写操作,在往总线上写入器件地址并接收应答信号后,主端向总线写入数据01 001 110,图4为写操作仿真图。

通过仿真波形,我们从模块正确写入一个字节01 001 110。

将读操作信号Byte_read置0,主端检测到读信号后,开始读操作,在完成伪写操作后,主端从总线读出数据01 100 101。

通过仿真波形可以看出,我们可以从总线读出一个字节01 100 101。

仿真结果与理论结果相一致,数据传输速率达到100 kbit/s,快速模式下可达到400 kbit/s,高速模式3.4 Mbit/s。

图4 写操作仿真

图5 读操作仿真

2.2 硬件测试

仿真完成后,在ISE13.4设计平台上进行综合布线,并采用Basys2中进行硬件测试,将复位信号置0,同步信号置1,写信号置0,将主端写入的总线数据通过Basys2的LED灯进行显示,图6为写操作。

通过LED显示,我们成功向总线写入一个字节0 100 1110。

将复位信号置0,同步信号置1,读信号置0。

并将从总线上读出的数据通过Basys2的LED灯进行显示,图7为读操作。

图6 硬件写操作

图7 硬件读操作

通过LED显示,我们成功读出总线上一个字节01 100 101。

仿真、硬件检测结果与IIC总线传输数据的预期结果相一致,从而说明了我们IIC总线设计的成功。最后,在ISE设计平台上将IIC总线模块进行封装,形成只有接口的IP固核。

3 结束语

采用Verilog HDL语言设计了一个IIC总线的单主模式的IP核,给出了一种模块化和层次化的完整设计方法。该IP核具有通用的接口和简单的操作时序,并且全部设计由Verilog HDL语言实现。无需代码修改就可以在片上系统的接口设计中使用,实现对IIC总线的支持,具有良好的移植性。

与近期的同类IIC总线IP核设计相比较,有别于Altera的Quartus II平台的设计,在Xilinx ISE V13.4设计平台上进行IP核的设计。ISE V13.4提供了便捷地IP核设计环境及仿真环境,进而使得设计便利化。此外,ISE为Xilinx公司的开发环境,Xilinx的产品市场占有率更高,因此,在ISE平台上设计使得所完成的产品更具实用性。

设计的IP核既体现了良好的可移植性,又体现了芯片设计的模块化思想。利用成熟的IP核进行新产品的开发可大大缩短设计周期,提高产品的可靠性,为新产品赢得市场契机。

[1]张延伟,杨金岩,葛爱学,等.Verilog HDL程序设计实例详解[M].人民邮电出版社,2008:132-160.

[2]Philips Semiconductors.The IIC-Bus Specification[M]Version 2.1,2001:6-19.

[3]夏宇闻.Verilog数字系统设计教程[M].2版.北京:高等教育出版社,6.1,2008:13-18.

[4]刘欲晓,方强,黄宛宁,等.EDA技术与VHDL电路开发应用实践[M].北京:电子工业出版社,2009:221-240.

[5]张延伟,杨金岩,葛爱学等.Verilog HDL程序设计实例详解[M].人民邮电出版社,2008:132-160.

[6]赵辉.IIC总线技术及其应用实例[J].微型电脑应用,2005,21(4):61.

[7]刘福奇,刘波.Verilog HDL应用程序设计实例精讲[M].北京:电子工业出版社,2009:434-444.

[8]陈旭.FPGA技术发展研究[J].半导体技术,2006,(4):1-3.

朱诚诚(1992-),男,汉族,安徽淮南人,本科生,就读于东南大学电子科学与工程学院,ccz2498466@163.com;

张 萌(1964-),男,汉族,研究员,东南大学ASIC中心,主要从事数字信号处理,集成电路设计,通信系统等,zmeng@seu.edu.cn。