基于DSPBuilder的正交矢量型数字锁相放大器实现

陈宇泽 邢维巍 樊尚春

摘 要: 微弱信号检测技术在当今科学研究领域必不可少,其中锁相放大技术由于在速度和精度这两个方面都能达到很高的要求,因而在微弱信号检测领域得到大量使用。使用DSP Builder可以更加方便高效地进行设计。以DSP Builder软件为工具,介绍了正交矢量型数字锁相放大器各个模块的设计,并对整体设计进行了验证,仿真结果证实设计可行。

关键词: 微弱信号; 锁相放大器; DSP Builder; 正交矢量

中图分类号: TN911.7?34 文献标识码: A 文章编号: 1004?373X(2015)01?0062?04

Abstract: Nowadays the weak signal detection technology is necessary in scientific research field, in which the phase?locked amplifying technology is widely used in the field of weak signal detection because it can meet the requirements of high speed and high accuracy. DSP Builder software is adopted as a tool since DSP Builder can make the design more conveniently and efficiently. The design of each module in orthogonal vector type digital phase?locked amplifier is introduced in this paper. The overall design was verified. The simulation results confirm that the design is feasible.

Keywords: weak signal; lock?in amplifier; DSP Builder; orthogonal vector

0 引 言

科学研究和工程领域难免会遇到微弱信号的检测。对于各种微弱的被测量,一般都是通过相应的传感器将其转换为微电流或低电压,再经放大器放大。但是由于外界干扰比有用信号的幅度大得多,放大被测信号的同时也放大了噪声,因此只靠放大是不能把微弱信号检测出来的。只有在有效地抑制噪声的条件下增大微弱信号的幅度,才能提取出有用的信号。

锁相放大作为微弱信号精确检测的一种有效方法,在速度和精度上都能达到很高的要求。它的基本原理就是利用被测信号和参考信号的互相关检测原理对信号进行窄带化处理,有效地滤除噪声干扰,完成对信号的检测。同时锁相放大器还具有中心频率稳定、通频带窄、品质因数高等优点,因而在科学研究和工程的各个领域都得到广泛的应用。

1 锁相放大器原理

1.1 锁相放大原理

锁相放大器的基本结构如图1所示,包括信号通道、参考通道、相敏检测器(PSD)和低通滤波器(LPF)等。

信号通道对调制正弦信号输入进行交流放大,将微弱信号放大到足以推动相敏检测器工作的电平,并且要滤除部分干扰和噪声。参考通道对参考输入进行放大,以适应相敏检测器对幅度的要求。参考通道的另一个重要功能是对参考输入进行移相处理,以使各种不同相移信号的检测结果达到最佳。

PSD以参考信号[r(t)]为基准,对有用信号[x(t)]进行相敏检测,从而实现频谱迁移,再经过LPF滤除噪声,其输出对输入信号的幅度和相位都敏感,这样就达到了既鉴幅又鉴相的目的。因为LPF的频带可以做得很窄,所以可使锁相放大器达到较大的信噪改善比。

1.2 正交锁相放大原理

正交矢量型锁相放大器需要两个相敏检测系统,它们的信号输入是同样的,但两个参考输入在相位上相差90°。如图2所示,同相通道中PSD1输入为正弦参考信号,正交通道中PSD2输入为余弦参考信号。

2 数字锁相放大器的设计

本文采用DSP Builder进行数字锁相放大器的设计。DSP Builder能够在算法友好的开发环境中帮助设计者生成DSP设计硬件表征,从而缩短设计周期,降低设计的难度。

2.1 DSP Builder简介

DSP Builder是ALTER公司于2002年推出的一个系统级设计工具,它构架在多个软件工具之上,并把系统级和RTL级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势。DSP Builder以Matlab的图形设计平台Simulink为载体,以Blockset方式呈现,同时通过Signal Compiler把设计文件转成相应的硬件描述语言VHDL设计文件以及用于控制综合与编译的TCL脚本;对后者的处理可以由FPGA开发工具Quartus Ⅱ来完成。

2.2 参考信号设计

2.4 低通滤波设计

使用DSP Builder设计FIR滤波器时,先设计一个较为低阶的子模块,然后反复调用并连接该模块,最后添加分析计算得到的系数,就能设计出一个完整的FIR滤波器波形。本次设计的直接I型64阶FIR滤波器通过反复调用4次16阶FIR滤波器实现。一个16阶的直接I型FIR滤波器主要由输入模块、输出模块、延迟模块、乘法模块和加法模块组成,如图7所示。

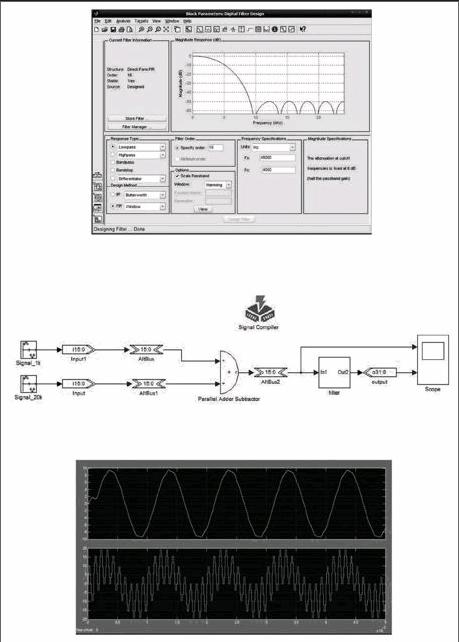

低通滤波器系数的生成是使用 Matlab 工具箱中的滤波器专用设计工具Filter Design and Analysis Tool(FDA Tool)实现的,FDA Tool能够根据需要设计各种类型的滤波器。在此设计中,通过分析和对比,采用哈明窗函数法设计FIR低通滤波器,设计采样频率为48 kHz,截止频率为4 kHz。FDA Tool设计的滤波器界面如图8所示。

利用 DSP Builder的层次设计方法将64阶FIR滤波器构成子系统,在Matlab的Simulink环境下,验证直接I型64阶FIR滤波器滤波功能的图形模块,如图8所示。设计中输入了两个频率分别为1 kHz和10 kHz,幅度大小均为10的正弦信号。图9为两个正弦信号的叠加和滤波器的输出波形,从输出结果中可以明显地看到10 kHz的信号被很好地滤除掉了。图10为64阶FIR低通滤波器输出结果。

2.5 锁相放大器的仿真建模

利用DSP Builder的层次设计方法,根据正交锁相放大原理,将参考信号产生模块和乘法器、滤波器模块连到一起构成正交矢量型数字锁相放大器。仿真模型如图11所示。

从图13可以看出,噪声被很好地滤除掉了,输出的结果只剩下了有用信号和参考信号产生的差频信号,证明系统是可行的。

3 结 论

DSP Builder大大提高了数字锁相放大器的设计效率,并且能够很好地抑制噪声。但这只是在Simulink中进行了系统级的仿真,后续的工作包括把设计文件转成相应的硬件描述语言VHDL设计文件以及对生成的VHDL文件进行功能仿真。功能仿真需要在Quarus Ⅱ软件中完成,然后根据仿真结果修正设计模型;最后将编译好的设计文件下载到FPGA器件中,进行硬件测试,实现硬件设计。

致谢:感谢长江学者和创新团队发展计划(IRT1203),惯性技术国防科技重点实验室的资助。

参考文献

[1] PAN Song, HUANG Ji?ye. EDA technology and VHDL [M/OL. [2011?09?16]. http:// www.pudn.com/downloads.

[2] DIXON P K, WU L. Broadband digital lock?in amplifier techni? ques [J]. Review of Scientific Instruments, 1989, 60(10): 3329?3336.

[3] GASPAR J, CHEN S F, GORDILLO A, et al. Digital lock in amplifier: study, design and development with a digital signal processor [J]. Microprocessors and Microsystems, 2004, 28(4): 157?162.

[4] 高晋占.微弱信号检测[M].北京:清华大学出版社,2004.

[5] 朱瑞.锁相放大器及其应用介绍[J].国外电子元器件,2005(1):75?76.

[6] 郭金淮,汤汉屏.DDS 技术浅析[J].数据通信,2002(3):50?52.

[7] 黄爱蓉.高性能DDS信号产生器的设计研究[J].微计算机信息,2005,21(8S):153?156.

[8] 高耀鸿.基于FPGA的FIR低通滤波器[D].长沙:湖南大学,2012.

[9] 杜勇,路建功,李元洲.数字滤波器的Matlab与FPGA实现[M].北京:电子工业出版社,2012.