基于CPLD的多功能数字时钟实现

何有为 沈祖斌 邹光毅

(江汉大学数学与计算机学院,湖北 武汉430056)

1 整体设计方案

本系统采用最原始的原理图设计方案,采用原理图设计能最大限度的了解内部电路结构,了解其中的原理构造,清晰易懂,而且在一定程度上很好的强化与锻炼了“数字逻辑”知识。在一般的简易时钟基础上有了比较明显的改进。如图1所示,是该时钟的整体实现框图,实验板采用CPLD芯片EPM240,它是一个中规模的实验板,有很高的集成性,完全可以完成这个系统的需求。

图1 整体框图

该时钟的晶振源由实验板自带的50MHz晶振源提供,对50MHz分频得到1Hz的脉冲;然后对其计数,“秒钟”满60清0向分位进一,同样“分”满60进一到“时”,小时采用12小时制,故时满12清零。接着,使用刷新电路对其进行动态刷新,并通过数码管显示出来。对于校时部分,直接通过校时电路对分、时部分进行校时。最后,关于对控制电路的设计,控制电路通过使用模二进制的循环状态机实现四种模式循环,不同模式的控制,对模式信号进行处理,从而使MUX进行不同的选择实现显示以及闪烁。关于防抖部分,在每个按键输入处进行消抖处理即可。

2 数字钟模块实现

在确定整体思路基础后,进行模块化设计,采用模块化设计方便进行局部调整,以及模块的重用,便于开发,节省开发流程。对于该系统划分为以下几个模块去实现:①分频电路②秒钟计时电路③时钟计时电路④动态刷新和译码显示电路⑤控制电路⑥防机械按键抖动电路⑦闪烁电路⑧校时电路⑨功能选择电路。下面详细介绍控制电路、防机械按键抖动电路的实现。

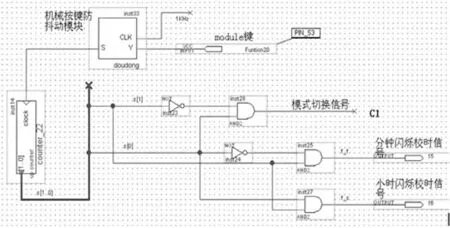

2.1 控制电路实现

控制电路是该系统能实现各种模式切换以及闪烁的重要部分。控制电路是本系统的核心电路,尽管结构简单但却有着“四两拨千斤”的作用。在控制电路中主要输出模式切换信号、闪烁信号、校时信号。决定了模式的状态和是否闪烁以及闪烁小时部分还是分钟部分。本系统设计了正常显示小时分钟、正常显示分秒、分钟校时闪烁、小时校时闪烁这四种状态,四种状态的实现通过一个状态机循环,即采用模二进制计数器。对应模式和模二计数器状态如下:M1正常显示小时分钟(S1S0=00)、M2正常显示分秒(S1S0=01)、M3分钟校时闪烁(S1S0=10)、M4小时校时闪烁(S1S0=11);模式切换信号分两种:①数码管上显示小时和分钟②数码管上显示分钟和秒钟;闪烁信号也分两种:①小时部分闪烁并校时②分钟部分闪烁并校时。需要模式切换信号①的模式有M1、M3、M4,需要模式切换信号②的模式有M2。使模式切换信号①为低电平;模式切换信号②为高电平,那么采用一定的逻辑电路便可完成高电平和低电平的分离,获取所需信号。采用的电路结构为S1与非门连接然后和S0相与得到切换信号C1,并将C1信号输出给MUX31_21,从而实现功能切换。

同理需要闪烁信号①的模式有M4,需要闪烁信号②的模式有M3,两种闪烁信号都不需要的模式有M1、M2。使需要闪烁时的状态为高电平,不需要闪烁时的状态为低电平。采用电路结构为,在M3模式下取闪烁信号为S0连接非门然后与S1相与得到高电平;M4模式下直接让S0和S1相与得到高电平,输出给闪烁电路和校时电路。由于闪烁时即代表该部分在校时,故闪烁电路和校时电路可以共用闪烁信号。既完成了对闪烁电路控制又完成了对校时电路的控制。控制电路的模二计数输入由外部定义的机械按键输入,该键即为module键。最后设计完成的控制电路原理图如图2所示,然后将其封装成模块,封装方法:选中电路图,File→Create/update→CreatesymbolfilesforcurrentFile保存即可。系统可直接调用封装好的模块。

图2 控制电路

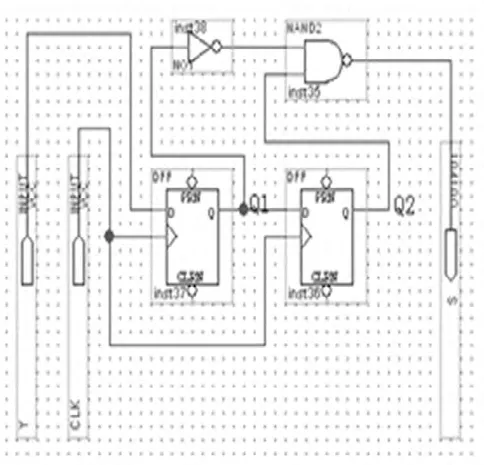

2.2 防机械按键抖动电路实现及效果

稳定可靠的信号输入是时钟系统能可靠工作的重要条件,我们不能将任何有毛刺的输入作为计时器的时钟信号,因此需要设计机械按键防抖动电路。该系统涉及到两个外部机械按键,要使它们每一次按下时都要产生单脉冲信号,以此提高可靠的信号。由于机械式开关的核心部件为弹性金属簧片,因而在开关切换的瞬问会在接触点出现来回弹跳的现象。虽然只是进行了一次按键,但在按键信号稳定的前后出现了多个脉冲,如图3按键波形图所示。为了确保按键识别的准确性,在按键信号抖动的情况下不能进入状态输入,为此就必须对按键进行消抖处理。实验开发板机械按键module键和check键常态下为高电平。如图4为去抖电路所示硬件消抖电路,当按键Y按下时产生抖动,此时若时钟脉冲CP的上升沿不来则两个D触发器的Q端不变,保持初始状态。设初始状态为Q1=Q2=0,输出。这时即使Y有抖动也不会影响输出,如图5消抖波形仿真图所示:

图3 按键波形图

图4 防机械按键抖动电路

图5 波形仿真

当第n个时钟脉冲CP的到来时,触发器DFF37翻转,Q1=1;DFF36不变,则S=1。当n+1个时钟脉冲到来时,DFF37不变,DFF36翻转,Q2=1,此时锁存Q1=Q2=1,则S=1。此时按下按键Y,在n+2个脉冲时钟到来时,触发器DFF36、DFF37维持不变。当按键Y松开时,D1=0,在第T个CLK脉冲到来时Q1=0,Q2不变,则S=0,产生了一个单脉冲信号。当第T+1个脉冲到来时,Q2翻转,此时S=1回到常态。当按键Y松开时,如果此时第m个时钟脉冲CP上升沿到来,Q1=1,Q2=0,则S=1。第m+1个时钟脉冲CP的上升沿带来时,Q1=1,Q2=1,则S=1。所以只要Y松开,即使有时钟脉冲出发,输出S仍保持不变。由此可得,按键Y按下一次,S端将获得一个与时钟脉冲同步的单次稳定脉冲信号输入给计数器。

这样就有效解决了抖动问题的情况,使得每一次按下外部机械按键时都只产生一个稳定的信号。为后面验证工作打下了很好的基础,保证了实际操作的准确性和灵敏度。

3 设计总结

本文介绍了采用原理图设计的方法,完成了数字时钟系统的设计。并在核心为EPM240T100C5的实验板上验证良好通过。数字时钟系统运行稳定,计时精准。注重设计时候的思想,采用自顶向下设计和模块化思想,是进行EDA设计的重要思想方法。锻炼学生动手操作能力,熟悉相关器件功能和工作方式。具有很好的综合锻炼能力。

[1]谢自美.电子线路设计·实验·测试[M].2版.武汉:华中科技大学出版社,2000.

[2]周润景.基于QuartusII的FPGA/CPLD数字系统设计实例(第一版)[M].北京:电子工业出版社,2007.