基于多层网络的片上网络可靠测试结构

俞剑明,周 炜,虞志益

(复旦大学专用集成电路与系统国家重点实验室,上海201203)

基于多层网络的片上网络可靠测试结构

俞剑明,周 炜,虞志益

(复旦大学专用集成电路与系统国家重点实验室,上海201203)

为解决片上网络测试问题,提出高可靠高并行度的片上网络测试结构。使用多层网络,在普通的片上网络上增加全局的广播网络和汇集测试结果的汇集网络。利用其冗余特性,有效保证测试部件的可靠性,同时提高并行度,节约测试时间。提出完备的路由器内测试方法,结合多层网络实现全面的片上网络测试。实验结果表明,该多层网结构在100核时的面积开销比内建自修复(BISR)结构减小56%,并且其测试时间比BISR结构减少85.8 %,测试覆盖率达到100%。

多核处理器;片上网络;多层网络;链路错误;控制错误

1 概述

Moore定律的不断发展带来了片上晶体管集成度的增加。同时随着处理器进入多核时代,片上集成处理器核数不断增加。在这样的趋势下,片上网络(Network on Chip,NoC)渐渐取代基于总线的SoC成为众核处理器的主流互联方式[1]。然而与此同时,芯片在制造过程中产生的缺陷也随之增多,在使用过程中由于材料老化、电迁移、压力迁移、电介质击穿、热载流子注入,负偏压温度的不稳定性等失效因素也导致缺陷的增加[2]。因此,多核网络的可测试性和容错设计成为了重要的课题。

企业界及学术界提出了许多片上网络的容错方法,这些研究主要是在假设错误模型的前提下进行分析[3]并采取对应容错方案。文献[3]使用的是随机错误注入的方式,使用SPICE模型进行仿真,获得错误信息。文献[4]将错误定义为链路错误,使用路由表的方法进行容错路由。文献[5]将路由器控制错误概括为32条规则,以低开销的并进检测电路对路由器的控制进行检错重发。

为了获得客观的错误模型,以及为了满足多核测试带来的复杂度增加,提出了全面可靠和高效片上错误测试方法。本文实现了文献[6]中的BISR测试结构,对SMIC 65 nm的片上网络芯片进行分析。在分析基础上提出了广播网络和汇集网络作为测试获得方法,在测试的面积开销以及并行度上有较大的改善。同时提出从控制、链路、存储以及软错多个角度对错误进行侦测的方法,以获得更高的测试覆盖率。

2 测试网络

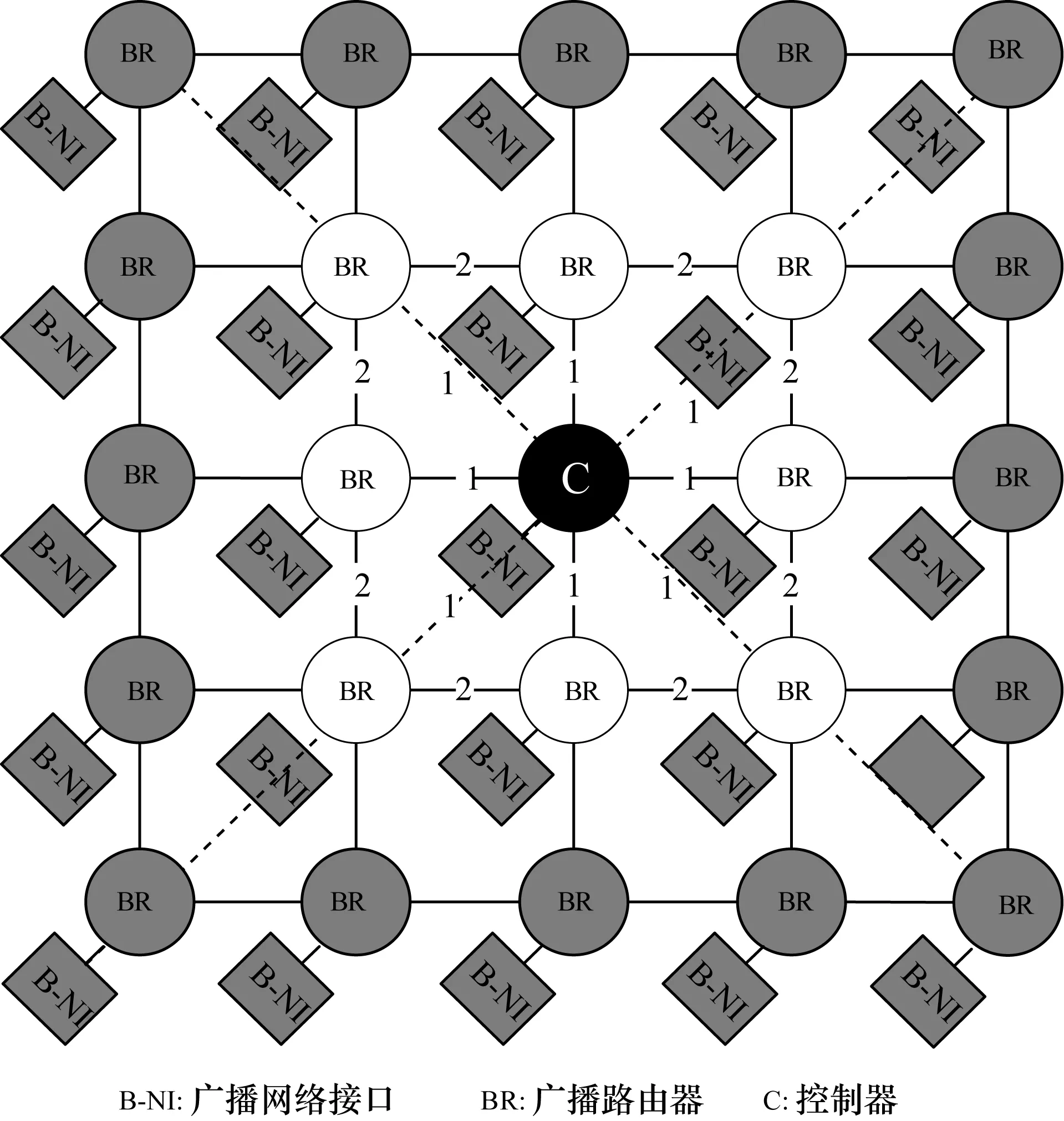

文献[7]等较多文献中将片上网络作为测试获得方法,从而对处理器进行并行测试。然而该方法是在片上网络正确工作的前提下进行的,无法保证测试向量的可靠注入和输出。文献[8]提出了多层次网络的概念,不同的通讯特性使用不同的网络进行通信,以达到最高的效率。受此启发,本文采用图1所示的三层网络以实现高效的以及高可靠的测试输入和输出方法。使用广播网络作为测试的输入以及测试的全局控制。利用广播通信一点(固定点)对多点的通讯特性,对网络的拓扑结构以及路由算法进行定制,以较小的代价获得较高可靠性和高的测试并行度。同时使用该广播网络控制下的汇集网络进行测试结果的输出,输出网络使用Flooding的路由,利用其冗余性,保证测试结果的正确输出。

图1 多层次网络测试的获得方法

2.1 广播网络

随着芯片集成度的不断增加,不仅对芯片设计提出了挑战,芯片的测试也成为了重要的问题。内建自修复(Build-in Self-repair,BISR)[6]采用外围测试环的方法间接地对片上网络进行链路的间接测试,测试向量顺序移位进入测试单元,测试单元之间进行数据发送,对结果进行比较以判断测试所经路径的链路状况。由于测试路径的有限性,在一些错误的分布下无法分辨出路径是否错误。同时串行的测试输入(10×10网络需要40个测试时钟周期),以及有限的单次可测试路径数(每次最多40条)使得该方案的测试时间较长。

同构多核处理器单核的一致性,实际上表明了其测试向量也可以相同,故本文提出一种广播网络作为测试的注入方法,以改善BISR结构中测试电路的不足。不同于普通2D-Mesh拓扑结构,考虑到广播通讯的通信为散射状的通信模式,本文设计对广播网络的拓扑结构调节为图2中的结构。在原本的2D网格拓扑的基础上增加了图中虚线所示的单向链路。从而将网络划分为多个层次:(1)图中黑色为第1层,主要为片外的FIFO接口以及广播控制电路。(2)白色的为第2层,灰色的为第3层,其他层次可类推。层与层之间通过增加的单向链路,使得各个层之间数据传输仅有一个网络跳步的延迟。这样的拓扑充分利用了广播通信模式的特性,对于一个N×N的网络原本节点间的最大间距为2N个跳步,而在该拓扑中减少为N/2(通信的源点固定在图中C节点)。

图2 用于测试输入的广播网络

测试电路本身的错误的引入也会造成测试结果的错误,所以保证测试电路的可靠性是极其重要的。本文采用的结构利用了时间冗余性来达到三模冗余的可靠测试输入。具体体现在其路由算法上:

(1)如图2中,第1个周期数据从控制器到达网络第2层(图中标1处),收到消息之后,第2层内各节点向相邻的节点进行转发。

(2)第2个周期之后,第2层各个节点将有3个消息,此时使用判决电路进行决策选择正确的结果,然后向下一层传输,如此反复。

这样的设计大大降低了测试网络可能出错的概率。虽然该方案使得广播网络的最大延迟变为原先的2倍,但是相比BISR,该广播使用的是系统内部时钟通常远快于BISR的测试输入时钟。同时数据传输在层与层之间的流水化,该方案在大量数据传输过程中带来的延时开销并不大。在硬件实现上由于广播网络的通信模式是固定的,在节点之间不会出现堵塞的情况,因此无需通常所用的FIFO进行数据缓冲。需要的仅仅是3组寄存器用于对收到广播包的寄存和一些裁决电路。

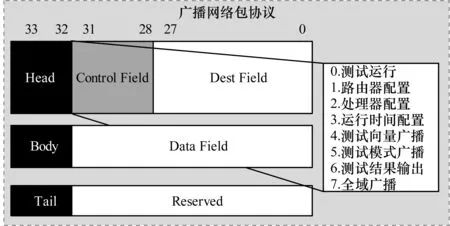

与2D片上网络常用的包结构类似,本文中的广播网络包也分为头包、体包和尾包。如图3所示,包的类型由最高的2 bit进行区分。头包中有4 bit的控制比特用于表明不同的测试状态,其中最后1 bit用于区分是否是全域广播,即是对所有节点广播或仅仅某些节点接收信息。第2种情况下会在接下来的体包中包含目的点的坐标,如此增加包结构的灵活性。图2中的B-NI是用于解析该包的网络接口。

图3 广播网络层包结构

2.2 汇集网络

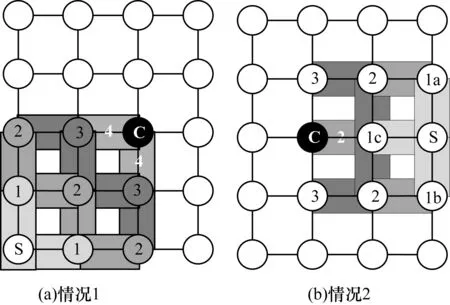

在保证测试向量正确注入的情况下还需要保证测试结果的正确输出。结果输出时的通讯模式具有如下特点,即:输出的目的节点固定为图4中的C节点,即一种汇集的通讯模式。因此,使用图4中所描述的路由算法。由前文提到的广播网络进行全局控制,使得在网络中同时只有一个节点在进行结果汇报。当源节点(S)和控制节点C节点的相对位置如图4(a)时,使用定向flooding算法进行路由,即如图4(a)所示的节点S同时向上和右发出2个包到达图中标志1的节点,接下来按照途中标识的编号顺序进行扩散传播。在第4个周期数据开始陆续到达C节点。可以看到数据由于扩散的效果将有较高的冗余度,这样可以保证输出结果的正确性。在图4(b)中的情况下,S节点和C节点具有相同的横坐标或者纵坐标,无法使用图4(a)中的方法进行数据的扩散。本文中的处理方式是S节点同时发出3个版本的数据到达1a,1b,1c这3个节点,然后1a, 1b节点按照图4(a)中的方法路由,而1c节点继续向C方向路由。

图4 汇集网络结构与路由算法

在测试时间和结果冗余度上做出权衡,可以控制接收冗余包的个数M,当收到结果数到达M时即可用广播网通知下一个节点进行汇报。这一方法通过在C节点中加入收包计数器进行设置。

3 路由器测试

片上网络路由器通常分为5级:(1)fifo读取; (2)路由计算;(3)通道仲裁;(4)开关(crossbar)传输;(5)链路传输[5]。同时错误类型还可以划分为硬错和软错[4]。完备的测试应该囊括各个方面。

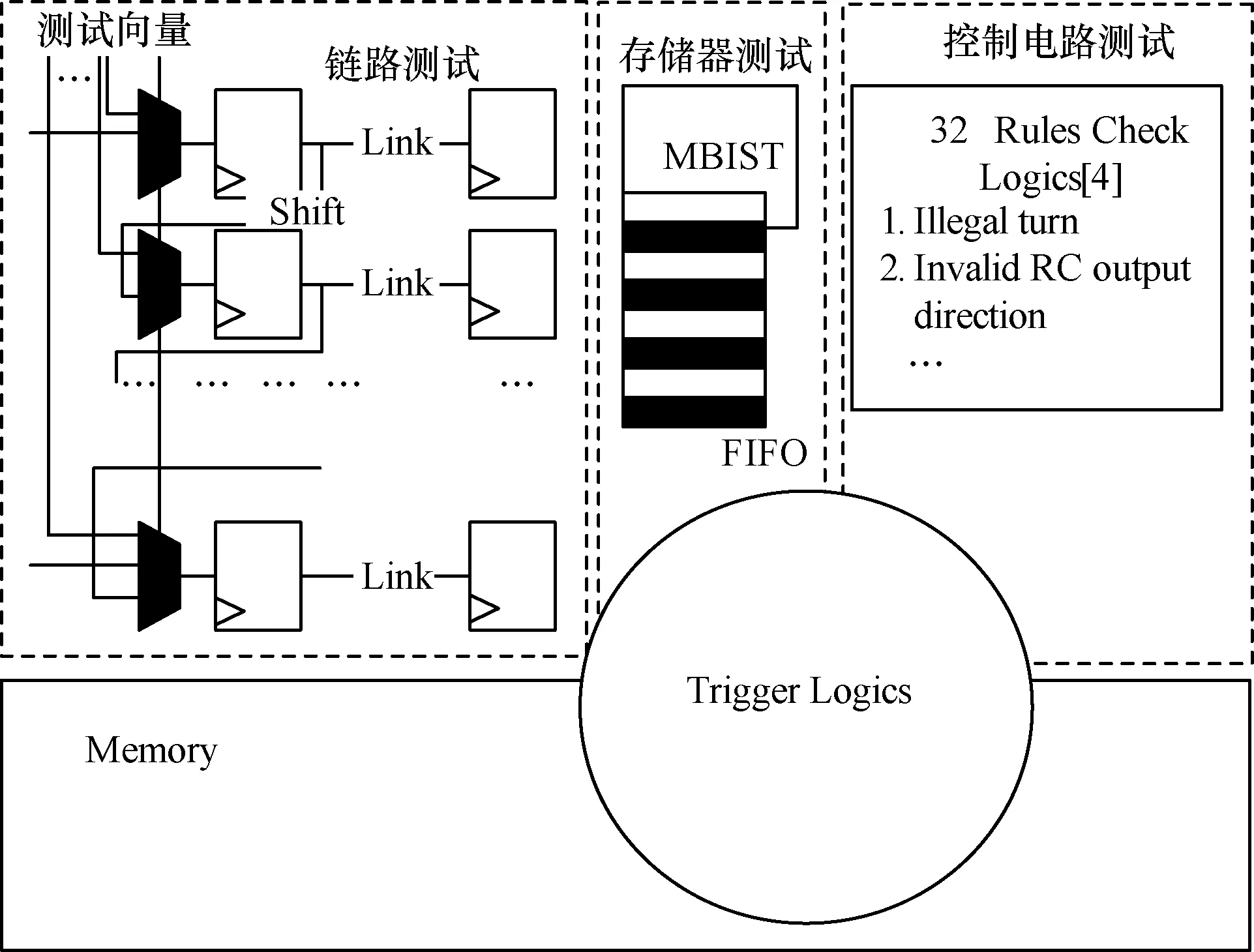

图5所示为本文提出的路由测试的结构。按照控制测试、存储测试、链路测试和软错测试4个方面对测试方法进行划分。

图5 片上网络路由测试结构

针对控制错误,文献[4]提出的以32条规则判断路由器中控制错误的状况,例如不允许出现路由算法中禁用的转弯方向,不允许出现无效的路由方向,每个通道一次只能有一个包占有等。以这样的规则并行判断带来的面积以及功耗开销小于3%而对关键路径的影响不到1%。

针对FIFO中出现的错误,使用BIST的方法[9-11]。

针对链路错误可使用图5中所示的方法[12],以广播网络发送本次进行测试的向量对链路两端的寄存器进行置外,然后进行相互的发送以及比较得出其判断结果。

3种测试方法通过触发逻辑(图 5中 trigger logics)与一个存储器连接。一旦错误发生就会触发存储器的写入操作。例如:当32条规则以32 bit独热编码,其中任何一个触发将使得相应控制信息和包的id等信息被写入存储器,链路以及memory类似。为节省存储器的写端口和面积,3种错误不同时测试。

在完成以上的硬件测试之后再在处理器之间互发数据进行软错误测试,以有效地将软错与硬错进行隔离。

4 性能评估

本文对多层次网络和BISR[6]进行了仿真及SMIC 65 nm HS的DC综合以进行比较,如图6所示。

图6 多层广播网络与BISR的测试时间与面积开销比较

如图6(a)所示,在核数在41×41核以下时由于多层网络利用广播和汇集2种固定的通信模式采用简单的无缓冲式的结构,在面积上相比BISR有优势。当核数增大,由于多层网络的面积开销是与核数成正比的增长,而BISR的面积正比于核数的开根号,在核数大于41×41时BISR的面积会较小。但是在测试时间上多层网络由于其高并行性有着明显的优势,如图6(a)及图6(b)所示在100核情况下多层广播网的测试时间不到BISR的14.3%。并且从测试的可自动化角度,多层网络结合本文中所示的测试电路也优于BISR。BISR的测试方法是一种间接的测试方法,覆盖率依赖于错误分布,在较悲观情况下覆盖率仅有70%。而本文通过广播直接对各个节点进行测试,在链路和开关测试上可有100%覆盖率,而控制和存储测试的100%的覆盖率也使得路由测试更为全面。

5 结束语

为了研究片上网络的错误分布,提高片上网络的可测试性以及测试并行度,本文提出一种新型的三层片上网络架构,以较低的硬件开销完成可靠的硬件测试分析,同时大大提升测试的并行性。下一步的研究工作将对该平台在各个工艺下的实现进行分析,总结出客观的片上网络错误模型,在此基础上提出合理的容错路由器结构。

[1] 何 军,王 飙.多核处理器的结构设计研究[J].计算机工程,2007,33(16):208-210.

[2] 石泽文.多核处理器的容错路由与粒度建模研究[D].上海:复旦大学,2011.

[3] Aisopos K,Chen C H O,Peh L S.Enabling System-level Modeling of Variation-induced Faults in Networks-on-Chips[C]//Proceedings of the 48th Design Automation Conference.New York,USA:ACM Press,2011:930-935.

[4] Feng Chaochao,Lu Zhonghai,Jantsch A,et al. Addressing Transient and Permanent Faults in NoC with Efficient Fault-tolerant Deflection Router[J].IEEE Transactions on Very Large Scale Integration Systems, 2013,21(6):1053-1066.

[5] Prodromou A,Nicopoulos C,Sazeides Y,et al.NoC Alert:An On-line and Real-time FaultDetection Mechanism for Network-on-Chip Architectures[C]// Proceedings of the 45th Annual IEEE/ACM International Symposium on Microarchitecture.[S.l.]:IEEE Press,2012:60-71.

[6] Chen K C,Lin S Y,Shen W C,et al.A Scalable Built-in Self-recovery(BISR) VLSIArchitectureandDesign Methodology for 2D-mesh Based on-chip Net-works[C]// Proceedings of Conference on Design Automation for Embed System.[S.l.]:Springer,2011:111-132.

[7] 赵建武,师奕兵,王志刚.复用NoC测试SoC内嵌IP芯核的测试规划研究[J].计算机工程与应用,2010, 46(15):60-63.

[8] Wentzlaff D,Griffin P,Hoffmann H,et al.On-chip Interconnection Architecture of the Tile Processor[J]. Microarchitecture,2007,27(5):15-31.

[9] 杨士元.数字系统的故障诊断与可靠性设计[M].北京:清华大学出版社,2000.

[10] 陈光禹.可测性设计技术[M].北京:电子工业出版社,1997.

[11] Corno F,Prinetto P,Reorda M S.Fault Tolerant and BIST Design of a FIFO Cell[C]//Proceedings of Design Automation Conference.[S.l.]:IEEE Press, 1996:233-238.

[12] 何世超.片上网络通讯结构可测性设计[D].西安:电子科技大学,2008.

编辑 顾逸斐

Reliable Test Structure for Network on Chip Based on Multilayer Network

YU Jianming,ZHOU Wei,YU Zhiyi

(State Key Laboratory of ASIC&System,Fudan University,Shanghai 201312,China)

This paper proposes a new test architecture with high reliability and high parallelism.It adds a broadcasting network and a gathering network controlled by the broadcasting layer on top of the network under test.With the redundancy of these two networks,the robustness of the test access interface can be improved.Meanwhile,more test parallelism is brought and huge decrease is achieved in test time.Complete inner router test methods are also developed. Combined with the multilayer test access method,a complete and reliable test platform is got for Network on Chip (NoC).The result shows the multilayer network takes 56% less area and uses 85.8% less test time than Build-in Selfrepair BISR in 100-core system.And the fault coverage of the design achieves 100%.

multi-core processor;Network on Chip(NoC);multi-layer network;link fault;control fault

1000-3428(2015)01-0275-04

A

TP393

10.3969/j.issn.1000-3428.2015.01.052

国家自然科学基金资助项目(61103008);上海市科委集成电路专项基金资助项目(12511503700);国家科技重大专项基金资助项目(2011ZX03003-003-03)。

俞剑明(1988-),男,硕士研究生,主研方向:容错片上网络设计,多核处理器;周 炜,硕士研究生;虞志益,副研究员。

2014-01-13

2014-03-17 E-mail:11212020063@fudan.edu.cn

中文引用格式:俞剑明,周 炜,虞志益.基于多层网络的片上网络可靠测试结构[J].计算机工程,2015,41(1):275-278.

英文引用格式:Yu Jianming,Zhou Wei,Yu Zhiyi.Reliable Test Structure for Network on Chip Based on Multilayer Network[J].Computer Engineering,2015,41(1):275-278.