基于IP协议的FPGA万兆可靠互联通信设计与实现

宋宇飞,张俊杰,王凯,李家齐,薛子威,郑

(上海大学特种光纤与光接入网省部共建重点实验室,上海 200444)

基于IP协议的FPGA万兆可靠互联通信设计与实现

宋宇飞,张俊杰,王凯,李家齐,薛子威,郑

(上海大学特种光纤与光接入网省部共建重点实验室,上海 200444)

近年来,云计算和大数据处理迅猛发展,现场可编程门阵列(field programmable gate array,FPGA)由于拥有独特的并行处理能力,已在大数据处理中得到广泛应用.而通信网络的好坏会直接影响大数据处理的性能,基于此提出一种基于IP协议的FPGA万兆可靠保序互联通信系统,基于三指针环形缓冲池以及并行序号管理实现线速万兆数据通信,利用硬件超时重传机制实现可靠数据通信.该系统与用户接口采用先进先出(first in first out,FIFO)队列方式,接口简单;采用IP协议进行通信,使得通信协议开销较小,具有良好的系统扩展性;实际传输速率可达9.33 Gbit/s.

大数据;现场可编程门阵列;互联;通信

为了满足云计算[1]以及大数据处理[2]的发展需求,高性能计算(high performance computing,HPC)[3]变得越来越重要,现场可编程门阵列(field programmable gate array,FPGA)由于其灵活性、可编程性、拥有丰富的高速通信接口以及独特的并行处理能力[4],在高性能计算中得到了越来越广泛的应用.FPGA在HPC中一方面被用于数据处理、硬件加速[5],比如微软公司已经开始使用FPGA来代替CPU作为数据中心的处理单元;另一方面作为节点之间的通信通道,例如天河一号超级计算机中使用了自定义的互联协议[6].而随着节点数目的增加,节点之间的通信性能将成为系统性能提升的瓶颈之一.

在FPGA互联通信方面,Senouci等[7]提出了一种混合多处理器片上系统(multiprocessor system-on-chip,MPSoC),该系统采用嵌入式软件结构管理FPGA间的通信.Romoth等[8]介绍了一种能够实现信道自适应的FPGA互联通信结构.这些系统都是由处理器实现的,但由于嵌入式处理器性能不高,所以只能实现千兆以下互联通信数据传输.

另一种高速通信方法为片上网络(network-on-chip,NoC)[9-10],Liu等[11]提出了一种灵活的可扩展的多FPGA仿真框架,可以用来验证和测试一个完整的片上系统,该框架中的多个仿真模块可以通过FPGA的千兆位级收发器(multi-gigabit transceiver,MGT)串行链路互连;Mühlbach等[12]针对复杂的网络应用提出了一种基于环的可扩展多FPGA系统平台,而且用户数据报协议/传输控制协议(user datagram protocol/transmission control protocol, UDP/TCP)[13]核也已在FPGA中实现.然而,NoC系统只能实现单电路板上的多块FPGA进行高速互联通信,大规模FPGA互联通信的实现依然非常困难.

片上系统FPGA互联通信传输速率受限于片上处理器的工作频率(一般小于200 MHz),同时由于结构限制,不能实现大规模FPGA之间的高速数据通信.为了实现大规模FPGA之间的万兆可靠数据通信,本研究提出了一种基于IP协议的万兆可靠保序互联通信系统.本通信系统完全由硬件逻辑实现,因此能够实现10 Gbit/s线速的数据收发.同时,通信协议采用IP协议[14]来实现,包头开销小,带宽利用率高,并且系统可直接通过商用万兆交换机进行互联通信,具有较好的系统扩展性.

1 系统结构及接口定义

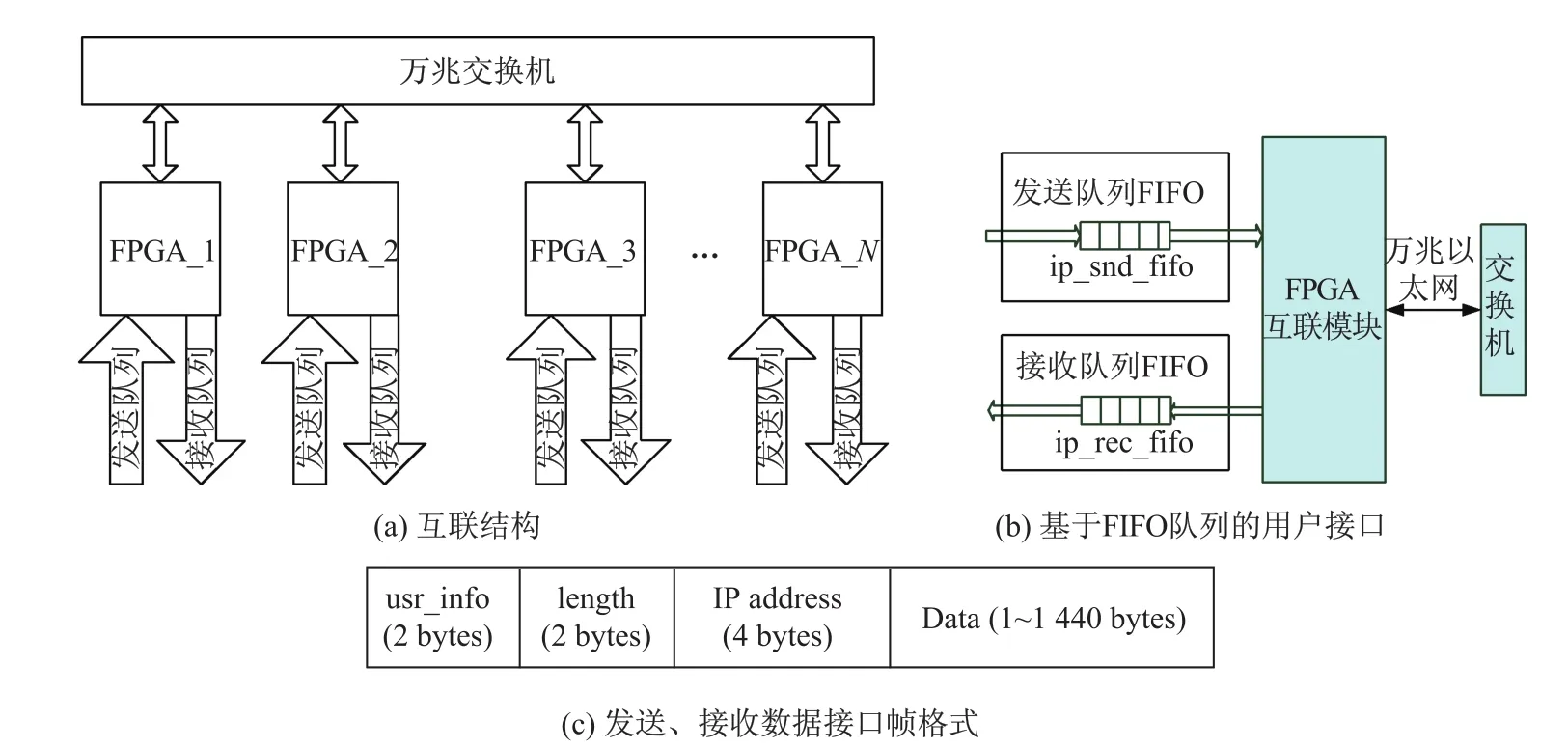

基于IP互联的传输结构如图1(a)所示,多片FPGA之间采用IP协议通过万兆交换机进行通信,通信速率为10 Gbit/s.基于先进先出(first in first out,FIFO)队列的用户接口如图1(b)所示,FPGA互联模块与用户的接口采用队列进行信息传输.用户把待传输的数据加入发送队列中,由FPGA互联模块完成数据的IP协议封帧、线速传输以及超时重传等可靠通信机制,同时完成万兆以太网接收数据的线速保序接收,并把接收到的数据剥离IP帧头,形成接收队列供用户使用.

为了便于用户使用以及简化接口设计,基于IP协议的FPGA通信对用户提供标准FIFO接口.如图1(b)所示,所有FIFO都是双时钟域FIFO,紧邻FPGA互联模块FIFO处的时钟频率为156.25 MHz,紧邻用户端的时钟频率可以由用户根据应用层需要进行动态配置.发送和接收队列FIFO宽度均为65 bit(其中最高位用来指示本次发送或者接收数据的起始位置),能提供10 Gbit/s的数据吞吐率.

发送队列FIFO:发送队列帧含义如图1(c)所示,其中usr info为用户提供的参考信息将通过万兆以太网透传到接收端,用户可以利用该信息对传输的数据进行分类和标识,length表示本次数据传输的长度(字节长度),其范围为1∼1 440字节,所定义的数据传输长度使得在一帧以太数据内能完成发送数据帧的传输,不需要对发送数据帧进行拆分和重组,简化了系统设计复杂度,IP address表示本次数据传输的目的IP地址,Data表示本次数据传输要传送的以太数据.从以上描述可以看出,发送数据接口定义比较简洁,便于用户调用和使用.

图1 基于IP互联的结构及接口Fig.1 Structure and interface based on IP interconnection

接收队列FIFO:接收队列帧含义与发送队列相似(见图1(c)),其中usrinfo为发送端发出的用户信息,length表示本次数据传输的长度(字节长度),IP address表示本次数据传输的源IP地址,Data表示本次数据传输接收到的以太数据.

从发送队列和接收队列的定义可以看出,本研究设计与实现的基于IP协议的万兆互联通道提供了一个开销较小的数据传输通道,其简洁的用户接口简化了系统设计和用户使用的复杂度.

2 高速可靠传输机制

2.1 基于三指针环形缓冲池的线速通信机制

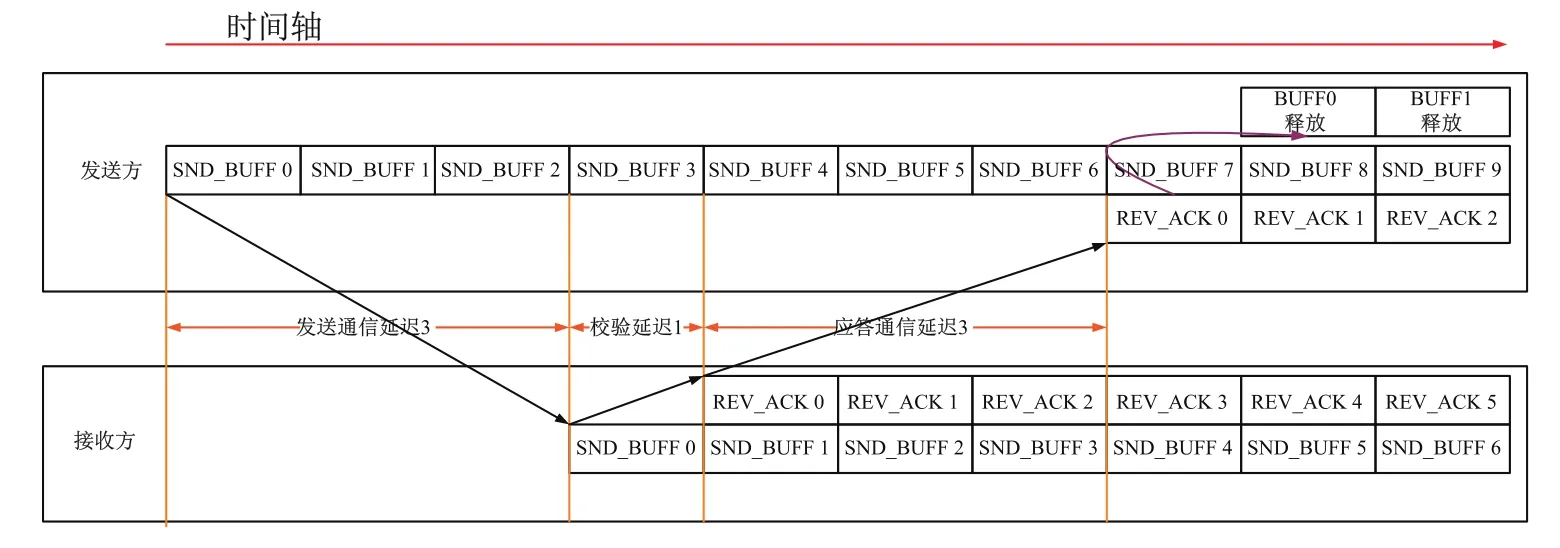

由于发送方发送的数据需要经过万兆交换机以及万兆光纤物理通道,因此接收端在一段时间之后才能收到发送的数据(见图2).从图中可以看出,接收端在3个时间片后才开始接收数据,并对接收到的数据进行校验.如果接收到的数据没有错误,则向发送端发送应答ACK.同理,由于发送端与接收端之间有通信延迟,则该应答信号在第8个时钟片才能达到发送端.

因此若要实现完全的流水线发送,则需要在发送端将已经发送出去的数据缓存起来,等收到接收方返回的应答ACK以后,再释放相应的缓冲区.缓冲区的大小需要与收发双方的通信延迟相匹配.

图2 互联通信的线速传输机制Fig.2 Line-speed transmission mechanism of interconnect communication

2.1.1 三指针环形缓冲池设计

为了实现所需的数据线速发送,本研究提出了一种基于三指针的环形缓冲池来缓存已经发送的数据(见图3),图中箭头方向表示指针的增量方向.整个缓冲池采用块方式进行存储,每一个块存储一个完整的已发数据帧.考虑到发送数据帧的长度小于2 KB,因此每一个块的大小为2 KB.缓冲池共有M=256个存储块,能够匹配收发双方大约331µs的通信延迟.存储池提供的信息如下.

(1)头指针:表示未收到应答帧的第一个已发送数据缓冲区.当头指针对应的数据成功发送到接收方以后,接收方产生应答帧发给发送端;发送方收到该应答帧以后,则表示头指针指向的缓冲区数据已经成功发送到接收端;然后头指针自增1,指向下一个待确认的已发数据缓冲区.

(2)尾指针:用户待发信息存储区起始指针.当用户发送队列有数据需要发送,则把待发送数据存储到尾指针指向的缓冲区,待发数据存储完毕,尾指针自增1.

(3)当前发送指针:若缓冲池有数据要发送,则为该指针指向的缓冲区数据增加IP协议,并发送到万兆以太网络上.

(4)空标志(Send_Buf_ Empty):环形缓冲池没有待发送数据(即当前指针与尾指针重合).

(5)满标志(Send_Buf_ Full):环形缓冲池已经写满(即尾指针与头指针重合).

图3 基于三指针的环形缓冲池Fig.3 Ring buffer pool based on three-pointer

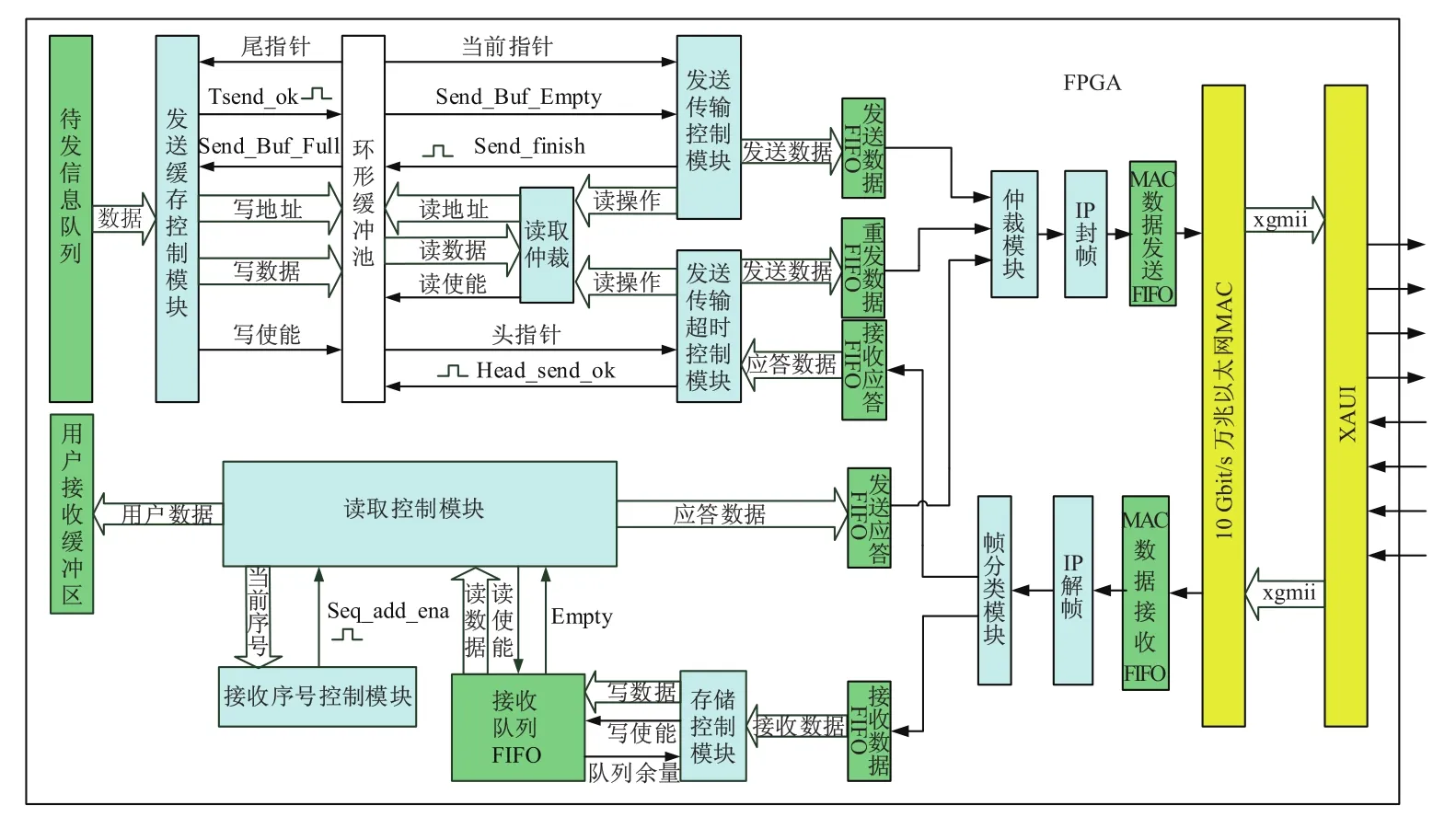

2.1.2 线速发送结构及流程

发送端线速传输的FPGA实现逻辑如图4的上半部所示,其线速通信方案依赖三指针环形缓冲池的存储控制,主要包括线速存储、线速读取以及线速封帧三大部分.存储、读取和封帧的操作依赖各自对应收发数据FIFO状态以及环形缓冲池的状态,三者之间相互独立,共同实现待发数据的线速通信.

(1)线速存储:当发送缓存控制模块检测到待发信息队列有数据需要发送,且环形缓冲池能够容纳一帧以太数据(即Send_Buf_ Full无效)时,则从待发信息队列获取要发送的一帧数据,并把该帧数据线速存储到基于双端口存储器的环形缓冲池中;待该帧数据传输完毕,则向环形缓冲池发送传输完成信号Tsend ok;环形缓冲池一旦检测到Tsend-ok信号有效,则沿指针绕行方向把尾指针指向下一个缓冲区,从而实现待发信息的线速存储.

(2)线速读取:发送传输控制模块一旦检测到环形缓冲池中有超过一帧的数据要发送(即SendBufEmpty信号无效),则从当前发送指针指向的缓冲区线速读取完整的一帧,并为该帧增加当前发送序号,然后将该帧写入发送数据FIFO;完整写入后,向环形缓冲池发送传输完成信号Send_finish;环形缓冲池一旦检测到该信号有效,则沿指针绕行方向把当前发送指针指向下一个缓冲区,从而实现了数据的线速读取.

图4 线速收发逻辑结构框图Fig.4 Line-speed transmitting logic structure diagram

(3)线速封帧:当仲裁模块检测到发送数据FIFO、重发数据FIFO或发送应答FIFO有数据需要发送时,则通过仲裁从相应FIFO中读取一帧数据,并将该帧数据传送给IP封帧模块;IP封帧模块收到该帧数据后,为其添加相应的IP头信息,并将该帧封装成完整的以太帧;然后通过介质访问控制(media access control,MAC)和10 Gbit/s以太网连接单元(ten-gigabit attachment unit interface,ⅩAUI)将该帧传送到物理信道上.

线速存储、线速读取和线速封帧采用流水线结构,流水线级与级之间互相没有干扰,用户数据经过这三级线速流水线处理,被封装成完整的以太帧,并可实现线速发送到物理信道上. 2.1.3可靠线速通信的万兆以太网传输帧格式

为了支持万兆线速可靠数据通信,基于IP协议通信的帧格式如图5所示.图中,类型:表示发送帧类型,包括数据内容帧(0x31)和数据应答帧(0x32);并发序号:对应当前发送指针指向的缓冲区编号,用于保序传输(详见2.2.2节);长度:表示有效的数据长度,以字节为单位;用户信息:由用户提供的信息,透传到接收端.

图5 自定义协议帧格式Fig.5 Custom protocol frame format

该可靠通信协议基于IP层进行传输,包括通信头和通信内容两部分.从图中可以看出, IP协议通信头仅占用8字节,与传统的TCP首部20个字节相比,协议通信头开销减少了60%.帧类型有两类:①数据内容帧(0x31),与其对应的传输数据为图1(c)用户定义的待传数据;②数据应答帧(0x32),是指接收方收到内容帧后向发送方发送的应答帧,对应的传输数据暂时没有定义.为了满足以太帧的最小64 bytes的需求,同时减少应答帧占用网络的通信带宽,将传输数据长度设置为24 bytes.

2.2 可靠通信机制

2.2.1 数据通信丢包重传机制

为了解决互联通信由于通道竞争以及带宽受限带来的丢包现象,本研究提出的逻辑实现方案增加了硬件超时重传功能,如图4中的发送传输超时控制模块.该模块在一定时间间隔内(与收发往返延迟相关,如1 ms)检测头指针是否发生变化,如果没有变化则意味着没有收到头指针对应缓冲区的应答帧,或者该缓冲区数据没有正确发送到接收方,则发送方重新发送头指针指向的缓冲区数据;该模块如果接收到了头指针对应的应答信号,则释放当前头指针指向的缓冲区,并把头指针移动到下一个缓冲区,同时把超时计数模块清零.如果重发多次(可设)仍然没有接收到应答信号,则放弃本次操作,并向上层应用汇报数据发送状况.

2.2.2 保序传输机制

系统的保序通信通过收发序号检测的方法来实现.当初始上电时,发送方和接收方的当前序号均默认为0,每成功发送或接收一次,当前序号加1,然后进行下一次发送或接收,直到当前序号达到M−1(此处M=256,与缓冲池的块数目相匹配),则下一次当前序号再次复原为0.发送传输控制模块为当前发送指针所指缓冲区的数据帧添加当前序号,并将该序号封装后,发给接收方;发送完成后,当前发送指针指向下一缓冲区,进行下一次发送.

接收方存储控制模块收到来自以太网的信息后,首先将信息存储到接收队列FIFO中去,如果存储过程中接收队列的余量不能容纳一帧以太数据,则丢弃本次以太数据,等待发送方重发本次数据.读取控制模块若检测到接收队列FIFO非空(即Empty信号无效),则从接收队列FIFO中获取本次接收数据的接收序号.如果本次接收数据的当前序号与本地当前序号一致,则认为本次数据为要传输的数据,然后把该数据传输到用户接收缓冲区,并产生一个新的保序接收有效信号Seq_add_ ena,同时向发送方发送包含当前序号的应答数据.当接收序号控制模块检测到Seq_add_ ena信号有效时,则把本地当前序号自增1.如果接收序号与本地当前序号不一致,则认为此数据帧为非正常保序传输帧,丢弃该帧,等待发送方发送保序帧.

3 系统测试

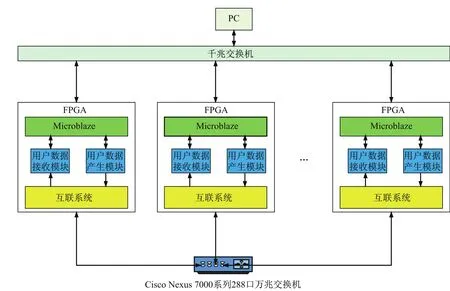

本研究提出的基于IP协议的FPGA万兆可靠互联通信系统已在Xilinx Virtex 6 lx550t FPGA上实现应用,对应的FPGA开发平台详细结构参见文献[15].为了测试系统工作稳定性,搭建了相应的测试平台,结构如图6所示,100块FPGA通过Cisco Nexus 7000系列288口万兆交换机相连.每块FPGA内部由用户数据产生模块产生测试数据,由用户数据接收模块接收来自互联系统的数据.用户数据产生模块的启动、停止以及用户数据发送的目的IP也是由FPGA内部软核Microblaze来控制与实现的.除此之外,内部Microblaze能够收集上述两个模块发送和接收的数据总量,以评测系统通信的可靠性.为了支持大规模系统测试, Microblaze运行LWIP协议,使得控制中心PC可通过千兆交换机控制每一台FPGA.数据帧负载为1 024字节,经过长时间(1天)的测试,每一对收发FPGA通道的发送与接收数据量保持一致,验证了系统的通信稳定性和可靠性.

图6 系统测试结构Fig.6 System testing structure

图7为通过Xilinx Chipscope Pro Analyser抓包软件抓取到的测试过程中某一块FPGA上的内部逻辑信号,图中xgmii_ txd为发送的数据,xgmii_rxd为接收的数据.可以看出,发送端在并发模式下一次性连续发出多帧数据,接收端隔一段时间便会收到ACK帧.发送端数据帧占用139个时钟,帧间隙为10个时钟.由于万兆接口时钟为156.25 MHz,数据位宽为64,故数据传输速率为139/149×156.25 MHz×64 bit=9.33 Gbit/s,可见带宽利用率达到了93.3%,已非常接近理论传输速率10 Gbit/s.

图7 并发模式数据传输Fig.7 Data transmission in concurrent mode

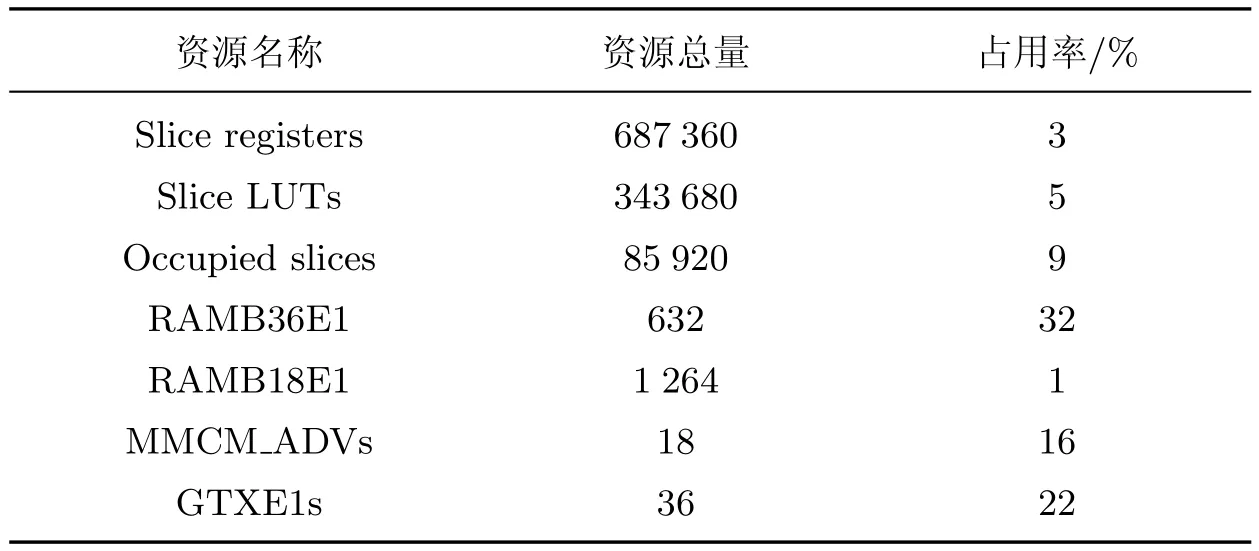

本系统在lx550t FPGA上的资源占用情况如表1所示.从表中可以看出,系统仅占用了少量的FPGA Slice资源和RAM资源.由于每块FPGA提供2个万兆接口,因此共使用了8个GTX高速串行收发器.系统共占用3个时钟资源,其中2个用于XAUI IP核产生156.25 MHz时钟,1个用于产生Microblaze使用的100 MHz时钟,即占用3个MMCM_ADV资源.

表1 Virtex 6 lx550t资源占用表Table 1 Device utilization summary for Virtex 6 lx550t

4 结束语

本研究提出了一种可在FPGA上实现的大规模FPGA高速万兆可靠保序互联通信系统,采用基于IP协议的自定义协议,减小了包头开销,提高了带宽利用率.系统设计基于三指针环形缓冲池,通过分析收发两端通信延时,提出线速数据存储、线速数据读取及线速封帧方法;采用流水线处理结构实现了线速万兆数据传输;通过保序传输机制以及超时重传机制,确保了传输可靠性.系统实测数据传输速率可达到9.33 Gbit/s,并成功实现了100多个FPGA处理单元之间的万兆可靠互联通信.

[1]秦秀磊,张文博,魏峻,等.云计算环境下分布式缓存技术的现状与挑战[J].软件学报,2013,24(1): 50-66.

[2]陈如明.大数据时代的挑战、价值与应对策略[J].中国国际信息通信展专刊,2012(17):14-15.

[3]李波,曹福毅,王祥凤.高性能计算技术发展概述[J].沈阳工程学院学报:自然科学版,2012,8(3): 252-254.

[4]杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J].电子与信息学报,2010(3):714-727.

[5]张兴军,丁彦飞,黄一元,等.基于FPGA的动态部分可重构高性能计算实现[J].华中科技大学学报:自然科学版,2010,38:82-86.

[6]朱小谦,孟祥飞,菅晓东,等.“天河一号”大规模并行应用程序测试[J].计算机科学,2012(3): 265-267.

[7]Senouci B,Kouadri M A M,Rousseau F,et al.Multi-CPU/FPGA platform based heterogeneous multiprocessor prototyping:new challenges for embedded software designers[C]//The 19th IEEE/IFIP International Symposium on Rapid System Prototyping.2008:41-47.

[8]Romoth J,Jungewelter D,Hagemeyer J,et al.Optimizing inter-FPGA communication by automatic channel adaptation[C]//2012 International Conference on Reconfigurable Computing and FPGAs(ReConFig).2012:1-7.

[9]Mak T S T,Sedcole P,Cheung P Y K,et al.On-FPGA communication architectures and design factors[C]//International Conference on Field Programmable Logic and Applications. 2006:1-8.

[10]韩高飞,杜慧敏,蒋林,等.基于FPGA的NoC验证平台的构建[J].电子设计工程,2010(3):90-93.

[11]Liu Y,Liu P,Jiang Y,et al.Building a multi-FPGA-based emulation framework to support networks-on-chip design and verification[J].International Journal of Electronics,2010,97:1241-1262.

[13]龙玉军,龚彬,马卫东,等.基于TCP、UDP的多路多数据流融合网络系统设计[J].电子设计工程, 2011,19(21):69-72.

[14]张齐,劳炽元.轻量级协议栈LWIP的分析与改进[J].计算机工程与设计,2010,31(10):2169-2171.

[15]Zheng Y,Zhang J J,Yan K,et al.Design and implementation of multi-FPGA high-speed access to RAID[C]//2013 IET/IEEE Second International Conference on Smart and Sustainable City.2013:203-207.

Design and implementation of FPGA 10 Gbit/s reliable interconnect communication based on IP protocol

SONG Yu-fei,ZHANG Jun-jie,WANG Kai,LI Jia-qi,

XUE Zi-wei,ZHENG Yue

(Key Laboratory of Specialty Fiber Optics and Optical Access Networks, Shanghai University,Shanghai 200444,China)

In recent years,cloud computing and big data processing have been rapidly developed.Since field programmable gate array(FPGA)has the unique parallel processing ability,it is widely used in big data processing.As the performance of communication network directly affects the performance of big data processing,this paper presents a high speed and reliable communication system based on IP protocol for FPGA communications. The system uses a three-pointer ring buffer pool and a method of parallel number management to achieve data transmission at a line-speed of 10 Gbit/s.By implementing hardware timeout retransmission mechanism,the system can guarantee reliable communications.A self-defined reliable IP protocol is used in the system,which has a small overhead and a good system expansion.Tests on the FPGA hardware platform show that the real data transfer speed can reach 9.33 Gbit/s.

big data;field programmable gate array(FPGA);interconnection;communication

TN 914.34

A

1007-2861(2015)05-0570-09

10.3969/j.issn.1007-2861.2014.05.015

2014-08-05

上海市科委科技攻关项目(13DZ1108800);上海市科委基金资助项目(11510500500,13JC1402600);国家自然科学基金资助项目(61132004,61275073)

张俊杰(1978—),男,高级工程师,博士,研究方向为光接入网等.E-mail:zjj@staff.shu.edu.cn