便携式超声探伤系统设计❋

卢伟雄,曾松德,李怀胜,钟清华

(华南师范大学物理与电信工程学院,广州510006)

便携式超声探伤系统设计❋

卢伟雄,曾松德,李怀胜,钟清华

(华南师范大学物理与电信工程学院,广州510006)

为克服传统超声探伤系统设计复杂以及电路调试困难等缺点,介绍了一种以Altera公司的Cyclone IIFPGA为处理核心的设计方案。利用NIOS II软处理内核构建SOPC嵌入式系统,使用IP核技术,结合超声传感器实现探伤系统的软硬件协同设计,灵活高效,有利于缩短设计迭代周期。实验结果表明,该系统能够实现数据实时采集和复杂算法处理,具有体积小、成本低和可靠性高等特点,能够有效分析判断缺陷的位置和特征。

超声探伤;FPGA处理器;SOPC技术;IP核;实时采集;缺陷分析

1 引 言

超声波检测作为一种重要的无损检测方法,通过将超声波耦合到被检测对象,并获取其中的透射波、反射波,分析被测对象的内部结构,适用于产线质量监控、现用设备和关键零部件的缺陷分析[1]。目前,在便携式超声波探伤仪设计中,大多数以FPGA+DSP或者FPGA+ARM为核心,但DSP的串行指令执行方式,使探伤仪的工作速度和效率大打折扣;使用ARM嵌入式系统可开发友好的图形用户界面,但系统电路复杂,设计成本较高[2]。随着可编程片上系统(System on a Programmable Chip, SOPC)日益成熟,在FPGA中构建嵌入式处理器内核,软硬件协同设计,具有功耗低、体积小、成本低、可靠性高等优点,系统控制灵活,调试方便。

Altera公司提供的NIOS II软处理内核,支持32位宽的指令和数据总线,通过存储器拓展接口,可访问片内和片外存储器,以支持程序运行,非常适合网络、数据处理等应用背景的嵌入式系统。利用NIOS II在FPGA上构建SOPC系统及相关接口,设计可靠的超声波检测电路,编写系统功能IP核(Intellectual Property Code)及嵌入式处理程序,采用单核处理,灵活高效,适用于设计一种便携式、低成本的超声波探伤仪系统。

2 超声波探伤仪总体架构

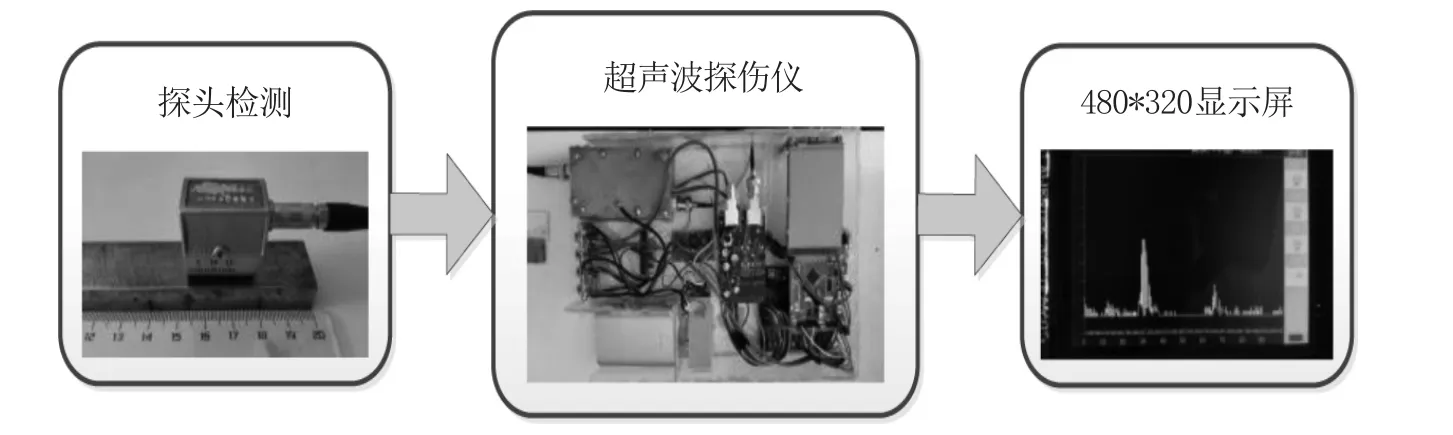

超声波探伤仪的系统框图如图1所示。系统选用单晶体超声波斜探头BSN1540,中心频率为5MHz,利用Altera公司生产的Cyclone II系列FPGA(EP2C8Q208CN)作为处理核心,通过配置NIOS II软核,以及设计各功能IP核,完成发射电路驱动、接收电路控制、数据采集、数据处理分析、系统功能选择、结果显示及存储等功能。系统充分利用FPGA的并行处理特性,结合其软硬件协同设计的灵活性,简化系统电路,减少外界干扰,提高系统的稳定性和可靠性。

3 超声波检测电路设计

3.1 超声波发射驱动电路

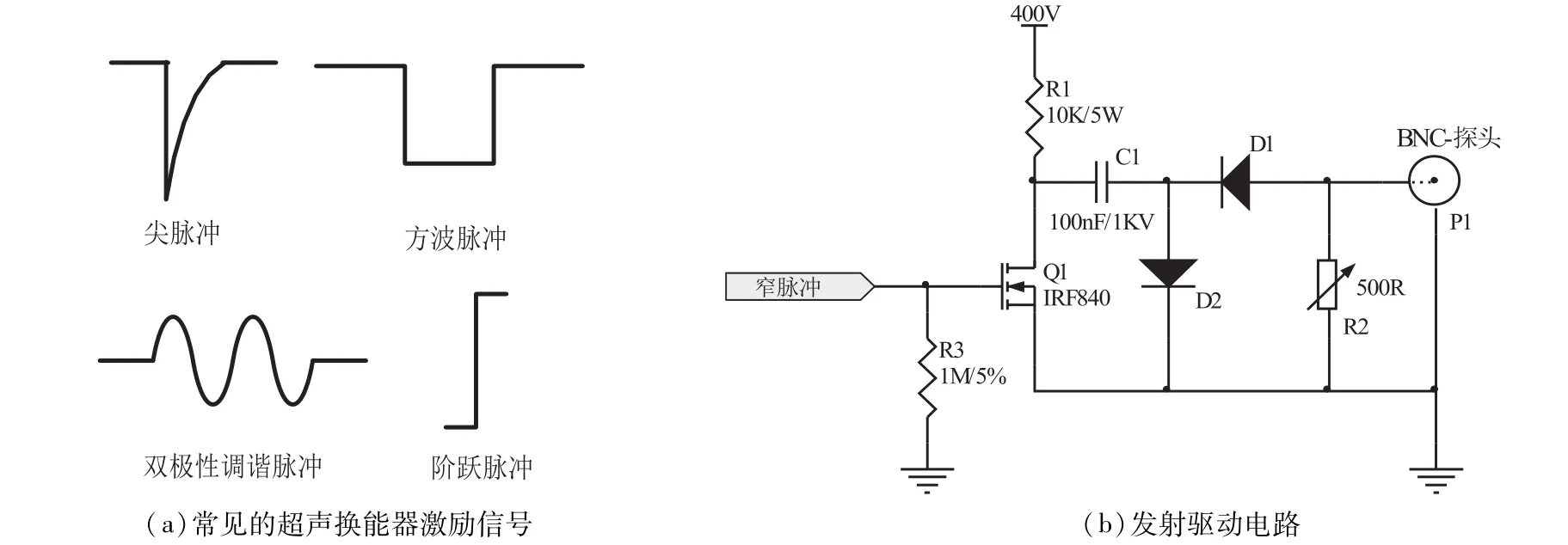

系统探头是一种单晶体超声换能器,其前辐射面声压与激励电压的导数dU/dt成正比,因此尽量减少激励脉冲的上升时间至关重要,常见的超声换能器激励信号[3]如图2(a)所示。系统选用尖脉冲信号,其脉冲宽度窄,幅度高,能高效激励换能器产生超声波信号。针对激励信号特点,系统设计一种非协调式发射驱动电路,如图2(b)所示,适用于产生尖脉冲信号,没有使用调谐元件,产生的超声波频率主要由换能器的中心频率决定,以便适应不同频带范围的探头[4]。

图1 超声波探伤仪系统框图

图2 发射激励信号及驱动电路

发射电路的高压激励源选用小型集成化高压电源模块,用于产生400V高压。MOS管Q1(IRF840)作为高速开关,受控于FPGA产生的低压窄脉冲触发信号。触发脉冲为低电平时,Q1截止,高压源通过R1、D2对电容C1充电,使其两端电压差达到+400V。触发脉冲翻转为高电平后,Q1导通,C1经过Q1、R2和D1放电,电容两端电压不能发生突变,D1输出端电位转变为-400V,激励探头产生超声波信号。另外,可变电阻R2决定了电路的阻尼情况,影响发射信号的强度。电阻大,阻尼小,发射强度大,系统分辨率低,适用于分辨率要求不高的大厚度检测;相反,则发射强度小,系统分辨率高,适用于分辨率要求高的近表面检测。

3.2 超声波接收电路

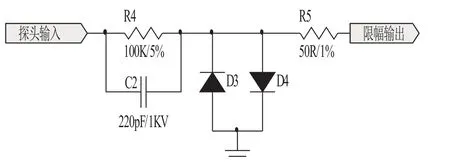

系统选用单晶体探头,为避免高压尖脉冲信号击穿损坏后级接收电路,设计了一种带RC并联网络的限幅保护电路,如图3所示。在传统并联限幅电路中引入RC并联网络,既能抑制串扰的激励信号,又能使接收电路与探头之间实现最佳阻抗匹配,其转折频率为f0=1/(2πR4C2),电容容抗为Xc=1/(2πfC2)。设置系统的转折频率为5MHz,电容容抗为50Ω,当输入信号频率远小于f0时,电路总阻抗等效为R4,此时能够有效吸收发射激励信号;当频率接近f0时,总阻抗约等于XC,能够最佳匹配探头阻抗,拾取回波信号。为了达到更好的限幅保护效果,通过RC网络后,由并联限幅电路将输入点电位限制在±0.7V,使得高压信号被钳位,微弱回波信号直接输入后级处理。

超声波在传播中存在衰减,且被测对象厚度不同,回波信号有较大的动态范围,这要求接收放大电路能实现自适应增益控制,提高系统灵敏度[5]。系统回波信号的频率为探头固有中心频率,由于存在噪声干扰,因此数据采集前需经过带通滤波器拾取有效信号,具体的电路设计方案如图4所示。

系统采用级联自适应增益放大电路,前置同相增益放大器选用MAXIM公司的高速运放MAX4104ESA,固定增益41倍;配合TI公司的压控增益放大器VCA810,利用D/A电路输出增益控制电压,增益范围±40dB,实现自适应增益控制。系统应用MAX4104ESA设计二阶有源带通滤波器,其中心频率为5MHz,带宽为1.25MHz,能有效滤除回波噪声,有效拾取回波信号。利用高速A/D采集数据,以便FPGA对回波信号进行分析处理。

图3 限幅保护电路

图4 后级接收处理电路

4 系统软件设计与实现

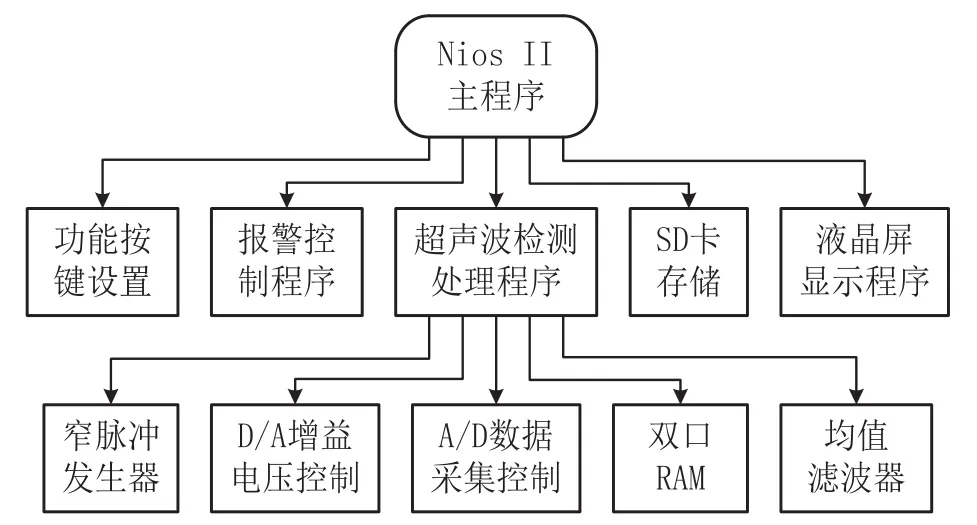

根据超声波探伤仪的系统特点,在FPGA上设计相应的功能IP核及相关接口,其中接口参数可调,系统更新迭代灵活。在NIOS II处理器中统一调度,实现超声波发射控制、信号增益控制、数据采集分析、数据存储及回波显示等功能,具体的系统软件设计如图5所示,系统设计使用VHDL语言,应用软件设计使用C语言。

4.1 窄脉冲发生器

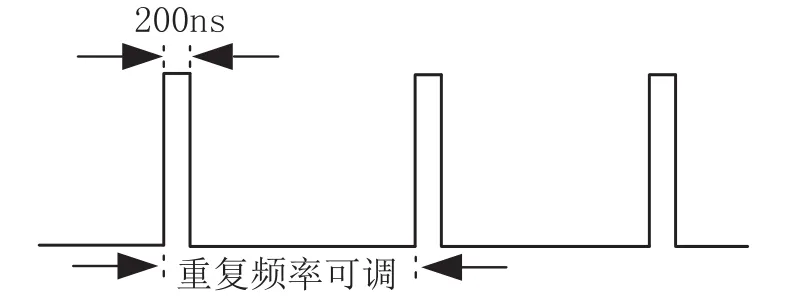

超声波探伤仪的发射触发脉冲重复频率一般在50Hz~2KHz之间,可以高达10KHz以上,提高重复频率有利于提升探伤速度,但提高重复频率却受限于检测距离。如果重复频率过高,当回波信号声程的时间大于触发脉冲的周期时,容易出现发射波与回波混叠,导致检测失败。为了适应不同探伤材料、不同探伤厚度,系统基于FPGA设计了一个脉宽固定、重复频率可控的窄脉冲发生器[6]。为匹配探头中心频率,窄脉冲的脉宽始终保持为200ns,初始化重复频率为500Hz,用户可通过功能键盘设置重复频率,具体的触发脉冲如图6所示。

图5 超声波探伤系统软件设计

图6 可调重复频率窄脉宽信号

4.2 数据采集处理

系统选用AD公司的50MHz高速A/D转换器AD9283,采样率10倍于超声波信号的中心频率,能够很好的保留超声波信号的信息,可无需低通滤波恢复,直接打印原始波形,进一步简化系统电路[7]。系统根据声速和声程计算采样点数,并将其写入寄存器中,由NIOS II综合调度A/D采集信号数据。每一轮采样开始时,A/D控制模块监听片上系统的触发信号,控制AD9283进行采样,50MHz时钟提供到AD9283的ENCODE端,在时钟的下降沿,将A/D转换结果写入双口RAM,实现信号数据高速采集存储。

4.3 双口RAM

双口RAM具有两套独立的数据、地址和控制总线,可以对两个端口进行同时读写,互不干扰。系统将采样数据从一个端口写入,由片上处理器从另一个端口读出,实现数据高速存取,并且具有随即存取的优点。由于大容量的高速双口RAM价格相对较贵,因此系统利用Altera公司提供的双口RAM IP核,在FPGA内部构建一个16K*8bit的双口静态RAM,访问速度快,满足系统对高速存储的要求,而且降低系统成本[8]。

4.4 数据自适应平滑滤波

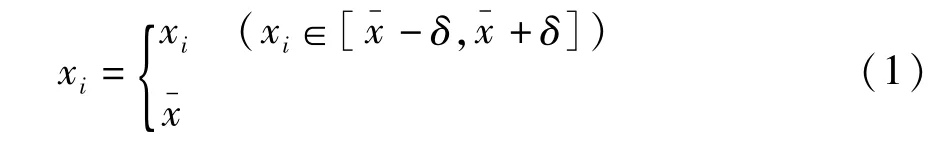

由于外界环境影响或者被测试件表面粗糙不平,回波信号会受到噪声的干扰,数据存在奇异值。系统通过改进均值滤波器,实现数据自适应平滑滤波处理。在实际设计时,系统选用1*4的滤波窗口,计算窗口内数据的均值x-和方差δ,设定阈值为[x--δ,x-+δ],对于落在这个区间的数据,默认为正常数据,否则使用均值代替该值,从而有效剔除窗口内奇异值对回波数据的影响。改进后的均值滤波算法可表示为:

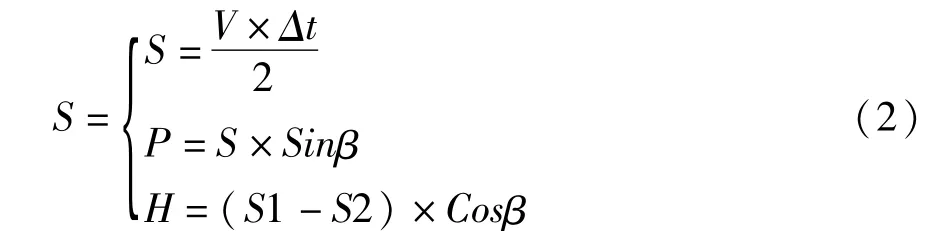

4.5 探伤回波分析计算

系统通过数据高速采集存储技术,保证回波信号的完整性,因此利用发射信号与接收信号的时间差可以准确地检测出缺陷位置。假设每次发射信号与接收信号的时间差为Δt,超声波在被测物体中的传播速度为V,探头入射点到裂纹的水平距离为P,回波声程为S。如图7所示,针对超声波斜探头,根据端点反射回波法,裂纹根部与顶端的端点回波声程分别为S1和S2,探头移动距离为L,入射角为β,垂直于表面的裂痕高度为H,试块厚度为T。由式(2)可以分别计算出系统回波声程S、裂纹的水平距离P和高度H。

图7 裂纹探测原理图

5 系统测试

为检测系统性能,进行如下实验测试:选用北极星辰公司提供的单晶体超声波斜探头BSN1540,中心频率为5MHz,入射角为69.14度,K值为2.624;试件选用45号钢,斜探头横波在其中的传播速度为3230m/s;试件尺寸为20mm×20mm×10mm,底面用线切割加工出垂直表面的裂纹,裂纹宽度为0.3mm,高度为3mm。

测试时,在探头和试块表面涂敷甘油作为耦合剂,提高其耦合效果。移动探头,当屏幕出现回波信号后,持续移动,直到回波信号消失,读取这一过程中回波信号最强点(即裂纹根部)的声程S1,刻度尺测量此时探头与裂纹的水平距离P1;读取回波信号消失前一时刻(裂纹顶端)的声程S2及探头与裂纹的水平距离P2;具体试验数据如表1所示。

图8 系统测试示意图

表1 系统测试结果

6 结束语

超声波探伤仪采用FPGA单核心处理器,使用较高性能的Nios II软核,构建完善的SOPC嵌入式系统,有利于实现系统小型化。系统使用IP核技术,极大地提高了设计灵活性,缩短了设计迭代周期,使得整个开发过程高效可控,方便对产品进行修改或添加新功能,延长了产品的生命周期。测试结果表明,系统能够实时准确的提取超声波回波信号,有效分析判断出缺陷的位置和特征。

[1] Martin,R.Nat.Nondestructive Testing Centre,Harwell,Didcot,UK.Portable digital NDT instrumentation[J].Recent Developments in Digital NDT Equipment Design,1988:1-2.

[2] 金伟,周西峰,郭前岗.基于FPGA的便携式超声波探伤仪设计[J].电子测量技术,2009(9):107-110.

Jin W,Zhou X F,Guo Q G.Design of portable ultrasonic flaw detector based on FPGA[J].Electronic Measurement Technology,2009(9):107-110.

[3] 游江通,刘松平,宋秀荣.一种新颖的宽带窄脉冲超声波发生电路[J].航空制造技术,2004(4):88-91.

You JT,Liu S P,Song X R.A novel circuit to generate the broadband narrow pulse ultrasonic[J].Aeronautical Manufacturing Technology,2004(4):88-91.

[4] 王晓蕊,张晓青,贾三山.超声波探伤发射电路及参数分析[J].仪表技术与传感器,2012(9):30-32.

Wang X R,Zhang X Q,Jia S S.Transmission circuit and parameter analysis for ultrasonic flaw detector[J].Instrument Technique and Sensor,2012(9):30-32.

[5] 宋光德,胡宏波,梁磊.一种基于FPGA的A超数字式探伤系统的研究[J].电子技术应用,2003,(10):29-30.

Song G D,Hu H B,Liang L.A system research of A-mode digital flaw detection[J].Electronic Technology Applications,2003(10):29-30.

[6] Dingguo Xiao,Bo Yang,Qinxue Pan,et al.Measurement of characteristic parameters of ultrasonic flaw detectors[J].Mechatronics and Automation(ICMA),2012:641-646.

[7] Tao Lin,Zhou Zhenguo.The implementation of 100MHz data acquisition based on FPGA[J].System-on-Chip for Real-Time Applications,2003:287-291.

[8] 张凯华,任勇峰,贾兴中.基于FPGA的高速数据存储系统优化设计[J].电子技术应用,2014(9):37-40.

Zhang K H,Ren Y F,Jia X Z.Optimization design ofhigh speed data storage system based on FPGA[J].Electronic Technology Applications,2014(9):37-40.

Design of Portable Ultrasonic Flaw Detection System

Lu Weixiong,Zeng Songde,Li Huaisheng,Zhong Qinghua

(School of Physics and Telecommunication Engineering,South China Normal University,Guangzhou 510006,China)

In order to overcome the disadvantages of traditional related design such as complicity of circuit and shortcomings of debugging,a new design method of ultrasonic flaw detector based on the Altera's Cyclone IIFPGA is proposed.IP code and the SOPC,composed of NIOS IIprocessor,conducive tomake the system efficient and shorten the design cycle,are used to achieve the collaborative design of hardware and software with ultrasonic sensor.The experiments show that the system can realize the real-time data acquisition and the complex algorithms,has the feature of small size,low cost and high reliability and so on and can effectively analyze the position and characteristics of flaw aswell.

Ultrasonic flaw detection;FPGA;SOPC;IP code;Real-time data acquisition;Flaw analysis

10.3969/j.issn.1002-2279.2015.05.024

TP277

A

1002-2279(2015)05-0092-05

广东省教育部产学研合作基金(2012B091100062);广东省自然科学基金(S2011040003189)

卢伟雄(1989-),男,广东省汕头市人,硕士研究生,主研方向:智能仪器与系统。

2015-03-04