ADSP-TS101高速全双工Link收发器FPGA设计

王 鹏,连帅彬,孙秋菊,黄文霞,钟莉娟

(1. 信阳师范学院 物理电子工程学院, 河南 信阳 464000; 2. 中国空空导弹研究院 航空制导武器航空科技重点实验室, 河南 洛阳 471009)

0 引言

在各种雷达信号处理系统中,DSP和FPGA的应用极为广泛.通常地,FPGA具有强大的并行处理能力,而浮点DSP则具有开发周期短和高的计算精度等优势,常用于对预处理数据的进一步算法处理.目前常用的浮点DSP有ADI公司的TigerSHARC101(以下简称TS101)、以及TS101的性能加强版本TS201[1],此外TI公司的C671x、C667x系列等也是常用的浮点DSP芯片[2-3].其中,TS101虽然已经推向市场多年,运算性能并不占优,但由于极为出色的功耗控制,使得其在许多以电池为供电来源的弹载雷达系统中成为最常见的DSP器件[4].而FPGA芯片则以Xilinx和Altera两大公司的中高端产品为主,如Virtex5/6、Stratix IV等[5].

近年来,由于弹载雷达信号处理复杂度日益提高,整个系统所处理的数据量飞速增加,传统的准连续波体制雷达只需包含有一维速度数据即可完成目标速度和角度测量[6],而PD体制则上升到距离—速度二维数据矩阵[7],近年来逐渐成为研究热点的STAP技术更是需要完成距离—速度—空间三维矩阵数据处理[8-10].如此海量的数据要求必须在DSP和FPGA之间实现高速、可靠的数据通信[11].针对该需求,传统的设计方案是利用FPGA内部丰富的块存储器,并开辟一段专用的SRAM存储区,DSP通过地址和数据外总线对其进行读写操作. 然而这种方案传输速率受DSP外总线的限制很大,多数DSP芯片的外总线时钟速率最高只能达到100 MHz左右,而且该方案还要求所有外总线设备必须共享总线,直接限制了传输效率,同时总线时钟频率也难以满足复杂信号处理中的高速数据交换[12].因此,本设计采用性能上更为优秀的TS10高速Link接口作为专用高速通信接口,并采用相应的TigerSHARC 101 Link通信协议完成DSP和FPGA的信息交互.与其他的协议相比,该协议最大的优势是可以在时钟的上升沿和下降沿同时传输数据,这使得其传输效率比传统的单时钟沿数据速率(Single Data Rate)方案得到改善,并且由于TS101共有4个独立的Link口,总吞吐量还可以进一步增加4倍.因此,综上所述,采用Link接口可以获得远比外总线传输方案更高的传输速率.本设计在FPGA芯片内完整实现了Link口协议收发的全部功能,仅占用少量LUT及寄存器资源,最高传输速率可达4.8 Gb/s.而且该设计通用性及可移植性良好,不仅可用于FPGA与DSP高速互联,也可用于实现FPGA片间的高速通讯,进而推广应用于更多场合.

1 TigerSHARC 101 Link协议

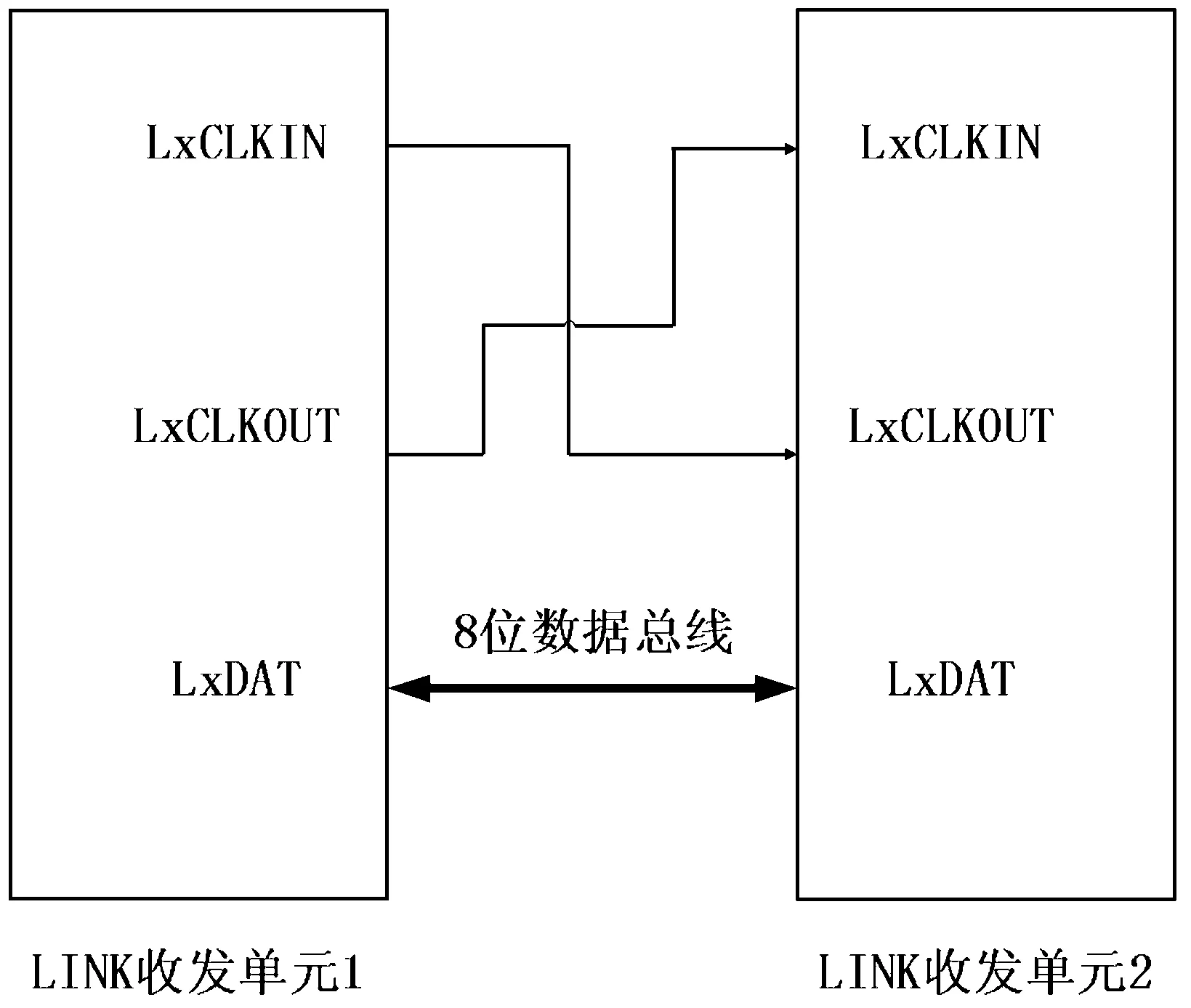

TigerSHARC Link通信协议 (以下简称Link协议)的最小系统传输接口如图 1所示:

图1 Link接口信号说明Fig.1 Link interface signal lists

可以看出,Link协议通过8位并行数据总线完成双向数据传输,同时与数据总线配合的还有相应的时钟信号线LxCLKIN、LxCLKOUT.

按照TS101器件手册,Link链路传送过程的最小粒度是每8个周期传送1个四字组,每个四字组包含16字节,时钟的上下沿各传送一个字节,且传送过程均由发送端发起.同时,当且仅当接收端将它的LxCLKOUT置为高,即接收端处于接收方式,且有空闲的缓冲时,发送端才可以启动一个传送过程[13].

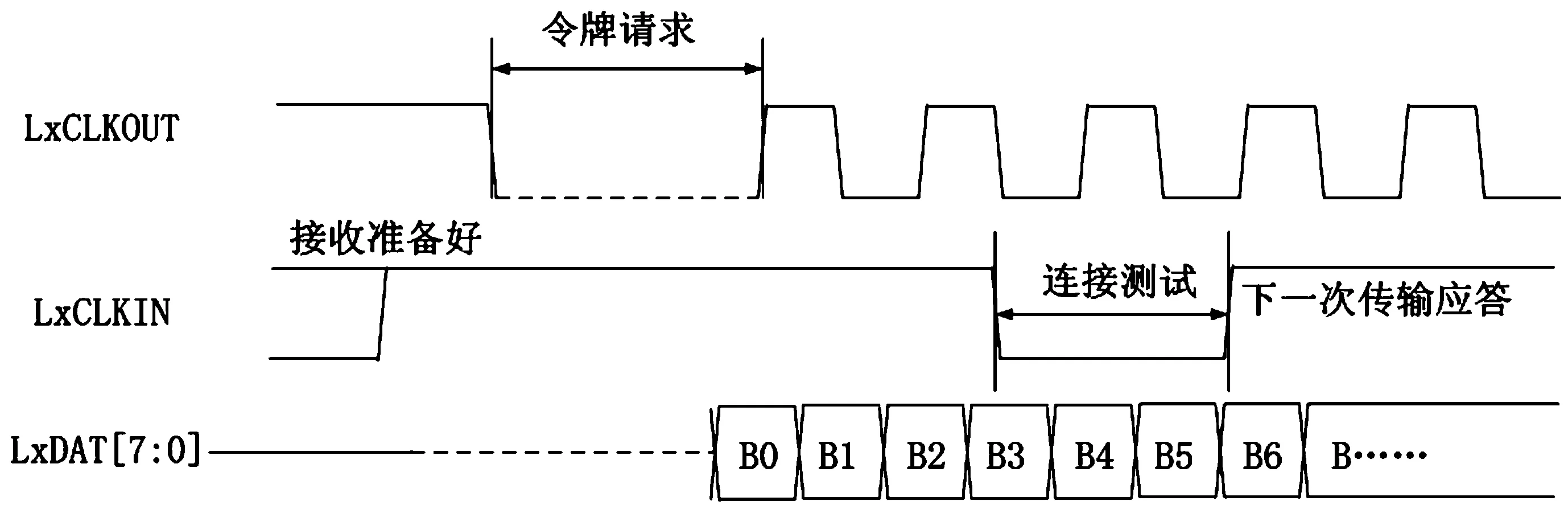

完整的Link协议传送启动过程如图 2所示.具体时序解释如下.

1. 发送端驱动其LxCLKOUT信号为低电平,以此向接收端发出令牌请求.

2. 发出令牌请求后,接收端等待6个周期,并验证其LxCLKIN(参照图1,该端口实为发送端的LxCLKOUT)是否依旧为高,若是则启动传送过程.

3. 传送过程启动一个周期以后,接收端将发送端的LxCLKIN驱动为低,以此作为连接测试.若接收完当前四字组之后接收端无法再收到另外的四字组,则接收端保持LxCLKIN为低.

图2 Link协议传输时序图Fig.3 Link protocol transmission diagram

在整个系统传输过程中,发送端驱动其LxCLKOUT端口做为同步时钟,而待传输数据则在LxCLKOUT的上升沿和下降沿时刻通过LxDAT锁存到接收缓冲中.

可以看出,Link协议需要采用双时钟沿传输数据,但FPGA设计中最重要的准则是同步设计准则[14],也即要求FPGA设计中的所有变量尽可能只在单一时钟的上升沿完成数据更新.而Link的DDR特性为FPGA实现带来了很大困难,为了解决该问题,必须将FPGA系统工作频率SCLK设定为Link时钟速率的2倍,所有Link收发器相关信号均在SCLK的上升沿更新,然后将SCLK时钟的两分频输出作为LxCLKOUT信号,以符合如图 2所示的Link通信时序.

2 Link收发器设计

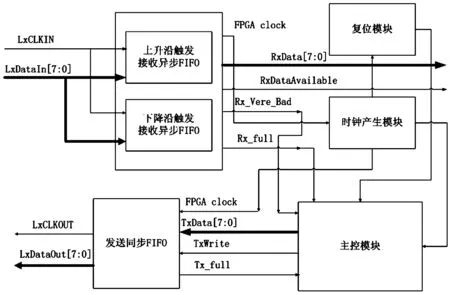

本设计基于Xilinx公司Virtex4系列XC4VSX35芯片,采用Verilog语言完成RTL级可综合代码设计,将所有Link协议操作均封装在FPGA模块内部实现.除Link接口信号外,其余模块输入输出信号均在同步时钟SCLK的上升沿处更新,符合同步设计准则,从而增强了系统的稳健性.图 3给出了整个Link收发器结构框图.

如图 3所示,左边信号为Link协议标准信号,其中输入数据LxDataIn和输出数据LxDataOut最终需要映射为FPGA的双向IO引脚,这可以通过在FPGA顶层模块中调用Xilinx公司的IOBUF原语完成双向数据端口实例化.可以看出,该收发器主要由3个子模块完成,以下分别介绍各子模块的关键设计.

图3 Link收发器结构框图Fig.3 Link protocol transiver diagram

接收异步FIFO:用于完成Link接口输入数据缓存及从LxCLK到FPGA Clock的跨时钟域转换.该FIFO事实上由两块FIFO并联构成,一块由LxCLKIN上升沿触发,一块由LxCLKIN下降沿触发,二者协同工作,即可在8个时钟周期内得到完整的16字节数据.该数据在FPGA系统时钟上升沿的触发下按顺序出现在RxData端口上,并置RxDataAvailable有效,此外,异步FIFO内部还集成了一个数据校验计算模块,当使能Link协议数据校验功能时,如果校验失败,Rx_Vere_Bad信号会置高,此时上级模块可视情况选择重新传输或者直接丢弃错误数据.

发送同步FIFO:用于实现Link接口的发送端数据缓存,该FIFO的读写时钟均采用FPGA内部SCLK,待传输数据通过TxData写数据端口和TxWrite写使能控制信号写入同步FIFO,此后同样在SCLK的配合下将数据通过LxDataOut输出,但是在模块外部看来,LxDataOut 即在LxCLKOUT的配合下通过LxDataOut发送出去.当FIFO缓充区满时,会通过TxBP和RxBP给出相应的标志信号,由上级模块视情况处理.

整个系统的任务高度则是由主控模块完成,它通过有限状态机(FSM)实现Link协议下的各种操作,由于状态较多,为减少状态译码复杂度及提高工作频率,采用独热码编码实现.该模块可支持Link数据发送、接收、字节校验等处理.其主要端口包括全局复位、传输超时信号、传输包长度指示信号、发送应答失败等信号.

时钟模块和复位模块的功能相对单一,前者主要采用FPGA内部的DCM基元生成高质量全局时钟,后者则用于实现所有寄存器的异步复位、同步释放.

3 FPGA实现及验证

基于ISE10.1开发套件,采用可综合Verilog代码实现上述设计,并在缺省设置下,基于Virtex5系列XC5VSX95芯片,顺利完成了布局布线,ISE最终报告该系统占用Slice为452个,仅占芯片全部可用资源的3%.经过静态时序分析,可知系统最小工作时钟周期为3.646 ns,相当于工作频率可超过270 MHz,由于Link总线共有8位数据并行传输,这意味着该Link收发器的数据传输速率可达4.32 Gb/s,在采用集成在ISE中的PlanAhead工具进行手动优化布局及延时约束后,最高工作频率更是可达300 MHz以上,等效数据传输率为4.8 Gb/s.而同样是8位数据总线,如果采用传统外总线结构,则最高只能达到800 Mb/s的传输速率,因此,采用Link协议完成数据通信性能优势十分明显.

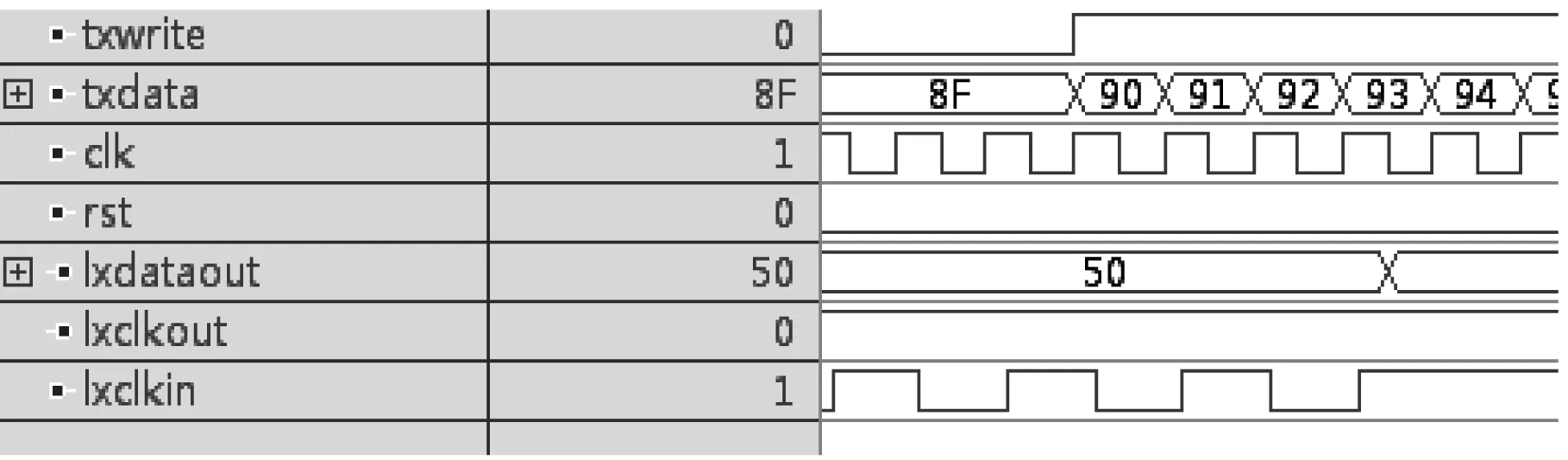

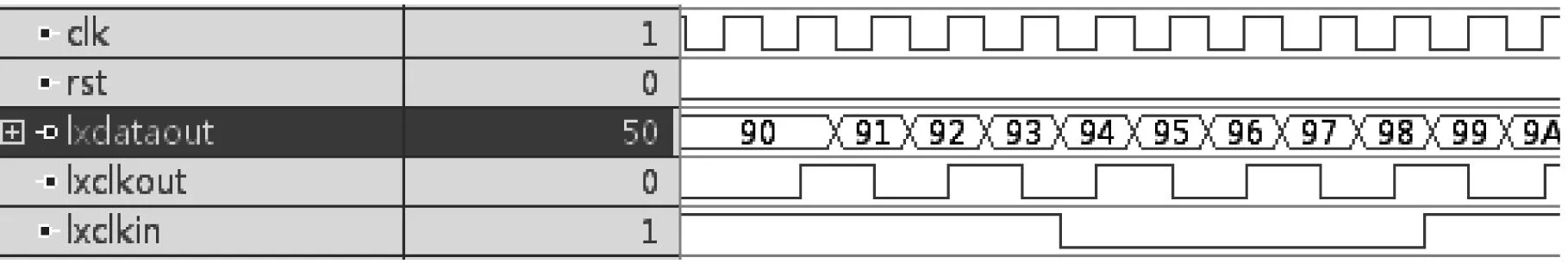

图4和图5给出了该Link收发器在Active HDL 8.2仿真环境下的时序图.

图4 Link收发器写发送数据时序图Fig.4 Data writing diagram of Link protocol transceiver

图5 Link收发器输出端口时序图Fig.5 Data outputting diagram of Link protocol transceiver

从图4中可以看出,FPGA通过该收发器的外部控制接口写入待发送数据0x90、0x91、0x92、…,注意此时所有写入数据均是在FPGA本地时钟的上升沿处更新.图5则是通过Link端口信号输出的数据波形图,可以看到,收发器成功完成了DDR数据传输功能,在LxCLKOUT的第一个上升沿发送第一个有效数据0x90,第一个下降沿则发送第二组数据0x91,直至最后一组数据,与图4所示发送数据完全一致,LxCLKIN输出时序也完全符合LINK接口协议.此外,需要强调的是,由图5中还可以看出,LxCLKOUT时钟沿与LxDataOut数据端口变化沿恰好相差半个时钟周期,这样可以保证Link收发器发送的数据在接收端具有最大的建立和保持时间余量,无须再进行烦琐的时钟相位调整即可直接采用双时钟沿寄存器完成数据接收,大大减轻了设计者压力.

该设计现已经在某精确制导预研项目雷达信号处理机中得到了成功应用,显著减少了数据传输时间,传输效率大幅度改善,最终使整个雷达信号处理算法具有更长的运行时间,进而加入更复杂的信号处理机制.而且随着处理要求的不断提高,多FPGA应用也已经成为雷达信号处理领域中的流行趋势.此时采用Link收发器完成FPGA片间数据交换也是极为合适的选择,可比传统的单数据速率SDR方案增加一倍的吞吐量,而且设计者可以在PCB板上自行增加LVTTL转LVDS差分驱动电路或直接采用FPGA的差分IO形式,此时最高工作频率、信号完整性及最大传输距离均可得到明显改善,但是需要注意的是:Link协议数据总线为双向端口,LVDS驱动电路也必须实现总线形式的LVDS,即Bus LVDS(BLVDS).

4 结论

在雷达信号处理机设计中,高速可靠的数据传输协议是整个系统的重要组成部分,一些常用的传输协议如SPI、I2C等已经在FPGA系统中得到了较多的运用,而为了在FPGA与DSP间完成大批量数据交换,SPI与I2C的串行传输数据吞吐量架构明显不能满足需要.因此,目前典型的设计思路是采用DSP的存储外总线方式来完成大批量数据交换,但此时数据吞吐率就严重受限于DSP本身的外总线带宽,一般只能达到100 MHz左右的主频,同时占用端口数量也非常可观,在许多雷达信号处理机中,由于实时性要求非常高,如果依然采用这种传统设计,则难以达到设计技术要求.因此,本文提出了一种基于目前广泛应用的ADI公司TigerSHARC101 Link通信协议高速数据收发器设计方案,全部设计基于可综合HDL代码完成,并在FPGA上顺利通过验证,以较低的资源占用实现了全功能高速Link收发器,并支持数据校验功能,经在XC5VSX95芯片中布线表明,最高传输速率可达4.8 Gb/s,可与ADI公司的TS101型DSP芯片或者其他FPGA形成无缝接口.整个设计并不依赖于具体FPGA芯片,具有较强的可移植性,目前已可支持Xilinx公司Virtex2,E, 4/5/6多个系列芯片.经过少量修改,也可用在Altera公司的FPGA中,通用性和实用性良好.