基于FPGA的CAN总线通信系统的设计

时旭++付成伟

摘 要: 为了避免单片机的缺陷,同时满足工业上稳定,精确的数据通信需求,在此提出了基于FPGA的通信系统,通过控制CAN控制器SJA1000,从而实现CAN总线的数据通信的设计。介绍了该系统的硬件结构和设计原理,针对FPGA的控制流程和原理进行了分析和设计;实验结果显示,该CAN通信系统满足通信需求,较以往的单片机CAN通信系统具有更高性能和优越性。

关键词: FPGA; CAN总线通信; CAN控制器; 数据通信

中图分类号: TN958?34; TP391.4 文献标识码: A 文章编号: 1004?373X(2015)22?0059?03

0 引 言

CAN总线全称为控制器局域网是一个可以多个主机同时使用的异步串行总线,是在国际上被应用最广泛的现场总线之一;而且其同时也是惟一被ISO国际标准化组织批准的现场总线。由于其优良的性能及独特的设计,CAN总线已经被广泛地应用在控制系统中。通常CAN总线的数据通信系统采用的是MCU(STM32等单片机)+CAN控制器(SJA1000)+CAN收发器(CTM8251T)的方案,但是单片机有诸多缺点的;所以本平台提出的设计方案采用FPGA(主控芯片)+CAN控制器(SJA1000)+CAN收发器(CTM8251T)的通信方案。与原始的通信方案相比,由于FPGA运行速度快、运算能力强、管脚相比单片机要更加丰富、在设计和实现大规模系统上更加出众,同时FPGA内部在执行程序时是并行运行的、在处理复杂逻辑上更突出,并且运行时系统的稳定性高,后期的扩展更加方便,所以本设计选用FPGA作为总体的模块控制器。

1 系统硬件设计

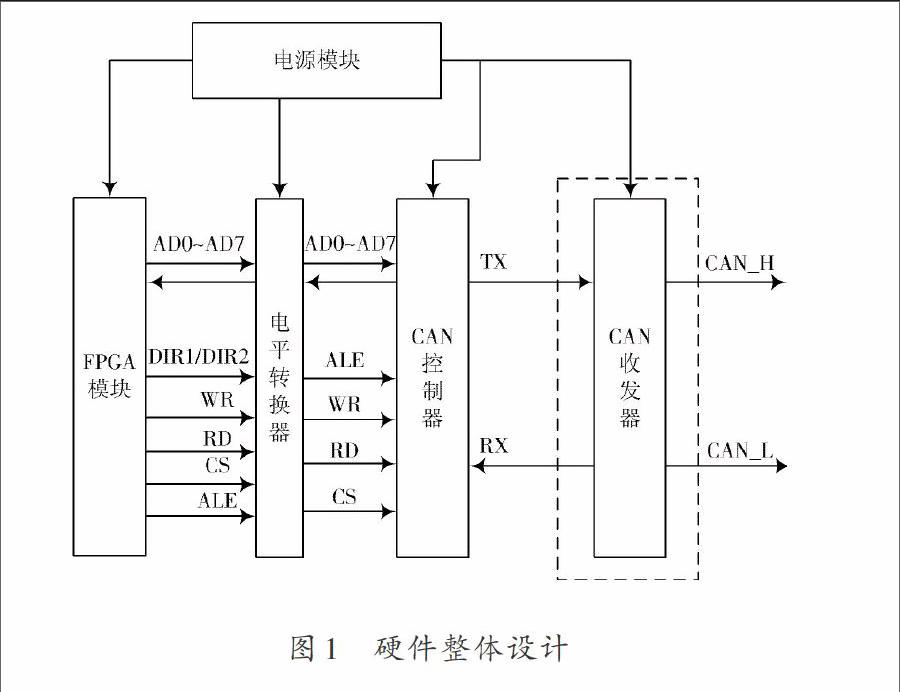

整个系统的总体硬件结构设计图如图1所示。

其中在硬件的选取上,FPGA模块使用的是以EP3C25为主芯片的EP3C25Q240芯片,采用EPCS16作为内部的配置芯片。芯片的等效逻辑门数量庞大,大约为65万门级,I/O口更是达到了173个,同时拥有4个PLL。其不仅功能强大,而且对后期的功能扩展和开发提供了便利的条件。因为电源模块没有特别的要求,采用LM1117(3.3 V)和LM1117(5 V),前者是将5 V转换成3.3 V,后者是将12 V转换成5 V。这两款芯片负责给除FPGA以外所有硬件供电,而FPGA应用自己本身的5 V电源进行供电。因为FPGA的I/O需要连接3.3 V,而CAN控制器输出电压为5 V,如果直接相连会导致I/O口烧毁,对FPGA造成损坏。所以通过一个电平转换器将电压转换成3.3 V,电平转换器选用SN74ALVC164245,这款电平转换器具有三态输出16位2.5~3.3 V或3.3~5 V电平转换收发器,非常适用于本设计。

CAN控制器选用Philips公司的SJA1000,CAN收发器选用的是CTM8251。CTM8251这款芯片本身带有隔离,抗干扰能力强,所以不需要设计隔离电路。为了避免干扰,提高CAN收发器接受的数据更加准确、稳定,在CTM8251的CAN_H,CAN_L之间连接一个120 Ω的阻抗匹配电阻。在使用SJA1000时,将RX1管脚接地,启用它的旁路功能,这样可以减少数据传送延时,提高通信的长度。最后进行试验,实验表明硬件设计可以实现CAN总线的数据通信。

2 FPGA控制程序和逻辑原理

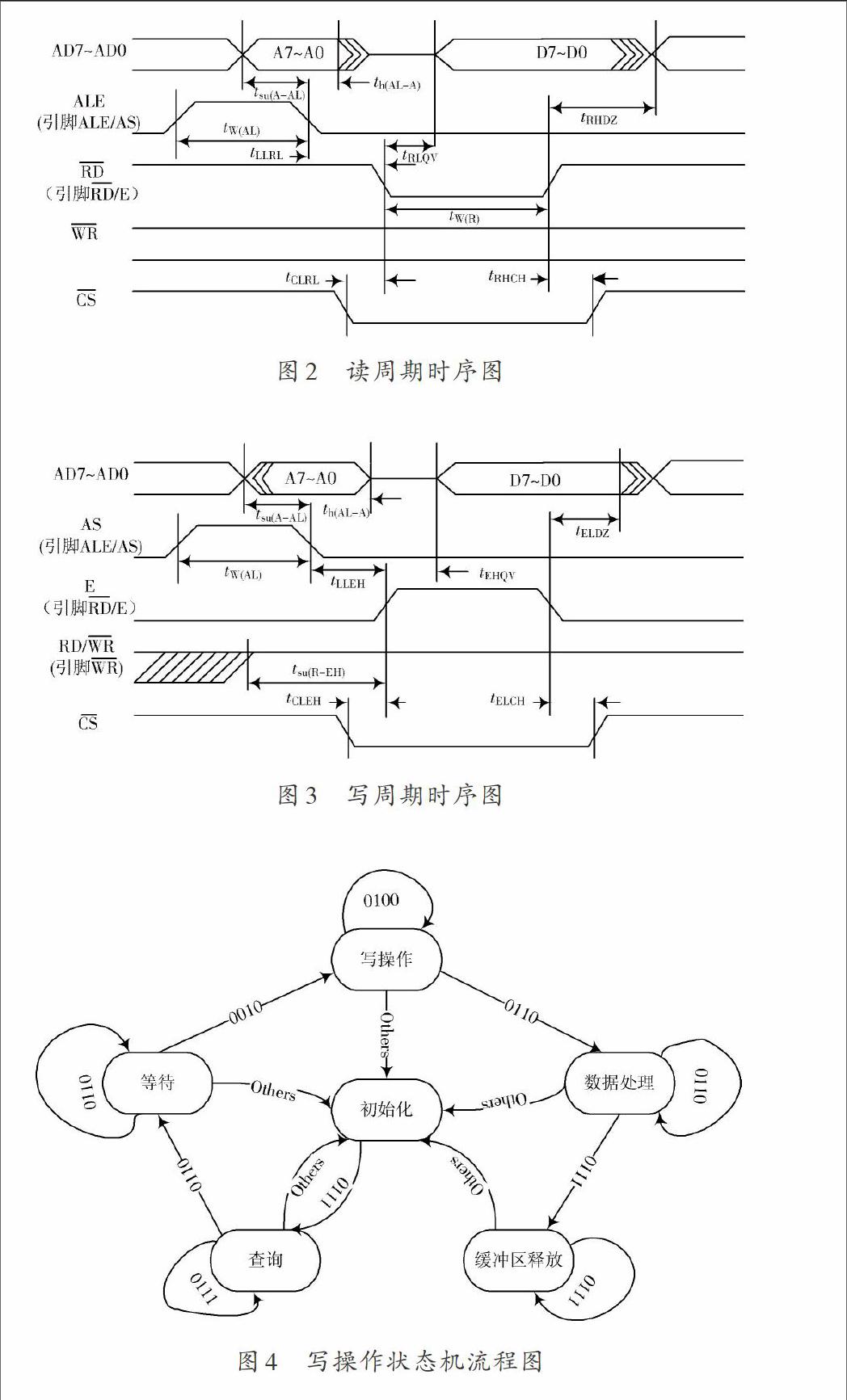

本设计的核心是保证FPGA与SJA1000之间的准确通信,为了保证FPGA与SJA1000之间能够准确无误的通信,在他们之间进行数据通信时,必须要按照SJA1000的时序逻辑进行通信。SJA1000的地址总线和地数据总线使用的是同一个总线而且是并行总线。在进行硬件连接、读/写操作时,采用的SJA1000工作模式为INTERL模式。该模式下的信号有[RD],[WR],ALE,[CS],ADD和DATA。[RD]为读信号,低电平有效;[WR]为写信号,低电平有效;ALE为地址锁存,下降沿有效;[CS]为片选,低电平有效;ADD是地址总线;DATA为数据总线。在编写FPGA的控制逻辑时,需要严格根按照SJA1000的读/写时序图。如图2为SJA1000读周期时的时序图,图3是其写周期时的时序图。

对SJA1000进行写操作时的状态图如图4所示。根据ALE,[RD],[WR]和[CS]的状态,进行状态机的转移。

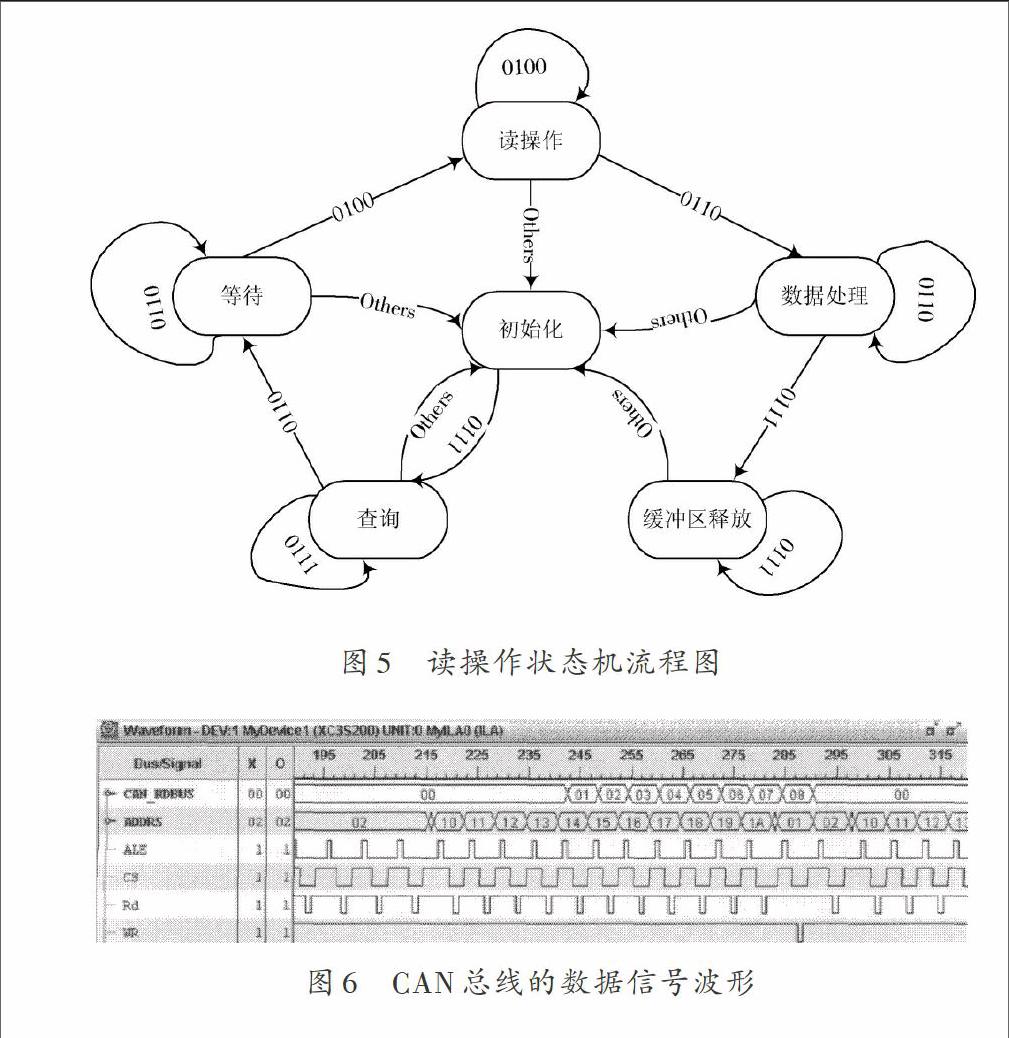

在系统启动时,程序首先对SJA1000进行初始化,初始化完成后,进行查询,检测ALE管脚的状态,当ALE出现低电平时,地址总线被锁定,并将此时的地址总线上的数据传输到SJA1000,否则程序会保持在查询状态;地址数据传输后,进入等待的状态机中,在等待状态,地址已经被锁定,设置好片选信号,同时检测写操作[WR]的信号时钟状态,当写操作的信号为有效时,进入写操作状态,在写操作状态,检测WR信号,当WR信号出现低电平时,将数据锁定,并将数据传输到SJA1000,数据处理则是当查询到发送缓冲区有数据后,写入帧数据,同时对数据帧进行处理,而缓冲区则是在数据处理完成后将缓冲区进行释放。这样FPGA内部程序就通过状态机的转移完成SJA1000数据的写操作。根据同样的原理可以利用FPGA对SJA1000进行数据的读操作。读过程中根据的是3 程序仿真

本设计在Quartus 8.0和Modelsim软件上进行程序的编写和程序的综合及仿真,并在实际应用上得到了验证。验证过正中,应用周立功的USB?CAN Ⅱ和上位机的ZLGCAN软件进行CAN总线的数据通信,同时应用ChipScope软件进行数据监控和测试,采用的测试数据为00,01,02,03,04,05,06,07,这样的数据既容易观察又可以验证通信的准确性。数据波形如图6所示。

4 结 语

该设计采用以FPGA(EP3C25)作为系统的主控制器,满足了系统的需求。与以MCU为控制器的原始系统相比,主控制器的功能和运算能力更加强大;同时本设计在硬件结构上进行了改进,使通信速度和通信的最大长度得到提升,而且本设计运行的稳定性高,扩展性强,应用市场更加广泛,为CAN总线的通信方式提供了更好的应用基础。

参考文献

[1] 刘涛.CAN总线接口电路设计中的关键问题[J].工矿自动化,2007(2):100?101.

[2] 张培坤,高伟,宋宗喜,等.基于FPGA的CAN总线通信节点设计[J].仪表技术与传感器,2010(12):68?70.

[3] 杨恒.FPGA/CPLD 最新实用技术指南[M].北京:清华大学出版社,2005.

[4] 张绍忠,王辉.基于SJA1000的CAN总线智能节点实现[J].电子技术应用,2006(8):22?24.

[5] 邬宽明.CAN 总线原理和应用系统设计[M].北京:北京航空航天大学出版社,1996.

[6] 刘向明,方建安.CAN总线网络的实时性研究和改进[J].现代电子技术,2011,34(22):46?49.

[7] 邱浩淼.基于CAN总线的在线更新机制的设计与实现[J].现代电子技术,2013,36(12):78?80.