基于RapidIO互联网络的多DSP加载方法研究

李尔效

(海军装备部,甘肃兰州 730070)

数字信号处理器(DSP)是专用于信号处理的微处理器,其处理能力强,可以使工程师较好地掌握实时性。因此,雷达系统中广泛使用多DSP系统来实现对大量信号数据的并行处理。ADSP-TS201是美国ADI公司推出的一款高性能DSP。它采用超级哈佛结构,最高工作主频为600 MHz,支持3.6 GFlops峰值浮点运算。

一套多DSP系统启动后,根据用户指令,DSP程序加载文件经过网络中各结点的路由转发,最终部署到对应的结点上,这一过程称为网络加载[1]。实时性是多DSP系统网络加载的关键指标之一,其要求系统在用户指令发出后的规定时间内,完成对所有结点的加载,正确地进入工作状态。

对多DSP系统程序的网络加载通常有两种思路。其一是通过上位机经总线给各DSP加载程序,加载数据保存在上位机端。这样可以通过上位机频繁地对系统进行复位、加载、查询内存等操作,这种加载方式的加载时间受制于上位机模块的性能,无法保证实时性。雷达系统定型后,出于系统简化和压缩成本的考虑,通常没有上位机模块,因此这种加载方式通常用在系统的调试阶段;其二是把程序存在片外Flash中,系统启动后,DSP程序从外部Flash加载到DSP上,由DSP来进行相应的处理。这种加载方式避免了程序加载的手动操作,一般用在系统的定型生产阶段。

文献[2~3]提出了几种网络加载方案,这些方案存在系统工作时总线负载过大、中继结点多、加载路径复杂等不足。针对这些局限性,本文基于目前最为高效的RapidIO嵌入式互联网络,设计实现了一个基于片外FPGA+RapidIO网络的多DSP加载模式,达到了降低总线负载、减化加载路径、保证加载实时性的目的。

1 多DSP网络加载设计

1.1 ADSP-TS201的引导方式

ADSP-TS201支持3种引导模式来对其加载程序,分别为Host引导,EPROM(Flash)引导和Link口引导[4-5]。3种引导方式均先通过某一DMA通道将引导核放置在DSP内存的0x00~0xff地址上,然后在DMA中断中从0x00开始执行引导核程序。引导核程序再启动一个 DMA将主程序加载,最后启动一个256words的DMA使引导核自身被程序代码覆盖。3种引导方式的不同仅体现在数据传输的路径上,如表1所示。文献[4~5]对3种模式下的引导方式做了详细描述。

表1 不同引导方式下数据传输路径

1.2 现有若干网络加载方案讨论

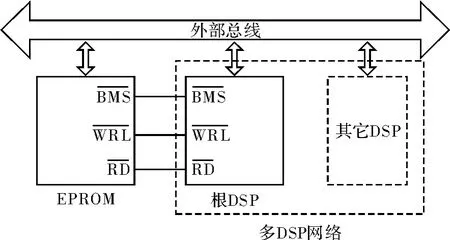

(1)文献[2]提及一种EPROM+总线的多DSP程序加载方案。其根DSP设置为EPROM(Flash)引导模式,其余DSP设置为Host引导模式。根DSP完成加载后,通过多处理器空间向其他DSP的AutoDMA通道写入引导核。此方案要求所有DSP挂接在同一根总线上,若系统中的DSP数量较多,那么在系统工作过程中总线负载过大,可能会频繁出现总线冲突与延迟,不利于保证数据交互的正确性和实时性。加载方案如图1所示。

图1 加载方案1的连接框图

(2)文献[3]介绍了一种Flash+Link通道的多DSP程序加载设计。其DSP系统中,根DSP与Flash直连,引导方式设置为EPROM(Flash),直接从Flash实现加载,其余DSP引导方式设置为link口加载,其加载文件经过路由,通过link网络实现加载。加载方案如图2所示。这种方案解决了DSP工作中总线冲突的问题。但此方案仍存在不足:1)根DSP是所有加载数据的唯一入口,对DSP数量较多的网络来说,入口唯一会导致DSP网络中各DSP加载路径复杂,不能灵活配置。2)此方案无法接受外部控制信号,只能加载一套固定的程序。在现代嵌入式实时信号处理系统中,常常要求系统在多种模式下工作,这就要求在系统的Flash中保存多种模式的程序,由系统控制加载某种模式的程序。3)此方案不能适应不同封装的Flash芯片,通用性受限制。

图2 加载方案2的连接框图

1.3 多DSP加载方案设计

为克服以上两种方案的局限性,文中提出了使用FPGA+RapidIO网络的高性能网络加载方案。在FPGA中,实现了加载控制接口、Flash访问接口和RapidIO接口。Flash访问接口与 FPGA连接,实现了 FPGA对Flash芯片中数据的读写;加载控制接口连接控制信号,可获取用户发出的加载命令和系统模式切换命令;RapidIO网络可作为传输网络,将加载程序分发给各个DSP。加载方案如图3所示。

图3 加载方案3的连接框图

本方案一方面利用了FPGA的可编程性,实现了对多种Flash芯片的支持,另一方面,利用高效RapidIO互联网络实现了加载程序的高效传输,大幅缩短了加载过程中的数据传输延迟。

(1)DSP与FPGA间的通信协议。DSP网络与Flash的交互通过 FPGA间接实现。DSP网络通过RapidIO发送一定格式的指令给FPGA,FPGA得到指令数据后,依照DSP与FPGA的通信协议对指令数据进行解包,并进行相应的操作。反之,FPGA也会按照通信协议通过RapidIO发送一定格式的命令或数据给DSP。这一通信协议实现了以下功能:1)FPGA从Flash芯片中获取加载数据,通过RapidIO口发送给DSP网络,实现DSP网络中各结点的加载。2)DSP把需要烧写进Flash的数据通过RapidIO网络发送给FPGA,FPGA获得数据后烧进 Flash。3)DSP要求FPGA读Flash数据,FPGA把Flash中指定地址的数据通过RapidIO发送给DSP,用于校验Flash烧写正确性。4)根据DSP的指令,FPGA格式化相应区域的Flash,或是格式化全部Flash。

(2)Flash的在线编程。DSP程序从Flash加载前,要先完成加载数据Flash中的烧写。对Flash的在线编程(in-circuit programming)[6]是指嵌入式处理器运行内部程序去改写Flash的内容。通过对Flash的在线编程,可以灵活地安排Flash内部的数据存放格式,满足多功能雷达系统的需求。

本方案中,对Flash的在线编程系统由上位机软件、任意一片与FPGA直连的DSP(文中称为DSP0)、FPGA、Flash组成。Flash在线编程的路径如图 4所示。

图4 Flash在线编程的路径

上位机软件首先把DSP网络中各DSP的加载程序打包成烧写文件,然后通过PCI总线加载DSP0服务程序,并把待烧写数据发送给DSP0。

DSP0收到烧写文件后,解析其中的信息,然后按照DSP与FPGA之间的通信协议,通过DSP总线把烧写数据发送给FPGA,最终由FPGA将加载文件数据写进Flash。

(3)DSP网络加载过程。系统加载时,所有DSP都设置成以Host方式引导。FPGA的加载控制接口接收到来自用户的加载系统或切换模式命令后,从Flash中读取相应的加载数据,通过RapidIO交换网络,以广播方式将加载数据发送到每个DSP节点上的FPGA中。然后由每个FPGA通过Host加载模式为连接的DSP加载程序。

与前两种加载方案相比,此方案的优势在于:(1)各DSP可分布于若干条总线上,让DSP工作时的总线负载降低。(2)可根据外部命令,识别系统所在的模式状态,从而选择加载不同程序。(3)能适应不同封装的Flash芯片,通用性强。(4)基于高效的RapidIO传输网络进行加载数据传送,大幅提高效率,缩短加载延迟。

2 工程应用

2.1 系统平台构建

信号处理模块采用cPCI板型,每个模块板载8片ADSP-TS201处理器。每个模块可实现28.8 GFlops的处理能力。模块上的FPGA实现系统PCI总线到局部PCI总线的转换,每个处理节点内部共享局部PCI总线,板卡上每4个DSP连接到一个FPGA上,每个FPGA实例化了一个RapdiIO接口与交换网络互联,板卡架构如图5所示。

图5 信号处理模块结构框图

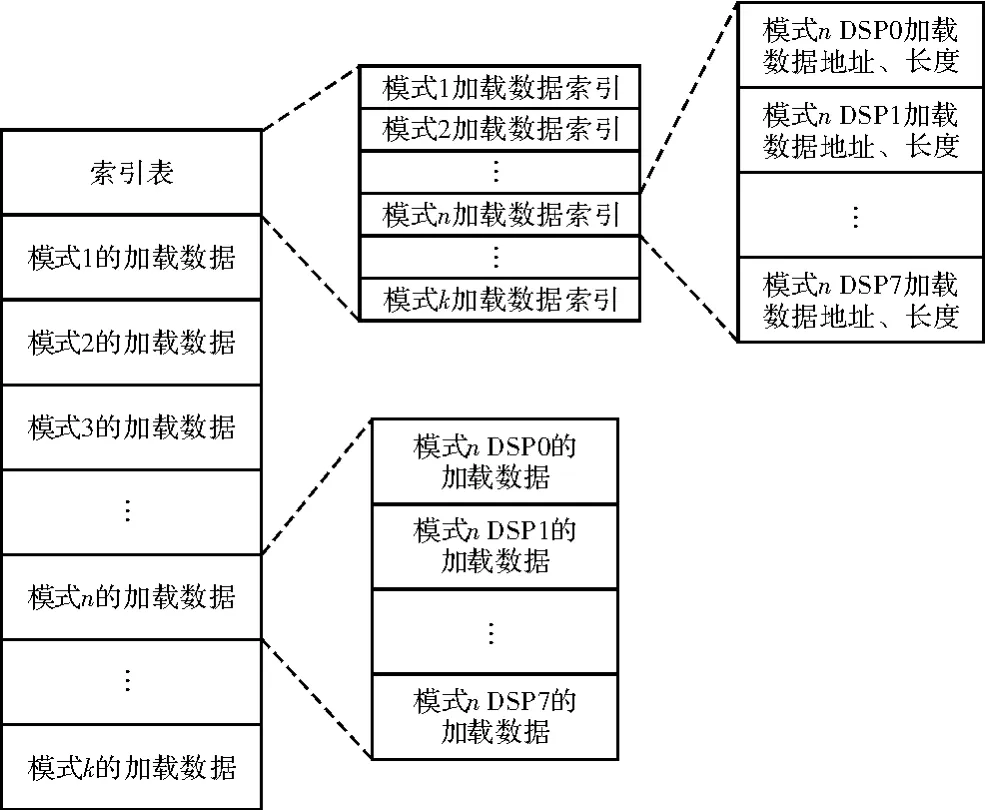

2.2 基于Flash的加载数据存储格式

设计要求FPGA能够根据系统命令对DSP加载不同模式的程序,为使FPGA能够获得不同模式下各DSP加载数据的在Flash中的首地址和长度,文中在Flash中设计一个索引表,FPGA在得到加载DSP的命令后,首先查询索引表,获取对应加载数据的地址、长度信息;然后FPGA再从Flash的对应地址获得加载数据,发送给DSP网络。在索引表之后,再顺序排列各套程序,Flash内数据存放格式如图6所示。

图6 Flash内数据存放格式

在Flash烧写的过程中,DSP需要按照这一格式对Flash进行在线编程,以保证在程序加载时FPGA能在对应的地址获得正确的数据。

2.3 加载数据路由与网络加载

系统上电后,系统中的各DSP设置为Host引导方式。FPGA监听加载控制接口传来的命令,收到加载或切换模式命令后,FPGA从索引表中查询对应加载数据的地址和长度信息,再从Flash芯片中读取对应模式的加载数据,基于RapidIO口通过广播模式,将加载数据发送给每个处理节点的 FPGA,每个处理节点FPGA接收到加载数据后,通过DSP总线将程序加载到与其连接的DSP上,系统中DSP的加载路径如图7所示。

图7 系统中DSP的加载路径

3 结束语

本文介绍了一套多ADSP-TS201系统的程序加载设计,设计的优势在于:(1)摒弃DSP与Flash直连的模式,采用FPGA+RapidIO网络形式,以FPGA为中介连接Flash。Flash的烧写、读取都交由FPGA来完成,FPGA通过RapidIO口进行通信。同时,FPGA通过加载控制接口接收用户指令。此方案充分利用了FPGA构建系统的灵活性,降低了总线负载,减化了加载路径,保证了系统加载的实时性,实现了系统多种模式间的灵活切换。(2)若干DSP通过RapidIO从获取加载数据,这样的设计保证了加载实时性。本设计已应用于工程实践中。实际应用结果证明,该方案提供了一种使用简便、安全可靠的基于Flash的多ADSPTS201网络加载方案。

[1]卫晋,刘峰,龙腾.大规模多DSP实时网络加载系统关键技术研究[J].计算机工程与应用,2007,43(5):236 -241.

[2]潘伟,于宁.TS201S型 DSP引导程序加载方法研究[J].国外电子元器件,2005(12):14-17.

[3]张宁,冯小平.链路口耦合的多片ADSP-TS101系统程序加载[J].技术前沿,2006,8(12):53 -57.

[4]Analog Device Inc.ADSP - TS201 TigerSHARC processor hardware reference revision 1.2[M].USA:Analog Device Inc,2005.

[5]Analog Device Inc.VisualDSP++5.0 loader and utilities manual revision 2.0 [M].Tex USA:Analog Device Inc 2007.

[6]刘峰,卫晋,龙腾.多DSP系统独立加载模块在线编程软件设计[J].计算机工程,2007,33(14):260 -263.

[7]王琤,王燕,龙腾.TS101 DSP Flash引导程序的设计和实现[J].计算机工程,2006,32(21):270 -272.

[8]刘书明,罗勇江.ADSP TS20XS系列DSP原理与应用设计[M].北京:电子工业出版社,2007.

[9]高立宁,龙腾.基于TS201与FPGA的信号处理系统[J].微计算机信息,2008,24(32):260-261.