PLL驱动DDS的低相噪小步进LFM信号源设计*

王文才,陈昌明,黄 刚

(成都信息工程学院通信工程学院,成都610225)

WANGWencai,CHEN Changming* ,HUANGGang

(School of Communication Engineering,Chengdu University of Information Technology,Chengdu 610225,China)

信号源是电子系统中不可缺少的重要组成部分,在微波通信、雷达系统、仪器仪表等领域具有广泛的应用。而频率合成技术是一种专门用于产生高性能信号源的先进技术。它包括直接模拟式(DAS)、间接锁相式(PLL)和直接数字式(DDS),其中DDS合成方式虽然输出信号频率较低,通常只有几百兆,但其具有频率分辨率高、转换速度快、体积小、可编程等优点,能很好地满足对多种复杂形式信号输出的要求[1-3]。因此现代雷达体系中复杂调制信号的产生往往是利用DDS技术在较低频率产生中频信号,然后通过变频方式将其搬移到更高的所需频段。而高线性度、低相噪的线性调频信号非常符合毫米波等雷达在体积和精度方面的要求[4-5]。文章正是基于这一点,结合DDS和PLL各自的优点,采用PLL驱动DDS的方式设计了一种低相噪、杂散、小步进的LFM信号源。

1 系统方案

本方案要求输出线性调频(LFM)信号中心频率为60 MHz,带宽10 MHz,扫频频率步进1 kHz,相位噪声优于 -100 dBc/Hz@1 kHz,杂散抑制大于 -60 dBc,输出功率大于-5 dBm。信号采用PLL驱动DDS的模式输出。由于设计中线性调频信号要求的频率不高,故采用DDS频率合成方式得到。AD9910在1 GHz系统时钟驱动下可输出高达400 MHz的模拟信号,相位噪声优于-125 dBc/Hz@1 kHz,频率分辨率优于0.23 Hz及以上。为使杂散抑制也满足指标要求,文章通过设计低杂散高精度的锁相环路(PLL)为AD9910提供1 GHz的时钟参考。100 MHz的恒温晶振提供给HMC704鉴相器,FPGA作为外部控制器通过串行SPI总线对PLL和DDS内部寄存器高速配置,得到所需的信号输出。系统总体框图如图1所示。

图1 总体框图

1.1 DDS设计与杂散分析

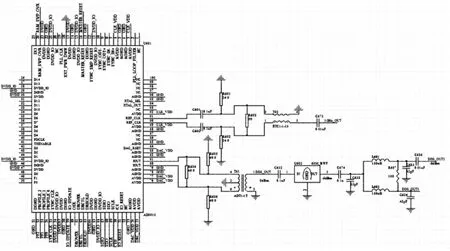

系统硬件设计时DDS外围参考时钟和输出模块的设计是关键。图2是包含AD9910参考时钟输入以及输出模块的电路原理图。根据DDS的原理,对其输出正弦-阶梯波的表达式傅立叶变换得到DDS 的理想频谱分布为[6]:

其中Sa(x)=(sin x)/(x),由式(1)可知:理想DDS杂散的主要来源是系统抽样函数δ(t=lTc),即由参考时钟fc引起,因此必须设计高精度时钟。为设计出杂散和相噪满足要求的LFM信号源,利用PLL控制VCO设计了1 GHz的参考时钟提供电路。

另外,由式(1)知DDS输出信号中存在较多的杂散干扰,当输出频率离fc/n(n=3,4,…)很近时,杂散分量fc-(n-1)f0和(n+1)f0-fc将离f0很近,特别是当输出信号是具有一定带宽的LFM信号时,由于对滤波器选择性要求太高而工程无法实现,因此应用中应避开这些频点[7-8]。设计方案中DDS输出LFM信号在这些频点之外。

1.2 锁相点频源设计

采用HMC704LP4控制VCO的方式设计了1 GHz的锁相环点频源,为DDS提供低相噪、高杂散抑制度的参考时钟。其中HMC704LP4内部集成了鉴相器、精密电荷泵、参考分频器R、可编程分频器N,是一款低相噪小数分频锁相环芯片,其相位噪声可达-112 dBc/Hz@50 kHz。采用的Delta-sigma调制技术能有效的改善分数杂散性能,使得锁相环输出信号的杂散满足系统要求。VCO选用mini公司的ROS-1000C-319+,其单边带相位噪声为 -126 dBc/Hz@10 kHz。

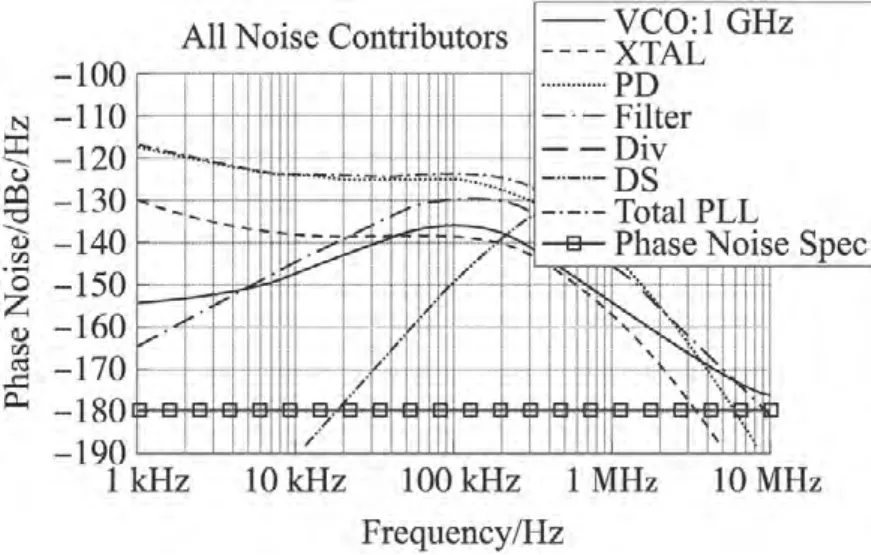

综合考虑相位噪声、杂散、稳定性和捉捕时间等要求,设定环路滤波带宽200 kHz,鉴相频率为50 MHz,相位裕度55°。采用 Hittite公司 PLL Design Tool软件,设计三阶无源滤波器并对锁相环路输出频率在1 kHz~10 MHz频偏范围内的相噪仿真如图3所示。

图2 部分DDS原理图

图3 1 GHz相噪仿真曲线

由图3知设计的锁相点频源总体相噪小于 -120 dBc/Hz。

1.3 LFM信号参数计算与配置

AD9910内部集成的数字斜坡发生器能很好的模拟线性调频信号的输出。首先计算出DRG模式下DDS的寄存器参数。然后经SPI总线将频率控制字等信息写入AD9910相应的寄存器中。

(1)寄存器参数计算

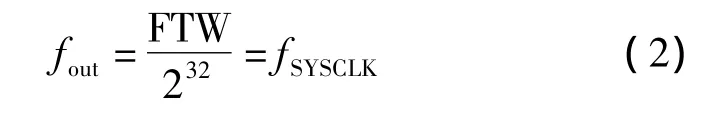

DDS实际上是一个分频系统,其输出频率fout与系统时钟fSYSCLK之间的关系如式(2)所示[9]:

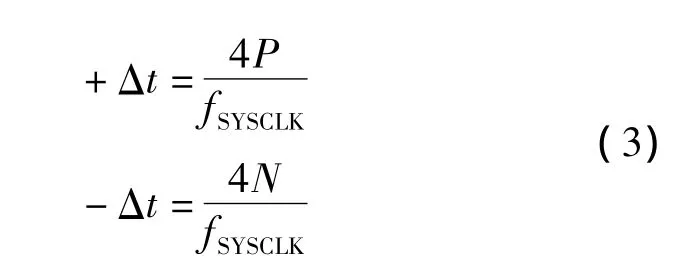

其中,FTW为频率控制字。DRG模式还需要配置的参数包括:扫频上限和下限频率以及扫频步进和步长。其中正、负斜率步进间隔(Δt)由式(3)计算得到:

P和N是保存在32 bit数字斜坡寄存器中的两个16 bit数值。用步长控制字STEPN或STEPP计算出扫频信号实际频率步长为:

其中斜坡步长采用32 bit数值,由64 bit数字斜坡步长寄存器编程控制。

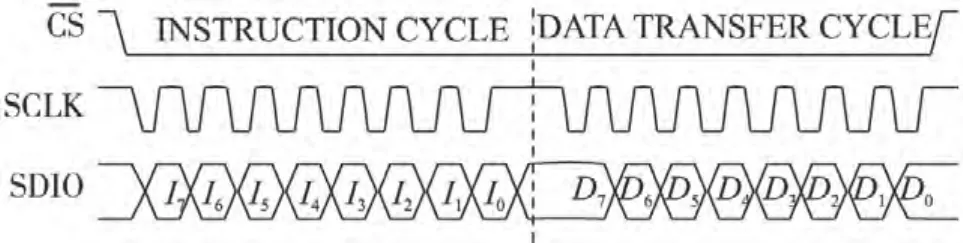

(2)SPI总线的时序要求

设计采用串行二线模式进行数据传输,其时序要求如图4所示。片选为低时,数据SDIO在时钟SCLK上升沿传输。通信周期的前半部分是指令阶段,用于读写控制和寄存器寻址。后半部分将控制信息向串行端口缓冲器中传输。

图4 AD9910串口时序

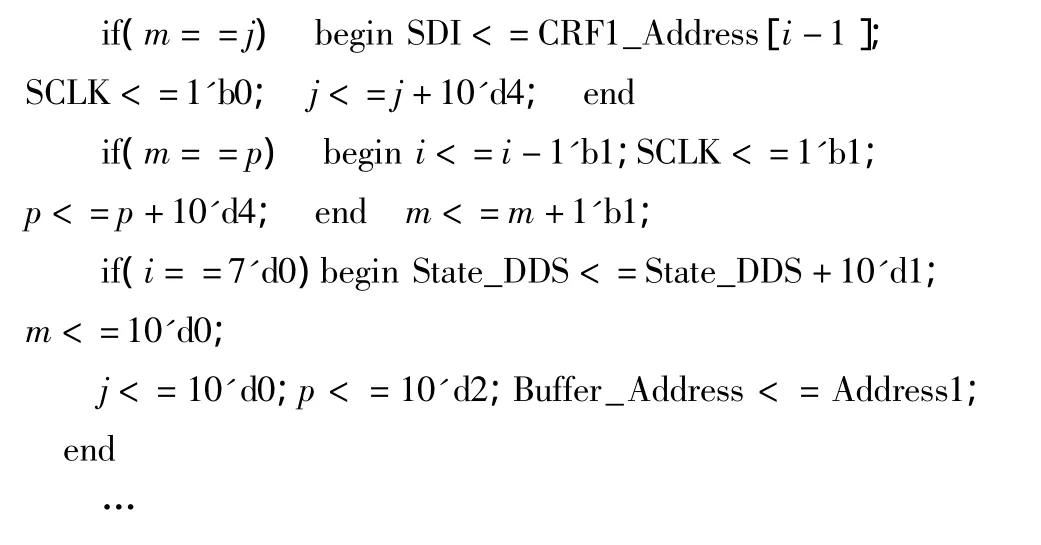

给出CRF1寄存器寻址的Verilog HDL代码:

(3)状态机设计

根据参数计算结果和SPI时序要求,设计FPGA控制程序。其状态图如图5所示,对应扫频模式下AD9910寄存器配置的4个步骤:(1)DDS系统初始化设置;(2)控制CRF寄存器,使能DRG模式;(3)将计算出的控制字等信息写入3个DRG编程寄存器;(4)通过DRCTL引脚控制斜率方向实现线性调频信号的输出。

2 测试结果分析

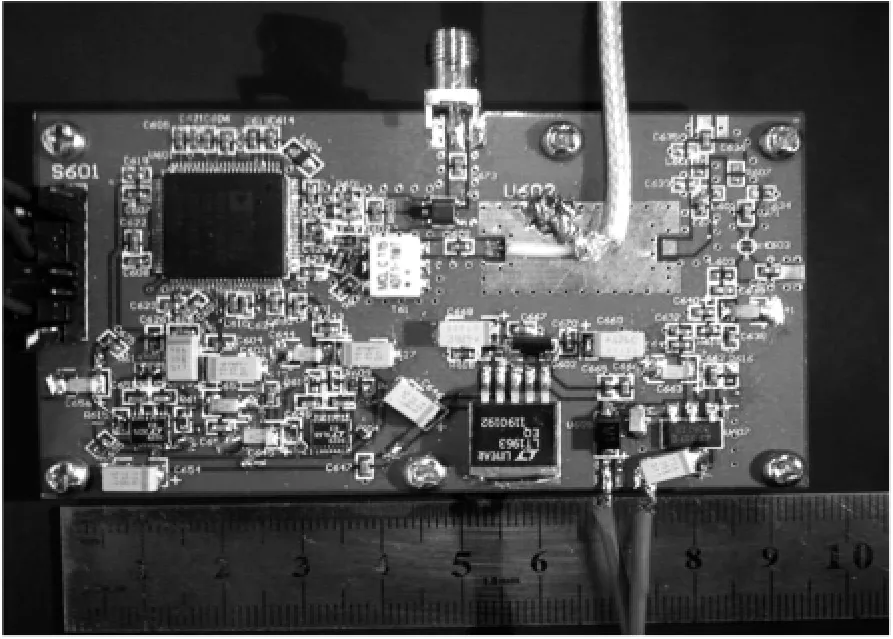

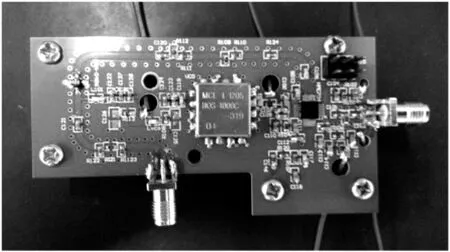

通过对环路滤波器和电路印制板优化设计,加工制作的线性调频信号源PCB板如图6所示。图7是设计的1 GHz锁相信号源。

图6 LFM信号源

图7 PLL点频源

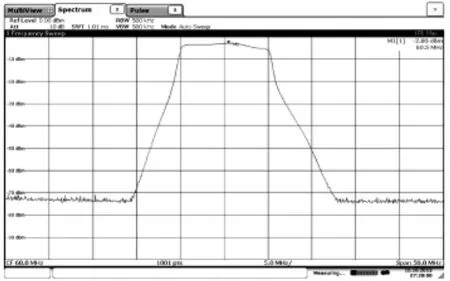

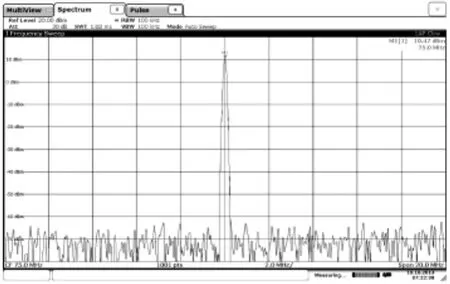

系统测试时,用设计的锁相源为DDS提供1 GHz的参考时钟,通过FPGA将频率控制字、扫频步进、扫频带宽等信息写入 DDS和 PLL,采用ROHDE&SCHWARZ公司的Signal Analyzer对设计的信号源测试,图8为LFM输出信号频谱图,为测试信号的相噪和杂散性能,给出单频信号频谱图如图9所示。

图8 LFM信号频谱图

图9 输出单频频谱图

由图8知输出LFM信号中心频率为60 MHz,幅度为-2.8 dBm,扫频带宽为10 MHz,频率步进1 kHz。脉内频率随时间呈线性调频关系变化,且线性度好。由图9知输出信号的相噪达到 -103 dBc/Hz@1 kHz,杂散已被设计的滤波器滤除。但脉冲内信号幅度略不平坦,这主要是由输出端滤波器带内插损不均等引起的。即便这样该频率源仍然能很好地满足工程要求。

3 结束语

本文充分利用DDS和PLL的优点,提出了一种低相噪小型化线性调频信号源的实现方案。实测结果表明:该信号源具有输出信号频率稳定度高、频谱干净、脉内线性调频信号线性度好、体积小等优点,通过一定的变频便可很容易的移植到更高频率雷达系统上。对设计同类乃至其他类型的信号源具有一定的借鉴意义。

[1] 江波,穆晓华,蒋创新.频率合成器的现状及发展[J].压电与声光,2011,33(4):637 -642.

[2] 江淮,李亚波,许建中.基于DDSAD9910的三角波调频信号[J].微波学报,2012,28(s1):498-500.

[3] Scheiblhofer S,Schuster S,Stelzer A.High-Speed FMCW Radar Frequency Synthesizer with DDSBased Linearization[J].Microwave and Wireless Components Letters,IEEE,2007,17(5):397 -399.

[4] 杨远望,蔡竟业,刘镰斧.毫米波低相噪捷变频高分辨率雷达频率源设计[J].电子技术应用,2011,37(10):56-59.

[5] Hu S.Performance Analysis of Frequency Sweep Nonlinearities in LFM Radars[C]//Electrical and Control Engineering(ICECE),2010 International Conference on.IEEE,2010:3977 -3980.

[6] Cui Weibo,Zhang Xiao,Lu Xiao,et al.The Design of High Performance X-Band Frequency Synthesizer Based on DDS and PLL[C]//Cross Strait Quad-Regional Radio Science and Wireless Technology Conference(CSQRWC),2013.IEEE,2013:97 -100.

[7] 李钱赞,张福洪.基于AD9910的跳频源设计[J].电子器件,2011,34(4):468 -472.

[8] 王江涛,於洪标,张建增.低相噪DDS信号产生电路的设计[J].微波学报,2007,23(z1):148-151.

[9] Analog Device Inc.AD9910 Datasheet[R].USA:Analog Device Inc,2008.