浅析PCB中DDR3等长线的设计

□ 文/蔡力峰

引言

随着科技的发展,产品要求有大的信息存储空间,SDRAM、DDR2、DDR3、DDR4等大存储空间的芯片也应运而生。一块电路板上,为了满足大容量的需求,常常是放置2片、4片、8片甚至更多的存储芯片,但是产品又多是趋于小型化设计,因此要求存储芯片的尺寸越来越小,小型的BGA封装正好能满足需求,所以目前主流的存储芯片多采用BGA的小型封装设计。DDR3通常也采用采用BGA封装,它的时序要求比较高,所以在PCB设计中对时钟、地址、数据、DQS等信号线要求做等长处理。本文结合实例对DDR3的等长线设计方法进行分析和论述。

DDR3主要信号线的分类及走线要求

DDR3主要信号线的分类

以16位DDR3举例,需要等长走线设计的信号有:

控制类信号:时钟信号CLK,CLK#,数据选通信号LDQS,LDQS#,UDQS,UDQS#,其他控制信号CKE,BA0-BA 2,LDM,UDM,CS#,RAS#,CAS#,WE#,ODT等

数据类信号:DQ0-DQ15

地址类信号:ADDR0-ADDR13

DDR3主要信号线的等长走线要求

单板PCB设计时要求传输线阻抗控制在50Ω±10%,时钟信号CLK,CLK#是差分信号线,一般要求差分阻抗为100Ω。线宽、线间距需要根据叠层结构来计算,与其他走线的间距要满足3w规则;另外,必需精确匹配差分线对走线误差,一般允许在10mil以内,具体误差要求可参照芯片设计手册。时钟信号CLK,CLK#,数据选通信号LDQS,LDQS#,RDQS,RDQS#,这三对信号线是差分信号线,通常要求差分线对的长度差小于5mil,并且线对间的线间距和走线宽度通常保持一致。DDR3的数据线DQ0-DQ15用DQS来锁存,因此要和DQS保持等长;地址、控制线用时钟来锁存,因此需要和时钟保持一定的等长关系,但不需要严格的等长,允有100mil的误差;而DDR3数据线和时钟线相比通常可以有200-300mi的公差。各类信号线具体走线要求如下:

时钟信号CLK是一对差分信号,长度要求如下:(1)CLK信号走线长度最长不能超过4inch;(2)CLK差分对信号走线严格走差分,差分线对的长度差推荐小于5mil,即:CLK-CLK# < 5mil;(3)CLK走线线宽和线间距不能小于4mil。DDR3时钟差分线阻抗控制在100Ω±10%。

数据信号线DQ[0∶15]的走线长度以数据选通信号DQS作为参考,偏差50mil,具体如下:DQ[7∶0]以LDQS的走线长度为参照进行走线,允许偏差范围为50mil,即:DQ[7∶0] = LDQS ± 50mil;DQ[15∶8]以UDQS的走线长度为参照进行走线,允许偏差范围为50mil,即:DQ[15∶8] =UDQS ± 50mil;数据线推荐以地层为参考平面,在无法满足的情况下,要求同组同层走线。

数据选通信号线DQS是两对差分信号,长度要求如下:(1)DQS差分对内部两根信号线严格等长,差分走线长度偏差推荐小5mil,即DQS-DQS#< 5mil;(2)DQS以CLK时钟走线长度为参照进行走线,其走线长度相对于CLK的走线长度,允许的偏差为±250mil,即:DQS = CLK± 250mil。

数据掩码信号线DM的走线长度以数据选通信号线DQS为参考,要求如下:(1)LDM以LDQS的走线长度为参照进行走线,允许偏差范围为50mil。(2)UDM以UDQS的走线长度为参照进行走线,允许偏差范围为50mil。

地址信号线ADDR[0∶13]的长度要求如下:(1)ADDR[0∶13]以CLK时钟走线长度为参照进行走线,允许的差范围为100mil,即:ADDR = CLK±100mil;(2)地址线采用T型走线,T点到CPU端管脚的走线,最长不超过2inch,T点到DDR3管脚的走线,最长不超过1inch。

控制信号线BA[0∶2]、DM、CKE、CS#、WE#、CAS#、RAS#、ODT的长度要求如下:(1)控制信号线以CLK时钟走线长度为参照进行走线,允许偏差范围为100mil;(2)为减小信号反射,建议所有DDR3 SDRAM的接口信号走线避免穿越电源地分割区域,保持完整的电源地参考平面。

实例分析

2片DDR3共用时钟线和地址线及控制线

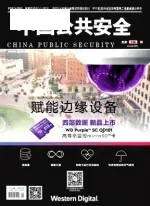

这种情况采用标准的T型走线。即从CPU到两片DDR3的时钟信号,地址信号及控制信号的信号线长度都要保证相等。即AT+TC=AT+TD。具体结构及PCB布线方式参见图1及图2。

▲图1 T型结构图

▲图2 T型走线PCB示意图

从CPU到两片DDR3的地址/控制信号线走线长度为LAC及LAD,钟信号线CLK走线长度为LCLK,要求LAC=LAD=LCLK。数据信号线DQ0-DQ15和数据选通信号DQS1等长,DQ16-DQ31和数据选通信号DQS2等长。

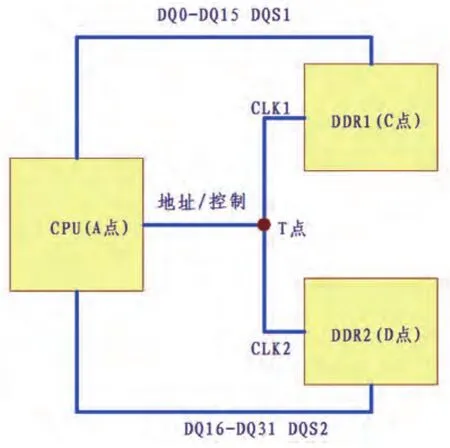

2片DDR3共用地址线及控制线,时钟线不同,T型走线方式

这种情况采用类似T型走线方式走线。即从CPU到两片DDR3的地址信号及控制信号的信号线长度和各自时钟信号等长。具体结构示意图参见图3。

从CPU到两片DDR3的地址/控制信号线走线长度为LAC及LAD,时钟信号线CLK1走线长度为LCLK1,时钟信号线CLK2走线长度为LCLK2,要求LAC=LCLK1,LAD=LCLK2。数据信号线DQ0-DQ15和数据选通信号DQS1等长,DQ16-DQ31和数据选通信号DQS2等长。

▲图3 不同时钟线的T型走线方式

▲图4 不同时钟线的菊花链走线方式

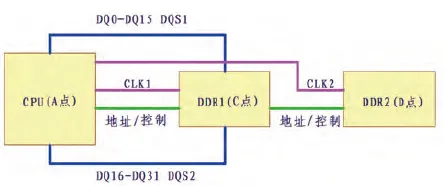

2片DDR3共用地址线及控制线,时钟线不同,菊花链走线方式

这种情况采用菊花链走线方式走线。地址信号及控制信号从CPU出发先到DDR1再到DDR2,两片DDR的时钟信号不一样,走线时DDR1的地址信号及控制信号和时钟信号线CLK1等长,而到达DDR1的地址信号及控制信号和时钟信号线CLK2等长。具体结构示意图参见图4。

从CPU到两片DDR3地址/控制信号线走线长度为LAC及LAD,DDR1到DDR2地址/控制信号线走线长度为LCD,时钟信号线CLK1走线长度为LCLK1,时钟信号线CLK2走线长度为LCLK2,要求LAC=LCLK1,LAD=LCLK2,其中LAD=LAC+LCD,数据信号线DQ0-DQ15和数据选通信号DQS1等长,DQ16-DQ31和数据选通信号DQS2等长。

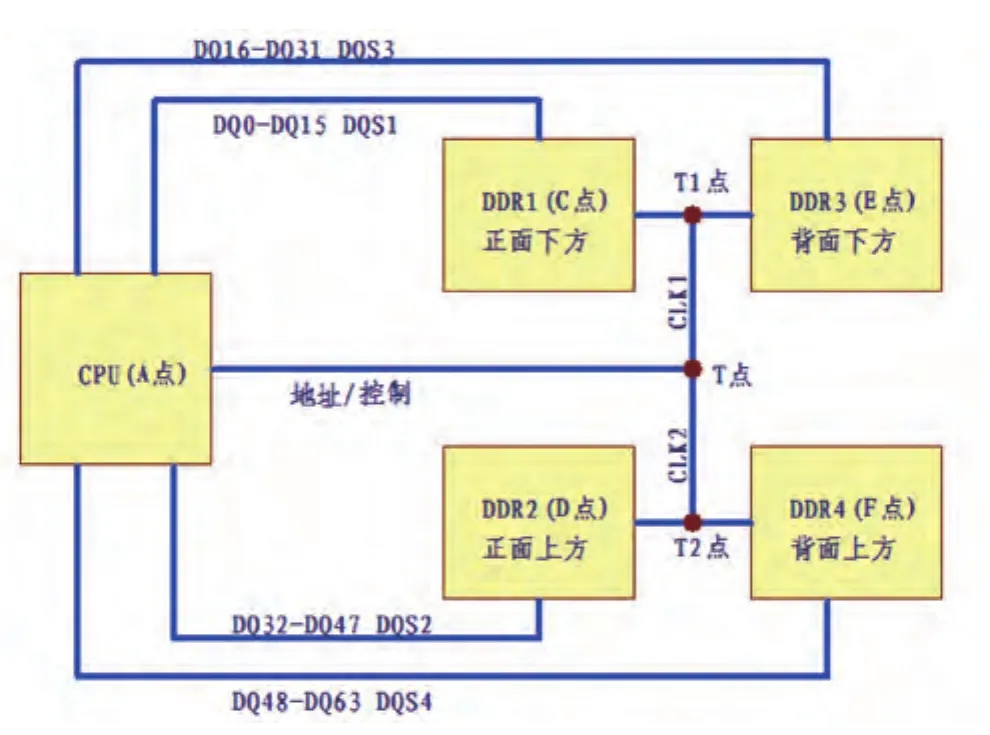

4片DDR3共用地址线及控制线,两组时钟线,T型走线方式

▲图5 4片DDR3的T型走线方式

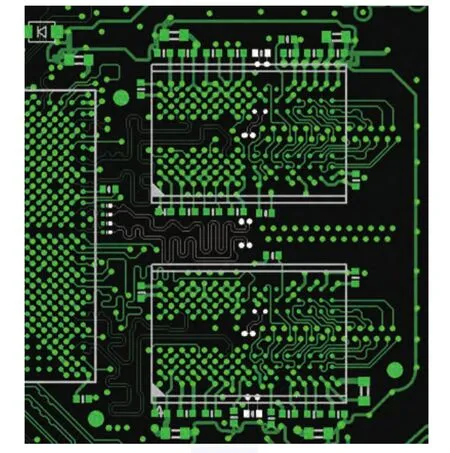

▲图6 2片DDR3正面放置

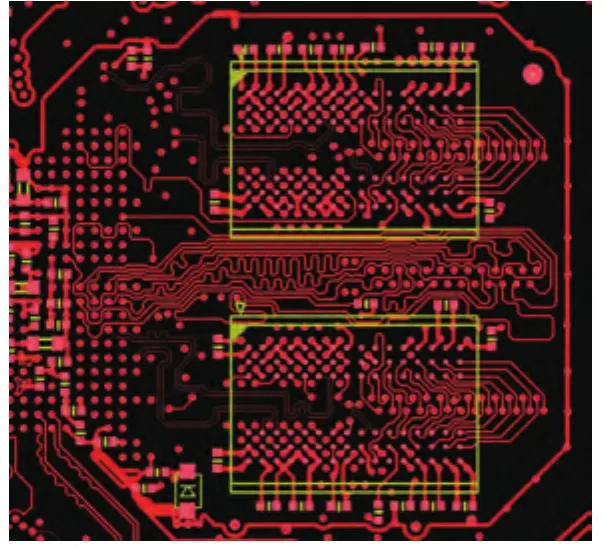

▲图7 2片DDR3背面放置

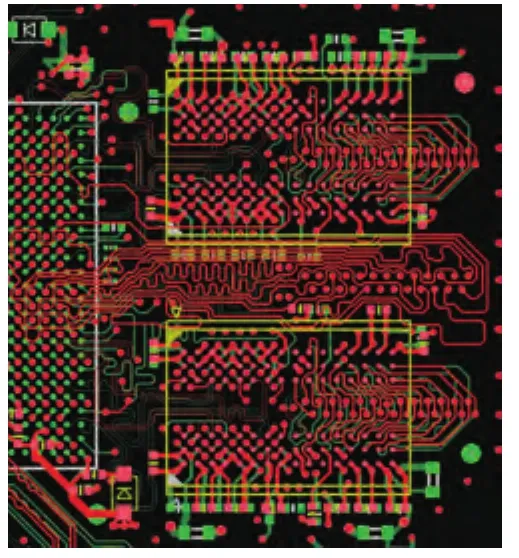

▲图8 4片DDR3放置

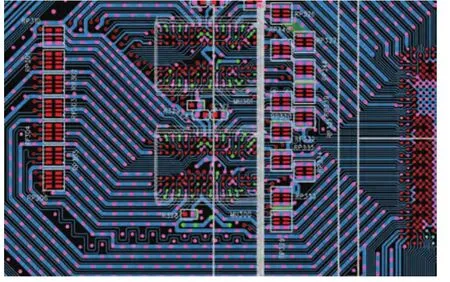

▲图9 DDR3在双面板中的设计效果图

这种情况和2片DDR3不同时钟线的走线方式类似,也采用T型走线方式走线。两组时钟信号将4片DDR也分成两组,将相同时钟信号的两片DDR3分别放置在靠近该时钟信号一侧,两片DDR3分别放在PCB的正面和背面的相同位置,另一组DDR放置在另一侧,同样按照上述方式放置,这样就变成了2组2片DDR3共用时钟线,地址线和控制线的T型走线方式。从CPU到两组DDR3的地址信号及控制信号的信号线长度和各自时钟信号等长。具体结构示意图参见图5,图6至图8是4片DDR3放置的PCB示意图,详细说明了如何在正面背面放置4片DDR3及完整放置的效果图。

从CPU到四片DDR3的地址/控制信号线走线长度为LAC,LAD,LAE及LAF,时钟信号线CLK1走线长度为LCLK1,时钟信号线CLK2走线长度为LCLK2,要求LAC=LAE=LCLK1,LAD=LAF=LCLK2。数据信号线DQ0-DQ15和数据选通信号DQS1等长,DQ16-DQ31和数据选通信号DQS2等长,数据信号线DQ32-DQ47和数据选通信号DQS3等长,DQ48-DQ63和数据选通信号DQS4等长。

DDR3在PCB设计中的地完整注意事项

DDR3在多层板设计中的地完整注意事项

如果DDR3采用多层板设计,需要注意,DDR3的等长信号线应尽量放在紧邻地层的内层走线,在DDR3区域正下方的地层一定要满足地平面完整这一要求,并且在对应位置的电源层只能放置DDR3的相关电源,不能有其他电源信号,DDR3信号线也只能在该区域内的信号层上布线,在空间上不能跨越电源分割区域。

DDR3在双面板设计中的地完整注意事项

在一些电脑主板或者数字电视的控制板中,控制成本是关键,因此,很多厂家都采用双面板实现DDR3布线,CPU芯片供应商也是尽可能地将芯片管脚优化,方便DDR3双面板布线。

在双面板布线中,DDR3的下方通常不可能有完整的地平面,这就要求通过将信号线包地处理,实现信号回流路径最短。通常2根信号线一组,两侧都要包地,且均匀打地过孔,如图9所示,粗线打过孔的就是地线,把信号线包在里面。

结语

在DDR3的PCB设计中,通常都应该遵循等长设计原则和地平面完整原则。只要能够遵循这两原则,并且遵循芯片设计手册的规定,一定能够设计出理想的PCB。