基于CPLD的编码器数据采集装置研究

陈 艳,李太平,朱江辉(中国飞行试验研究院,陕西西安,710089)

基于CPLD的编码器数据采集装置研究

陈 艳,李太平,朱江辉

(中国飞行试验研究院,陕西西安,710089)

摘要:绝对式光电编码器以其可靠性好、精度高的优良性能被广泛应用在高精度伺服系统位置检测中。本文以一种绝对式光电编码器为研究对象,介绍了光电编码器的原理,以CPLD为控制器,设计了装置的硬件电路,利用状态机,设计了装置的控制策略。实验结果表明,设计合理、可行。整个装置外围电路少、可靠性高。

关键词:CPLD,光电编码器,数据采集,状态机

0 引言

在精密伺服系统控制中,位置的反馈的好坏对于整个系统的性能起着至关重要的作用。由于绝对式光电编码器可靠性好、精度高,在伺服系统位置检测领域占据着一席之地。随着电子芯片技术的迅猛发展,复杂可编程逻辑器件(CPLD)以其可靠性高、处理逻辑能力强的特点广泛的应用于航天、航空等各个领域。本文以CPLD为控制器,设计了一种BiSS接口的绝对式光电编码器数据读入方法。

1 硬件设计

如图1所示,是数据读入设备的硬件整体架构。CPLD发送一个时钟刷,经调理电路,时钟转换成差分信号,激励光电编码器传回当前的位置数据。此位置数据符合BiSS接口规范,经调理电路,将数据转化为串行数据。CPLD接收数据,并转化为相应的并行数据。

图1 数据读入的整体架构

1.1光电编码器与BiSS接口

在高精度伺服系统中,绝对式光电编码器作为位置反馈装置,其精度高、可靠性好。本设计选用的是Hengstler公司的BiSS接口编码器AC36 。BiSS(Bidirectional Synchronous Serial Interface,简称BiSS)是一种标准的接口,用于控制器与光电编码器之间的数据传输。

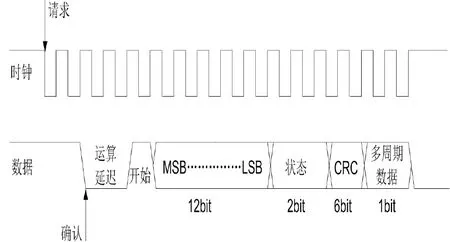

BiSS接口时序如图2所示。整个协议分为两个部分:时钟刷、数据。当光电编码器接收到时钟刷时,发出此时的位置数据。此数据遵守BiSS协议。即: 1位的起始位,12位的位置数据,2位状态位,6位CRC校验位与1位多周期数据(MCD)。

图2 BiSS接口时序

1.2CPLD

CPLD是整个设备的控制器。考虑到系统需要进行复杂的逻辑运算,选用CPLD——EPM7128AE。它发出时钟刷,接收串行的光电编码器数据,并将串行数据转化成并行数据,并进行校验。

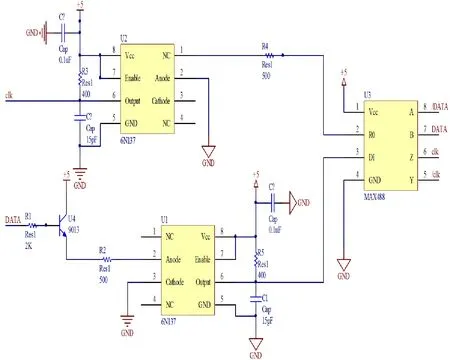

1.3信号调理电路

由于CPLD输出的为CMOS电平,而光电编码器需要TTL电平,因此需要电平转换电路。信号调理电路如图3所示。

信号调理电路将光电编码器与CPLD隔离,并将CPLD发出的时钟刷转化成差分信号,并将光电编码器反馈回的位置数据的差分信号转化为CPLD能过接收的CMOS电平信号。

图3 信号调理电路

2 程序设计

数据读入分为两个部分:时钟刷生成和串行数据处理。

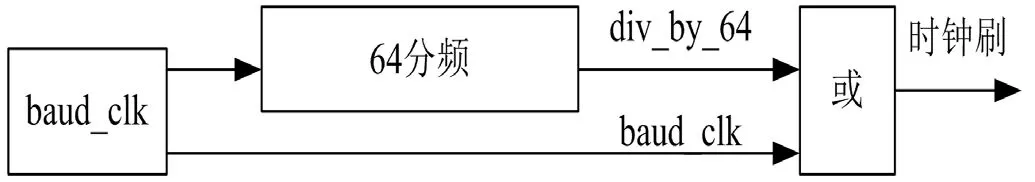

2.1时钟刷生成

为了得到如图2所示的时钟刷,将baud_clk时钟64分频,再将baud_clk与div_by_64相或,生成BiSS所需的时钟刷。其生成原理图如图4所示。

图4 时钟发送原理图

其中:baud_clk:时钟刷的波特率时钟

div_by_64:将baud_clk时钟64分频后时钟

2.2串行数据处理

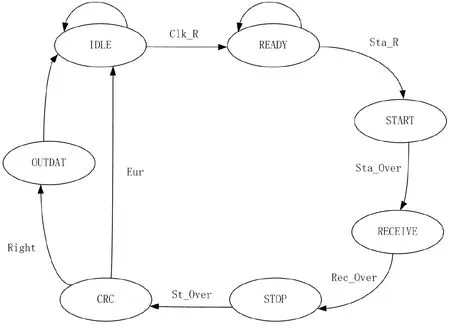

串行数据处理的状态机如图5所示。

图5 串行数据处理状态机

其中:

IDLE:空闲状态READY:准备状态

START:开始状态RECEIVE:数据接收状态

STOP:停止状态CRC:校验状态

OUTDAT:数据输出状态Clk_R:时钟刷到达信号

Sta_R:开始位到达信号Sta_Over:数据接收触发

Rec_Over:数据接收结束

St_Over:停止状态结束

Eur:错误信号

Right:正常信号

一般情况下,处于空闲状态,当CPLD发出时钟刷的下降沿,触发Clk_R信号,进入READY状态,并在此状态等待,当检测到串行数据的开始位,发出Sta_R信号,进入START状态,在一个波特率时钟后,进入RECEIVE状态,在此状态下,系统读入串行数据,并放入移位器,并用波特率时钟触发移位器移位,当数据接收状态完成时,进入STOP状态,检测到时钟刷结束,进入CRC状态,进行CRC校验,如果数据错误,进入IDLE状态,准备下次数据读入。如果数据正确,进入OUTDAT状态,此时将处理好的有效数据输出给DSP备用。

3 试验结果

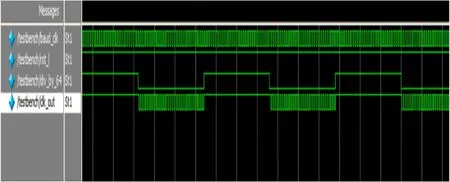

如图6所示,是BiSS时钟刷仿真时序。

在图6中,baud_clk为时钟输入信号,经过时钟发送的处理,生成时钟刷clk_out,从而激发光电编码器发出串行数据。

数据读入时序仿真图如图7所示。

在图7中,RXD是输入的无刷电机角位置串行数据,经过数据接收模块后,将其转化为12位并行数据addr。从而实现位置反馈的检测。

图6 BiSS时钟刷仿真时序

图7 数据接收模块时序仿真图

4 结束语

采用CPLD作为电路的控制器,设计了绝对式光电编码器的数据读入硬件电路。用状态机的方法设计了数据读入的程序。由于采用CPLD,系统能够并行处理数据。减小了位置反馈的延迟时间,简化了外围电路,提高了系统的可靠性。

参考文献

[1]高长清,林辉, 张辉. BiSS接口的光电编码器数据读出研究[J] 计算机测量与控制. 2009.5

[2]J. O. Krah,Software Resolver to Digital Converter for High Performance Servo Drives. PCIM Power Conversion Intelligent Motion, Nürnberg, June 1999,pp. 301-308.

[3] Hengstler, www.Hengstler.com

[4]Jens Onno Krah, Resource Optimized BiSS Master Interfacefor High Resolution Encoders, PCIM EUROPE 2006 • PROCEEDINGS

[5]Hengstler, ACURO – SSI / BiSS Technical Datasheet Interface

陈艳(1983-),女,新疆乌鲁木齐人,硕士,工程师,主要研究方向为机载试飞测试技术、电气系统试飞技术。

Research of Data Read Device for Optical encoder Based on CPLD

Chen Yan,Li Taiping,Zhu Jianghui

(Chinese Flight Test Establishment,Xi’an,China)

Abstract:As an important position feedback device,the absolute optical encoder is widely used in servo system.In the paper,a data read device based on CPLD is designed.Using the state machine,the control strategy of the data read device is designed.The experimental results show that the performance of the data read device is excellent.

Keywords:CPLD;photoelectric encoder;data acquisition;state machine

作者简介