一种全高清CMOS相机的设计与实现

许逸飞 樊超

摘要:为了获得高精度的图像,同时在满足微型化的要求下,本文使用CMOS图像传感器与FPGA构建了相机系统,本文在分析CMOS图像传感器MT9J003原理的基础上设计和实现一种基于FPGA的全高清CMOS相机,利用FPGA作为相机系统控制及系统时序生成的核心部件,最终输出HDMI全高清彩色视频。

关键词:图像传感器;CMOS相机;全高清;FPGA

中图分类号:TP18 文献标识码:A 文章编号:1009-3044(2016)03-0270-02

随着CMOS成像技术的不断发展, CMOS图像传感器工艺的不断进步,当前CMOS相机不断进步,CMOS图像传感器在功耗、成本以及集成度方面体现的优势越来越明显,CMOS图像传感器不断向主流和高端方向挺进[1]。CMOS图像传感器由于采用标准CMOS制造工艺,集成了A/D转换器以及底层驱动电路,使得CMOS图像传感器非常有利于FPAG对其像元进行操作,本文在分析Aptina公司CMOS图像传感器MT9J003原理的基础上设计和实现一种基于FPGA的全高清CMOS相机,相机通过HDMI接口输出全高清视频,分辨率可达到1920X1080(60Hz)。

1 系统结构

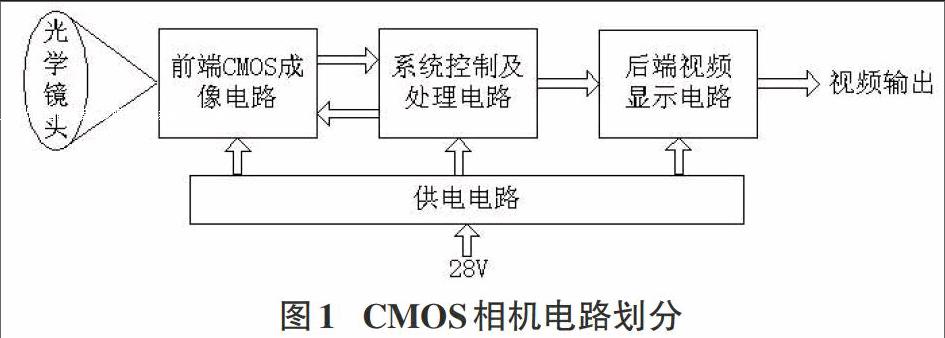

CMOS相机的系统结构如图所示,前端CMOS成像电路主要是图像传感器MT9J003的外围电路,保证MT9J003可以正常工作;系统控制及处理电路主要是对MT9J003的HiSPi[2]的数据进行串并转换同时实现MT9J003的功能配置以满足不同的应用需求;后端显示电路主要是根据相应的视频接口输出相应制式的视频格式;供电电路用于将输入系统的28V直流电转换成系统中其他电路所需的电压,以保证系统正常工作。按照系统的整体功能,CMOS相机可以分为以下几个部分:前端CMOS成像电路、系统控制及处理电路、后端视频显示电路、供电电路。

为了使相机输出全高清视频,MT9J003需工作在1080P模式下并且能通过HiSPi接口输出视频数据;为了使系统微型化,集成度更高,采用CMOS传感器中集成的A/D转换器,A/D的精度可达12bit,CMOS传感器将A/D转换器集成在每一个像素单元里,每一个像素单元输出的是数字信号,这样工作速度才能更快,功耗更低;对于1080p 60Hz的视频,每个像素点用12bit表示,其一副图像的大小为:1920X1080X12=24883200bit,1秒的数据量就是1424Mbps,因此系统处理的视频信号数据量非常大,所以需要采用FPGA等高速器件来进行系统控制及视频处理。

2 系统设计

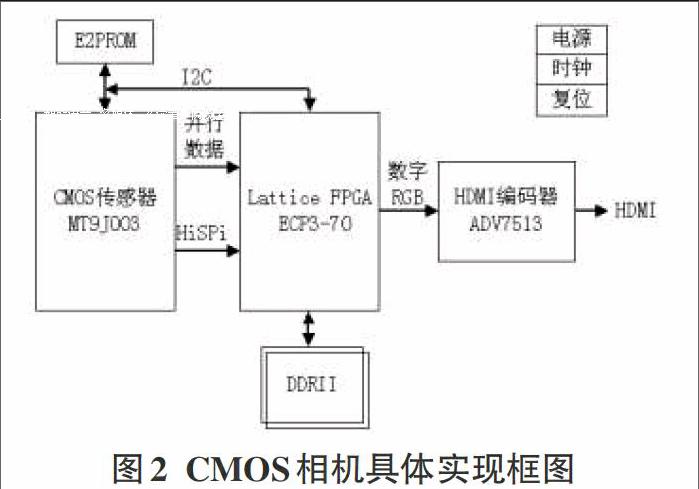

根据上述电路功能的划分,CMOS相机的具体实现框图如下:

CMOS相机共包括以下功能电路:

1)图像传感器电路,主要是图像传感器的外围电路;

2)串并转换电路,主要是将图像传感器输出的串行HiSPi数据转换成并行数据,采用Lattice公司的FPGA实现;

3)系统控制电路,可以通过E2PROM配置图像传感器工作在需要的模式;

4)视频处理电路,主要是将图像传感器输出的并行数据进行线性化、滤波、白平衡、Gamma校正、Bayer格式解析、色彩空间转换以及视频时序重组以满足后端视频输出电路的要求,采用DDRII作为视频缓存电路;

5)视频输出电路,主要由HDMI编码器组成以满足系统的视频输出接口要求;

6)复位、时钟及供电电路。

2.1 CMOS传感器电路

MT9J003是一款循序扫描以输出固定帧频数据流的数字图像传感器,它采用片上锁相环产生内部时序,输入时钟为6~48MHz,片上ADC分辨率为12bit[3]。传感器的核心是1000万像素的像素单元阵列,在时钟和控制电路的作用下,逐行对像素阵列进行读取数据和复位,而像元则在复位和读取数据的间隙感光成像。读取的数据经过模拟信号链进行排序,进而通过分辨率为12位的ADC,阵列中每个像素的值对应一个12位的数据输出,ADC输出的数据进而经过一系列的数字化处理后输出。MT9J003的图像数据是以循序扫描的方式读出的,有效图像数据被水平消隐和垂直消隐所包围,其中水平消隐和垂直消隐的数量可以由编程控制。MT9J003 的数据输出是由PIXCLK进行同步的,当LV为高电平时,一个像素的值在一个PIXCLK周期内通过12位的DOUT输出,像素时钟频率可以由传感器的主输入时钟和内部PLL配置决定。

2.2 串并转换

MT9J003要输出系统所要求的高清视频分辨率,需通过CMOS图像传感器的高速串行HiSPi接口。HiSPi接口是由Aptina公司开发的一种开放存取、可扩展的高速串行像素接口。为了使系统能输出正确的视频,必须将HiSPi接口的串行数据转换成并行数据,然后才能在FPGA里进行相关的视频处理操作。HiSPi的解串工作用Lattice公司的FPGA完成。

串并转换之后的信号包括时钟信号、数据信号、场同步信号及行同步信号。

2.3 视频处理电路

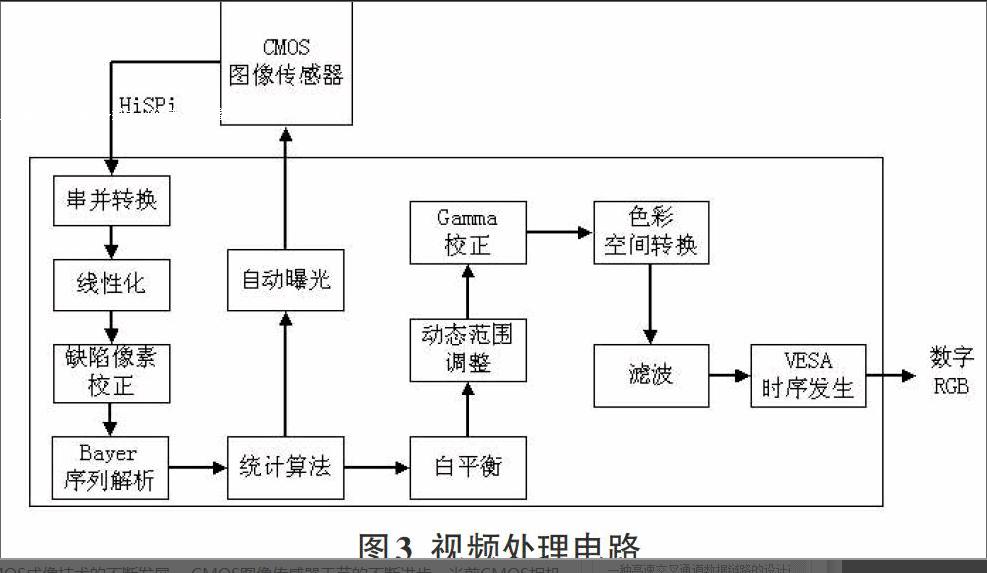

视频处理电路主要是对传感器输出的视频信号进行处理以满足系统对视频质量及视频接口的要求,该部分电路由Lattice公司的FPGA ECP3-70实现,该型FPGA具有丰富的图像处理IP库,通过使用外挂DDRII存储资源实现线性化、滤波、Bayer序列解析、校正、降噪、白平衡、色彩空间转换以及VESA时序生成等功能[4],具体实现如下图所示:

经过FPGA处理之后的视频已经是符合VESA制式的数字RGB信号,同时包括行同步信号、列同步信号以及数据有效信号,这一组数字信号送入到相应的HDMI编码器ADV7513即可输出1080p的HDMI视频。

3 结束语

本文介绍了一种CMOS图像传感器与FPGA构建的相机系统,该系统采用的高性能图像传感器配合FPGA实现的图像处理算法,最终能成功输出高质量的HDMI全高清视频,该系统由于采用了性能强大的FPGA,使得系统功能非常容易扩展[5],可以广泛应用在多功能显示系统、视景增强等领域。

参考文献:

[1] 刘新明.基于CMOS图像传感器的相机系统设计[D].中国科学院研究生院西安光学精密机械研究所.2009.

[2] High-Speed Serial Pixel (HiSPi) Interface Specification Data Sheet[Z]. www.aptina.com,2011.

[3] CMOS Digital Image Sensor MT9J003 Data Sheet[Z].www.aptina.com,2009.

[4] 张涛,王成龙,赵新宇.一种CMOS相机色彩还原算法[J].液晶与显示.2014,29(5).

[5] 刘美莹,王虎等.FPGA的大面阵CMOS相机系统的设计[J].红外与激光工程.2013,(Z2).