一种机载信号处理单元时钟电路的设计与实现

孟博+徐玉杰+王晨博

摘要:该文详细介绍了机载信号处理单元时钟电路的设计方案,分别从时钟需求、器件选型、信号终端匹配和PCB等方面进行了设计,保证了机载信号处理单元时钟电路的正确性、安全性和可靠性。测试结果和工程应用表明,该时钟电路各项指标均满足系统要求。

关键词:信号处理单元;终端匹配;PCB

中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2016)04-0224-03

The Design and Implement of Clock Circuit in

Avionic Signal Processing Unit

MENG Bo, XU Yu-jie, WANG Chen-bo

(Xian Aeronautics Computing Technique Research Institute, AVIC, Xian 710065, China)

Abstract:In this paper, a design scheme of the clock circuit in Avionic Signal Processing Unit is presented including clock requirement, component selection, signal terminal matching and PCB respectively, which ensures the accuracy, safety and reliability of clock circuit in Signal Processing Unit. Test results and real-world applications show that the performance of the clock circuit meets the system requirements.

Key words: signal processing unit; terminal matching; PCB

1 概述

在机载设备电子系统中,时钟电路一直是非常重要的组成部分。随着电路复杂度和时钟频率越来越高,机载电子设备单位面积PCB上的器件密度和信号之间的串扰也越来越大,机载设备要求具有高可靠性、高安全性。产品时钟电路设计的好坏直接影响整个机载电子产品的功能性能[1]。

针对此问题,本文就机载信号处理单元时钟电路设计在充分考虑时钟需求、器件选型、终端匹配、PCB设计等因素下,提出一种满足机载信号处理单元的时钟电路实现方法,保证了机载设备时钟电路的稳定性和可靠性。

2 硬件电路设计

2.1 需求分析

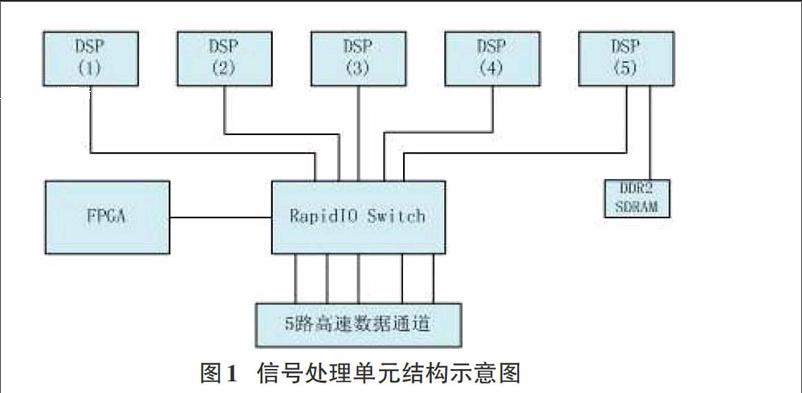

信号处理单元负责主要完成光电任务的处理工作,产品具备独立的5通道FC传输和信号处理通道,前4路完成与前端传感器点-点连接的信号的处理任务。本文论述的信号处理单元采用5片DSP处理器TMS320C6455和1片FPGA可编程器件XC5VSX240T,主要实现DSP信号处理功能、FPGA信号预处理和Rapid IO交换互连等功能,信号处理单元结构示意图如图1所示。

图1中,前4路DSP处理器各对应1路前端信号处理通道,第5路DSP处理器负责拼接功能,配置大容量DDR2 SDRAM存储器,用于数据缓存。可编程器件FPGA则用来实现信号的预处理和接口控制逻辑。最后通过RapidIO Switch交换互连协议,实现5路高速数据通道。

2.1.1 DSP时钟需求

DSP (TMS320C6455)需要3种时钟输入源。其中,CLKIN1提供DSP内部PLL1的源时钟,主要用于产生DSP工作主频。CLKIN2提供DSP内部PLL2的源时钟,主要用于产生DDR2控制器的工作时钟。RIOCLK为差分时钟,提供DSP上RapidIO接口的输入基准时钟。DSP各时钟的输入要求如表1所示。

按照要求,设计中DSP的CLKIN1输入50MHz的基准时钟,通过PLL1的控制寄存器产生20倍频,产生DSP的工作主频1GHz时钟;DSP的CLKIN2输入20MHz的基准时钟,通过PLL2的控制寄存器产生10倍频,产生DSP DDR2控制器的200MHz接口工作时钟;DSP的RIOCLK时钟输入156.25MHz的差分时钟,通过RapidIO控制寄存器的设置,可以配置RapidIO接口工作速率为1.25Gbps、2.5Gbps和3.125Gbps。

2.1.2 FPGA时钟需求

FPGA(XC5VSX240T)的时钟需求有两部分,一是FPGA实现存储控制器的基准时钟。设计中,通过FPGA的GCLK全局引脚输入100MHz的单端时钟,用于产生FPGA中DDR2 SDRAM和QDRII SDRAM控制器的工作时钟。同时,提供50MHz和20MHz的备份时钟。二是通过IP核实现2路RapidIO接口,采用FPGA相邻的4个GTP_DUAL Tile(MGT112,MGT 114,MGT 116,MGT 120)来实现。FPGA各时钟的输入要求如表2所示。

2.2 设计方案

根据DSP和FPGA的不同需求,信号处理单元时钟电路设计实现方案如图2所示。

通过50MHz晶振产生频率为50MHz、周期20ns的时钟信号,经过时钟驱动器驱动后输出10路时钟信号分别连接到TMS320C6455 DSP的CLKIN1时钟管脚和FPGA的GCLK管脚,用于产生DSP的内核工作时钟和FPGA的工作时钟。

通过20MHz晶振产生频率为20MHz、周期50ns的时钟信号,经过时钟驱动器驱动后输出10路时钟信号分别连接到TMS320C6455 DSP的CLKIN2时钟管脚和FPGA的GCLK管脚,用于设置DSP的DDR2接口时钟,作为FPGA工作的备份时钟。

通过100MHz晶振产生频率为100MHz、周期10ns的时钟信号,经过时钟驱动器驱动后输出10路时钟信号连接到TMS320C6455 DSP的AECLKIN时钟管脚和FPGA的GCLK管脚,提供DSP EMIF的接口工作时钟和FPGA工作的备份时钟。

通过156.25MHz差分晶振产生频率为156.25MHz 、周期为6.4ns的差分时钟信号,经过差分时钟驱动器驱动后分别输出到5片TMS320C6455的RIOCLK和[RIOCLK]时钟管脚, 提供DSP RapidIO接口的工作时钟。

2.3 器件选型

由于TMS320C6455对于输入时钟的要求比较严格,要求外部输入时钟CLKIN1和CLKIN2的上升沿、下降沿时间均小于1.2ns。本设计中选用CDCVF2310作为时钟驱动器,该器件是1路输入10路输出,输出最大上升沿、下降沿时间[tr]和[tf]为0.8ns,输入输出延迟[tPLH]和[tPHL]最小时间和最大时间分别为1.3ns和2.8ns,工作温度范围为-40温到850,工作电压的区间为2.3V到3.6V,工作的最大时钟频率为200MHz,可满足TMS320C6455的需要。CDCVF2310驱动器电气指标如图3所示。

差分时钟驱动器采用SN65LVDS108,电路示意图如图4所示。该器件要求输入LVDS的差分时钟输出8组LVDS差分时钟,传输延迟小于4.7ns,输出最大上升沿、下降沿时间为0.8ns,工作的最大时钟频率为400MHz,性能满足设计要求。设计中配置5路提供DSP的工作时钟。

模块上FPGA采用RapidIO IP核实现RapidIO协议,对GTX的时钟输入有严格的要求。设计中,采用LV7744DEV-125M晶振产生125MHz的差分时钟输出,输出到FPGA的GTX时钟管脚,提供FPGA RapdiIO接口2.5Gbps的工作时钟。

设计中20MHz、50MHz和100MHz晶振据选用SCX011B系列晶振,该晶振标称频率范围1MHz到125MHz,频率温度稳定度为[±]75ppm,占空比典型值为50%,各项参数均满足系统设计要求。156.25MHz差分晶振选用LV7744DEV系列晶振。

2.4 信号终端匹配

由于信号处理单元中的时钟信号种类较多、频率较高,因此在设计之初要考虑时钟信号完整性,本设计采用了终端匹配技术[2][3]。

2.4.1 串联电阻方式

在驱动器末端加载一个串联电阻Rs,确保信号不会在源端发射回来,链路中特性阻抗为Z0 ,驱动设备的输出阻抗为R0 ,匹配设计的规则为Z0 =Rs+ R0,串联电阻方式如图5所示。这种串联电阻的方式,保证了信号的完整性传输,这种方式的优点在串联的电阻很小,功耗很低,有很好的直流噪声容限,缺点在于使得时钟信号的延迟增大。

2.4.2 并联RC方式

并联RC方式是在负载端并联一个RC网络,在TTL和CMOS电路经常使用,并联RC方式如图6所示。其中,并联网络中的R值须与电路阻值Z0相等,C值通常选择比较谨慎,其要求能够吸收电波的能量,又不至于加大信号的上升时间,经验选择小于50pf的电容。

综合考虑,在信号线发送端利用源端串接匹配电阻的方法来吸收反射信号,由于传输线的特征阻抗控制为50欧, 因此设计中选用的是22欧的匹配电阻。

2.5 PCB设计

信号处理模块时钟网络较复杂,因此在PCB设计要充分考虑信号完整性问题[4] [5] [6]。本设计在PCB布局布线主要采取的措施主要包括:

1) 要求整个模块的特征阻抗为50欧;

2) 晶振输出的时钟信号走线尽量短,远离其他信号线;

3) 源端串阻靠近晶振放置;晶振输出时钟信号参考层为地平面,不能跨分割平面;

4) 时钟驱动器输出的时钟信号尽量短,远离其他信号线,源端串阻靠近;

5) 钟驱动器放置;时钟驱动器输出时钟信号参考层为地平面,不能跨分割平面;

6) 时钟线尽量少打孔,保持阻抗连续性,与其他线的间距保持3W或以上。

3 测试验证

在实验室搭建测试平台对机载信号处理单元的时钟电路进行测试验证。信号处理模块的误码率能直接反应时钟电路设计的性能。创建测试模块误码率的工程文件ibert.bit,利用Chipscope进行误码率测试。误码率测试结果如图7所示,该信号处理单元共有5路高速数据通道,选择其中两路进行测试。发送数据速率为2.125Gbps,在连续测试8分钟后,接收端接收到的数据Bit累积达到1.059E012,发生错误的数据位0,误码率下降到9.441E-013,并且随着时间的延长,误码率会一直下降。

测试结果表明,本文介绍的信号处理单元时钟电路设计,完全满足该机载信号处理单元的系统要求。

4结论

本文从机载设备时钟电路设计要求出发,详细介绍了一种机载信号处理单元时钟电路的器件选型、终端匹配、PCB设计等方面的详细设计,给出了机载信号处理模块时钟电路的实现方法。实验测试结果表明,该时钟电路各项指标均符合系统要求,现已在实际应用中得到验证,并对其他机载设备的电路设计有一定的指导作用。

参考文献:

[1] 江浩,柴孟阳,刘银年.基于多FPGA的高光谱图像数据采集系统时钟设计[J]. 科学技术与工程,2013,13(15):4408-4413.

[2] 陈倩.基于高速时钟电路终端的信号完整性分析[J].电讯技术,2005,10(4):185-188.

[3] 崔迎炜,张晓林.软件无线电中的高速设计技术[J].北京航空航天大学学报,2004,30(1).

[4] 齐志强.高速PCB设计经验与体会[J].电子设计工程,2011,19(16):141-143.

[5] 周润景,景晓松.高速电路板设计与仿真[M].北京:电子工业出版社,2008.

[6] 周芸,柯敏毅.高速PCB板设计研究[J].通信电源技术,2008,25(2):23-26.