SOI基外延纯Ge材料的生长及表征

蔡志猛,陈荔群(.厦门华厦学院,福建厦门,36000;.集美大学诚毅学院,福建厦门,360)

SOI基外延纯Ge材料的生长及表征

蔡志猛1,陈荔群2

(1.厦门华厦学院,福建厦门,361000;2.集美大学诚毅学院,福建厦门,361021)

摘要:利用超高真空化学气相沉积系统采用低温-高温两步法外延Ge材料。我们先在低温下生长硅锗作为过渡缓冲层利用其界面应力限制位错的传播,然后在低温下生长的纯锗层,接着高温生长纯锗,最后在SOI基上成功的外延出了高质量的纯锗层,测试结果表明厚锗层的晶体生长质量很好,芯片表面也很平整,表面粗糙度5.5nm。

关键词:超高真空化学气相沉积系统;外延;锗

0 引言

Ge 材料由于自身在电子和空穴迁移率及禁带宽度方面都比Si材料更优越同时其晶格常数同III-V族半导体材料相匹配等优点,近年来一直是研究的热点。G锗材料由于与硅工艺相兼容,被大量应用在近红外光电方面。另一方面,由于硅锗间高达4.2%的晶格失配,直接在硅材料上外延锗材料将会使得失配位错过多,无法得到平整的表面。同时过高的位错密度将会增加得器件的漏电流,导致元件性能下降; 凹凸不平的表面也将得器件加工工艺难度加大。要外延出高质量的Ge材料,关键是要寻找到如何减少位错密度和降低表面粗糙度的方法。文献上已经有诸多关于在硅材料上外延出高质量的锗层的报道。在这些报道中组分渐变硅锗buffer层技术,工艺比较复杂而且生长的材料过渡层明显偏厚, 对于小尺寸的集成器件研制不太适合; 相对的低温锗缓冲层的技术工艺较为简单,该方法以较薄的过渡层和较为平整的表面,成为目前硅基锗材料生长的主要方法。不过基于低温锗缓冲层外延的硅基锗材料仍然存在较高的位错密度, 需要进行循环热退火过程进一步降低位错密度。

SOI(silicon- on- insulator)材料结构是底层Si上一薄层氧化硅最外层是高质量的Si材料。由于氧化硅的存在,将器件与衬底隔离开来, 使得在器件性能有很大的提升,首先它能使寄生电容较小,运行速度得以提高, SOI 器件的运行速度比体硅材料提高了20- 35%;此外随着寄生电容的减小,漏电也降低了功耗自然也就下降了, SOI 器件功耗可减小35到70%。此外,这类型的器件能够抑制来自衬底的脉冲电流干扰, 降低软错误的发生。另外由于与现有硅工艺相兼容,因此工艺简单。我们在研究硅基外延纯锗的基础上,不断研究在SOI衬底上外延高质量的纯锗的方法。

1 Si实验及表征

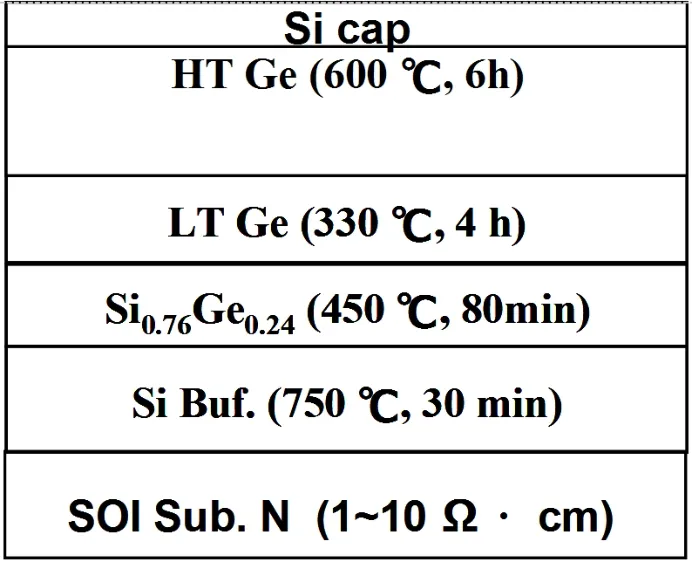

统中制备的。本底真空可以达到3×10-8Pa,实验中利用原位反射高能电子衍射仪(RHEED)全程监控。生长所用气源采用的是高纯的乙硅烷(Si2H6)和锗烷(GeH4)。实验采用的芯片为4英才N型SOI晶向〈100〉衬底电阻率为1~10 Ω·cm。实验前将芯片经过标准RCA清洗后传入生长室,将衬底缓慢加热到850℃保持该温度30分钟,目的是为了去掉衬底的本征氧化层得到清洁的生长表面,整个过程真空度维持在5×10-6Pa以下。脱氧完成后温度调整到750℃生长300 nm的硅缓冲层;接着将温度降低到450℃生长80分钟Si1-xGex缓冲层,紧接着温度降低到330摄氏度长4小时低温锗层。低温锗层生长完后,温度调整到600℃,高温6小时生长锗层。实验最后在最外层覆盖一薄层的硅盖帽层,材料结构如图1所示。

图1 SOI基外延锗材料结构图

图2是生长材料的XRD曲线,扫描模式是ω-2θ,扫描晶面为〈004〉的对称面。由该图我们可以观察到硅衬底峰,低温硅锗层和外延锗层的衍射峰。外延锗层衍射峰的半高宽是310 arcsec,锗的衍射峰的峰位与相比于理论上的锗的衍射峰峰位偏右,表明外延的锗层存在张应变。分析是由于锗的热膨胀系数比硅大,经生长时的高温冷却到室温过程中,锗层中产生了张应力。

我们的材料是在冷壁超高真空化学气相沉积(UHV/CVD)系下面我们以XRD曲线分析材料外延层受到的应力,材料的晶格常数垂直方向分量可表示为:

其中是图2所示XRD曲线峰值位置时的角度,λ采用的是Cu的kα1线大小0.154 nm。根据XRD测量曲线可计算出,由体锗的晶格常数公式,

最后由驰豫度关系式

可以计算出我们的外延生长的材料驰豫度为103.8%。其水平方向受到了张应力的影响,张应力的关系式为

计算得出张应力等于0.24%,应力的存在将会影响到能带的结构,使得带隙大小发生变化。另外,轻重空穴直接带隙和应力间又满足如下关系式:

图3是原子力显微镜扫描出来的外延锗层表面形貌,扫描模式为轻敲模式,扫描大小区域为10 µm ×10 µm,Z方向大小40nm。从图中可以看出表面平整,质地均匀起伏不大,实验测得在不同区域样品的表面粗糙度为5.5nm。

图2 SOI基外延锗层〈004〉 面XRD曲线

图3 SOI基外延锗层表面AFM扫描图

2 总结与讨论

采用超高真空化学气相沉积设备,以高纯乙硅烷和锗烷作为气源,以锗硅和低温锗作为缓冲层,在SOI衬底上成功外延出了高质量的纯锗层。原子力显微镜表征结果显示厚锗层的晶体生长质量很好,芯片表面也很平整,表面粗糙度5.5nm。计算得出锗层受到大约为0.2%的张应力,这导致锗的直接带隙降到0.78eV,Ge的吸收系数因此得到了增强,,截止波长向延伸外,光响应波长扩大到1600nm以上。该材料将为Si 基集成高速电子和光电子器件提供重要的平台。

参考文献

[1]S.Luryi,A.Kastalsky,J.C.Bean.New infrared detector on a silicon chip [J].IEEE Transactions On electron Devices, 1984, 31(9):1135-1139.

[2]G.L.Luo,T.-H.Yang,E.Y.Chang,et al.Growth of high-quality Ge epitaxial layers on Si (100)[J].Jpn.J. Appl.Phys.,2003,42: 517–519.

[3]H.C.Luan,D.R.Lim,K.K.Lee,et al.High-quality Ge epilayers on Si with low threading-dislocation densities [J].Appl.Phys. Lett.,1999,75(19):2909-2911.

[4]Y.Ishikawa,et al.,Strain-induced band gap shrinkage in Ge grown on Si substrate.Applied Physics Letters, 2003. 82(13):p.2044-2046.

[5]Y.Ishikawa.,et al.,Strain-induced enhancement of nearinfrared absorption in Ge epitaxial layers grown on Si substrate.Journal of Applied Physics,2005. 98(1):p.013501.

[6]J.M.Hartmann,A.Abbadie,Reduced pressure–chemical vapor deposition of Ge thick layers on Si.001 for 1.3–1.55-mm photodetection[J].JOURNAL OF APPLIED PHYSICS,2004.95(10):5905-5913.

[7]Y.Ishikawa,et al.,Strain-induced band gap shrinkage in Ge grown on Si substrate.Applied Physics Letters,2003.82(

13):p.2044-2046.

[8]Y.Ishikawa.,et al.,Strain-induced enhancement of nearinfrared absorption in Ge epitaxial layers grown on Si substrate[J].Journal of Applied Physics,2005. 98(1):p.013501.

[9]余金中,锗硅的性质[M],2002年9月第一版,国防工业出版社,p79.

[10]J.F.Liu,D.D.Cannon,K.Wada,et al.Tensile strained Ge p-i-n photodetectors on Si platform for C and L band telecommunications[J].Appl.Phys.Lett.,2005, 87: 011110-1-3.

[11]D.D.Cannon,J.F.Liu,Y.Ishikawa,et al.Tensile strained epitaxial Ge films on Si(100)substrates with potential application in L-band telecommunications[J].Appl.Phys. Lett.,2004.84(6):906-908 .

Growth and characterization of SOI based epitaxial pure Ge materials

Cai Zhimeng1,Chen Liqun2

(1.Xiaman Huaxia University,Fujian Xiamen,361000;

2.Jimei University Fujian Xiamen,361021,Chengyi College)

Abstract:The tensile stained Ge grown on a silicon-on-insulator(SOI)substrate were fabricated successfully by ultra-high chemical wapor deposition.Firsty, a thin relaxed low-temperature SiGe buffer was grown followed by a low-temperature Ge layer,then,a high temperature Ge layer was grown at 600℃.High crystal quality and low surface roughness of 0.55nm of the Ge layer are characterized.

Keywords:UHV-CVD;Epitaxy;Ge

通讯作者:蔡志猛

*基金项目:福建省中青年教师教育科研项目(JA15654)