基于FPGA的海杂波模拟器设计与实现

严纪珊

(上海儿童医学中心,上海 200127)

基于FPGA的海杂波模拟器设计与实现

严纪珊

(上海儿童医学中心,上海 200127)

摘要:给出了海杂波模拟器的设计和实现方案。该模拟器采用软硬件相结合的方式,能够实时地完成实际应用场景的杂波模拟。采用FPGA进行设计与调试,经过测试,所模拟产生的杂波与实测杂波波形特征相似,所模拟出的波形与实际测量的真实波形功率谱特性结果一致。为雷达海杂波的模拟和工程实现提供了可行的方法。

关键词:海杂波;现场可编程门阵列;零记忆非线性;模拟器

现场可编程门阵列(Field Programmable Gate Array,FPGA)是在原有的PAL、GAL和CPLD等可编程器件基础上进一步发展的产物[1]。作为专用集成电路(ASIC)领域中的一种半定制电路,它的出现既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。以Verilog或VHDL的硬件描述语言为基础的电路设计,可以在合理的综合布局后,在FPGA上进行测试,这是现阶段主流的开发测试方法,并使得采用数字设备来模拟自然信号成为可能。雷达技术的发展对于装备制造行业至关重要,传统的实地测量调试雷达技术设计研发方式周期长、成本高和效果差,而通过采用电子设备对信号进行模拟的方法,不仅可以缩短雷达设计和研发的周期,而且可以大幅度降低研发成本。

随着数字模拟技术的飞速发展,许多雷达信号都能够采用数字信号进行模拟,数字模拟的方法已经成为了雷达系统设计研发中不可缺少的组成部分[2-3]。在雷达的研发过程中,可以模拟的波形信号主要包括辐射源信号、干扰信号、杂波信号和回波信号。其中杂波信号的模拟在整个雷达研发过程中意义重大,杂波信号的模拟质量直接影响到雷达系统的研发。杂波信号模拟模型的精确度、兼容性和灵活度是衡量整个雷达信号模拟系统好坏的重要参数。本文在此基础上,对海洋杂波实际情况进行系统性模拟,研究如何基于FPGA平台实时、高保真度地产生海杂波数据。

1系统总体设计

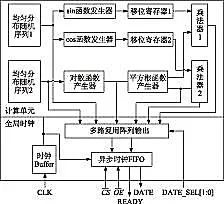

本文围绕海杂波回波信号的生成及在整个模拟系统中的实现而展开,以软硬件结合为设计思路,通过计算机配置加FPGA主运算的结构,充分发挥了软件的灵活性和硬件的实时性。独立地封装各功能子模块,使子模块之间通过接口协议协调工作,具有良好的通用性、兼容性及可扩充性。模拟器结构设计如图1所示。

图1 模拟器总体设计图

模拟器包括2个部分:上位机(或工作站)和专用硬件处理模块。上位机辅助硬件处理模块主要完成参数配置、数据预处理以及对硬件处理模块的控制;硬件处理模块是该模拟器的核心,在所涉及的硬件平台上完成对各种信号的模拟,以及数据的存储、传输等。

该模拟器仿真产生海杂波回波信号的流程如图2所示。

图2 海杂波回波信号产生流程

2系统硬件设计

2.1实现原理图

本文研究所使用的硬件设备为Xilinx公司XC5VLX50T型号的FPGA[4],具体的海杂波模拟器结构框图如图3所示。

图3 杂波回波信号产生的硬件原理图

海杂波回波信号在FPGA上产生的流程如下:1)上位机预先产生幅度归一化的发射信号,该发射信号储存在硬件上并周期性循环调用;2)在设定的1个脉冲波形周期内,通过对海底杂波实际测量,根据测量天线波束范围内的杂波分布情况,确定实际杂波与雷达波的几何关系;3)通过对函数进行调试,将原始波形模拟成天线接收到海杂波后的波形;4)FPGA根据这些调试函数估算不同实际实物模型的物理参数,如礁石珊瑚等形状和尺寸数据;5)对这些代表着不同实物的参数进行筛选切分,按照顺序进行编号;6)上位机按照随机数列作为一个周期内分布模型的调制函数,在模拟海杂波时对原始波形进行调制;7)在下一个周期时,上位机同样产生幅度归一化的发射信号,经过FPGA上对应函数的调制之后形成的波形,就是被合成的模拟海杂波回波信号。

2.2硬件指标

实现海杂波模拟器的XC5VLX50T设备采用的是65 nm工艺,6输入的查找表(LUT),跳线分布经过简化改进,RAM为64位分布式结构,内部时钟550 MHz;处理器采用3.6GFLOPS处理能力的ADSP-TS201S处理器,卡片储存容量为24 MB,集成14通道DMA控制器。每片处理器可以提供256 MB内存;根节点处理器提供16 MB闪存;同时在FPGA硬件上搭载36 bit×2 MB的储存器,完成整个硬件结构数据信息的存储和读取工作。这样的硬件配置能够极大限度地提升模拟海杂波的复杂性和真实性,从而大幅度提高模拟的效果。

3海杂波信号在FPGA中的实现

对杂波进行模拟,首先要选取杂波调用模型。采用随机方法所获得的数据模型不遵循高斯分布情况。常见的非高斯概率幅度密度分布大体可以分成4种常见模型,针对不同模型适用于不同的场景模拟情况,虽然不能对所有海杂波的全部状态进行模拟,但可以对某种海杂波的某种状态进行较好模拟。

3.1零记忆非线性法产生杂波原理

模拟时采用零记忆非线性(ZMNL)法进行中杂波信号产生设计[5],这种模拟算法的基本思想是先用系统生成高斯随机序列,然后通过特定的方式进行变换,最终得到一个非高斯随机序列。这种变化的优点是概念清晰,模拟者只要在输出和输入的波形中找到波形所对应的函数的变化过程,便可以进行相应的模拟。由于这种变化产生方法所涉及到的相关技术都比较常见,而模拟高斯随机序列调用函数调制波形的速度快,准确度高;因此,这种模拟算法在雷达杂波仿真模型中运用范围较大。整个波形的调试逻辑原理图如图4所示。

图4ZMNL的原理图

3.2CORDIC算法[6-7]的FPGA实现

采用ZMNL法来产生杂波序列,其中非线性变换主要是通过坐标旋转数字计算方法(CORDIC算法)来完成。此算法的基本思路为:当需要对平面矢量进行旋转时,采用坐标的方式将角度进行分解,并采用预设的基本角度进行组合逼近模拟,通过依照以基本角大小为变化基准单位的数次旋转,对数量并没有限制,但是必须是以基本角为旋转标准。该算法的优势在于每次原始数据的变化都是以基本角度为参考的变换,也就是说,每次对于原始数据的加工仅仅是简单的位移和加法运算,而整个模型的加工方式仅仅是通过加减法运算的方式来实现一个复杂的变化,这样的函数算法设计能够很大程度地提升整个硬件系统的运行优势,从性能上大幅提升模型的运行效果。

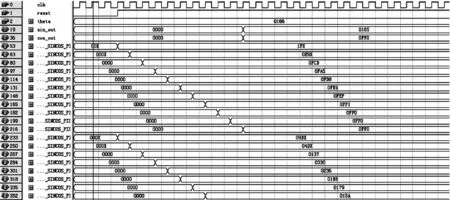

Altera公司设计了一款嵌入在自身软件开发环境QUARTUS II上的逻辑验证工具(简称SignalTap II)。SignalTap II在调试时,占用的逻辑资源极少,相当于将一个类似于示波器的分析仪嵌入在FPGA内部,然后通过检查那些设计者感兴趣的信号来了解系统的具体工作情况。在成功调试系统后,就可直接去掉嵌入式逻辑分析仪,并且对系统的工作不会产生任何影响。本文采用EP2S60F1020C4进行仿真,其中数据位数为16 bit,小数位为12 bit。模拟仿真效果图如图5所示。当原始波形经过12个时钟周期调制后,将调至后的结果进行输出,输入系统的原始波形为theta=16’h0166(50),经过调制后的波形输出正弦值为sin_out=16’h0166(0.087 4),余弦值为cos_out=16’h0FF0(0.996 1)。

图5 CORDIC算法仿真结果图

3.3高斯随机序列的FPGA实现

采用BOX-MULLER[8]变换法来实现高斯随机序列,BOX-MULLER变换法是一种比较常用的用于产生高精度高斯随机序列的变化方法,具体原理如下:

式中,u1、u2分别是大小在[0,1]的区间中均匀分布的随机序列;v1、v2分别是经过简单变形产生的正弦和余弦两路高斯随机序列,其模型逻辑产生原理图如图6所示。

图6 BOX-MULLER法高斯随机序列逻辑原理图

采用Modelsim6.2对高斯随机序列进行模拟仿真,具体效果如图7所示。

图7 高斯随机序列的仿真结果

4模拟结果及分析

4.1仿真参数设置

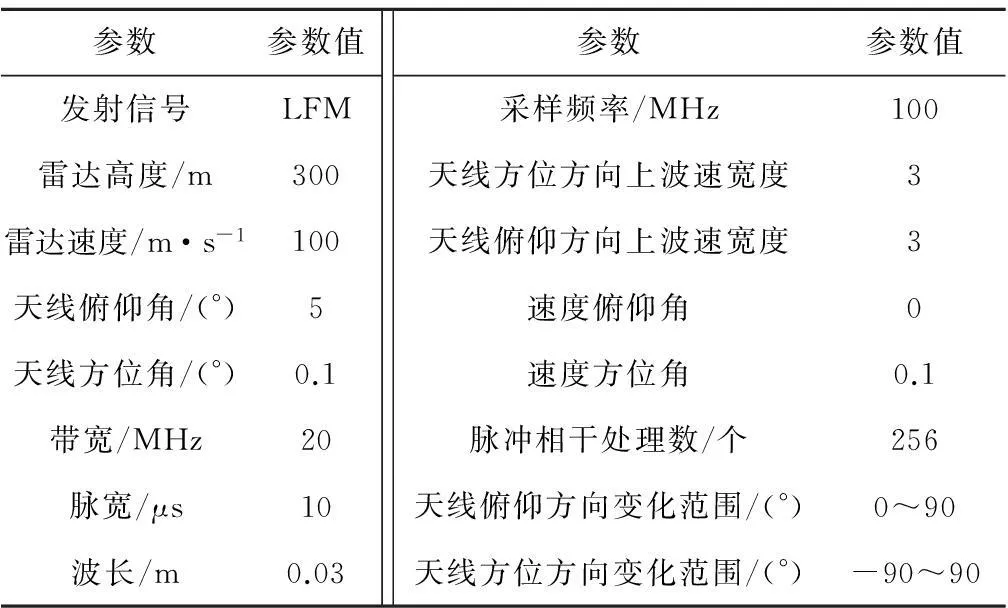

结合本文研究情况,对本系统所要仿真的参数进行设置,具体数值见表1。

表1 仿真实验条件参数设置

4.2实验结果

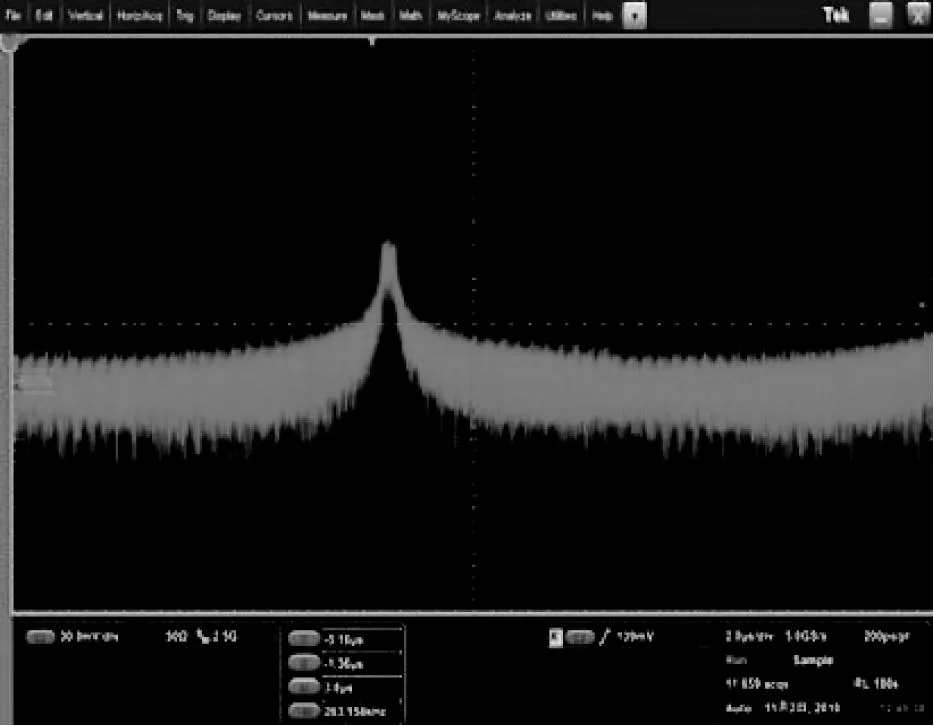

在本文设计中,雷达信号模拟器所选用的杂波模拟单元适用入射余角为30°~50°[9],模拟15级海情,模拟发射信号为单脉冲雷达信号[10]。海杂波回波信号频谱图如图8所示,雷达信号模拟输出的杂波回波信号如图9所示,产生的海杂波回波信号与MATLAB软件仿真结果一致,说明产生的海杂波回波信号是正确的。

图8 海杂波回波信号频谱图

图9 模拟海杂波回波信号频谱图

5结语

本文提出了基于FPGA海杂波模拟器的设计方案,实现了在具体场景下杂波回波信号的模拟。测试结果表明,该信号模拟器达到了设计要求,可以满足当前环境下的目标信号模拟,同时为同类雷达信号模拟器中的杂波产生方法研究提供参考。

参考文献

[1] 王胜. 动态目标雷达回波实时模拟技术及应用[D].长沙:国防科学技术大学, 2011.

[2] 夏阳. 海杂波建模仿真技术研究与FPGA实现[D].长沙:国防科学技术大学, 2011.

[3] Ward K D, Watts S. Use of sea clutter models in radar design and development[J]. IET Radar Sonar Navig., 2010, 4(2):146-157.

[4] 谈世哲,李建,管殿柱.基于Xilinx ISE的FPGA/CPLD设计与应用[M].北京:电子工业出版社, 2009.

[5] 杨凤凤,周智敏.基于ZMNL 法的雷达杂波仿真[J].现代雷达, 2003, 25(9):23-25.

[6] Volder J E. The CORDIC trigonometric computing technique[J]. IEE Transactions on Electronic Comput., 1959(8):330-334.

[7] Andraka R. A survey of CORDIC algorithm for FPGA based computers[C]//Proceeding of the 1998 ACM/SIGDA sixth international symposium on field programmable gate arrays. New York: ACM, 1998.

[8] Lee D U, Villasenor J D. A hardware Gaussian noise generator using the Box-Muller method and its error analysis[J]. IEEE Transaction on Computers, 2006, 55(6):659-671.

[9] 李海涛,张刚,张晓光. 一种基于FPGA的海杂波产生器设计[J]. 海军航空工程学院学报, 2010(6): 621-623.

[10] 李芾. 基于实测海杂波数据的统计特性分析[D]. 西安:西安电子科技大学,2013.

责任编辑郑练

Design and Realization of Sea Clutter Simulator based on FPGA

YAN Jishan

(Shanghai Children’s Medical Center, Shanghai 200127, China)

Abstract:Present a sea clutter simulator design and implementation. The simulator uses software and hardware, and can generate sea clutter in real time when given the practical application of the radar signal simulator scenarios. The generated clutter can satisfy the power spectrum characteristic requirement. The measured results and simulation match perfectly. Thus a viable method for simulation and engineering realization of the sea clutter generation is provided.

Key words:sea clutter, FPGA, ZMNL, simulator

中图分类号:TN 959.7

文献标志码:A

收稿日期:2015-11-17

作者简介:严纪珊(1983-),男,中级IT工程师,大学本科,主要从事计算机科学与技术等方面的研究。