基于FPGA的工业实时通信模块分析

黄昊

摘 要:在传统工业实时通信模块的设计中,采用的多是PLC编程的方式,以CAN總线作为扩展总线,其通信速率无法满足工业现场大型应用场合的需求,影响了信息的有效穿在。对于这种情况,本文提出了一种基于FPGA的工业实时以太网通信模块,立足标准以太网,通过定时器实现PLC主从站之间通信的周期性,可以显著提升通信速率。

关键词:FPGA;工业实时通信模块;设计

中图分类号:TP202 文献标识码:A 文章编号:1006-8937(2016)32-0066-02

1 概 述

在当前的技术条件下,PLC内部通信采用的多是分层结构,将通信分为不同插箱之间的通信以及插箱内部各个模块之间的通信,而传统PLC采用的是单层通信模式,在不同插箱之间利用CAN总线实现串联通信,不仅通信距离短,而且通信的速率不高,通常仅能达到500 Kbps,在这种情况下,系统扫描一个模件所需的时间约为1.6 ms,信息传输存在着很大的滞后性。如果利用通讯速率100 Mbps的工业实时以太网,在同等条件下,完成所有模件扫描的时间也仅需0.8 ms,通信速率得到了极大的提升。因此,针对当前CAN总线通信效率低下的问题,可以结合FPGA技术,将其升级为工业实时以太网,在提升通信速率的同时,满足工业现场的各种复杂需求。

2 基于FPGA的工业实时通信模块设计

FPGA,全称Field Programmable Gate Array,即现场可编程逻辑门阵列,属于一种比较特殊的半导体,在其中含有可以根据用户需求进行编辑的元件,其在程序编辑方面具有设计周期短,便捷方便,修改简单等特点。在实际应用中,FPGA相比较ASIC(专用集成短路)的响应速度要慢,实现同样的功能也需要更大的面积,不过其同样具有非常显著的优势,如能够实现快速成品,成本更加低廉,可以对程序中存在的错误进行改正等。考虑到通信接口模块本身的连接的受控模块较多,其各自的接口形式和通信协议存在着一定的区别,加上部分数据对于通信延时有着较高的要求,可以采用具备较强灵活性的FPGA技术,进行工业实时以太网通信模块的设计,需要从硬件和软件两个方面进行考虑[1]。

2.1 硬件结构

主控芯片选择Xilinx公司的Spartan-6XC6SLX45 FPGA,外部存储器选择DDR3 SRAM芯片MT41J64M16LA-187EIT以及Flash芯片25P64V6P。在网路芯片的选择种,采用了100M单物理层芯片的方案,选择PHY芯片DP8363SQ,以IP core在FPGA内部实现Ethernet MAC,与PHY芯片通过RMII接口连接在一起。

这里的Microblaze是基于Xilinx公司FPGA的微处理器IP核,采用RISC架构以及哈佛结构的32位指令及数据总线,能够对存储在片上存储器和外部存储器中的程序进行全速执行,同时对其中的数据进行访问。系统CPU设置有大量的外部设备,如SRAM、Flash、MAC等,系统为每一个设备分配了独有的地质,CPU对于各个设备的访问可以看做是相应地址的操作过程。

以太网IP core AXI Ethernet Lite MAC支持IEEE802.3标准,可以结合简化媒体独立结构,与工业标准PHY芯片连接,通过AXI4-Lite以及Microblaze实现相互之间的信息传递,支持10M乃至100 M的以太网通讯速率。IP核采用同步设计,为了确保以太网的通信速率能够达到最大的100 Mbps,系统时钟频率设置为50 Mbps。本系统硬件平台的搭设以及软件应用程序的开发都是在嵌入式软件开发工具EDK中实现的,硬件平台的搭设环境为XPS,软件程度的开发环境为SDK。

2.2 软件设计

2.2.1 数据接收与发送

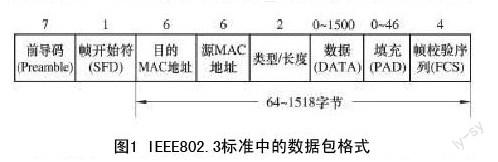

在通信模块中,软件设计主要是实现PHY芯片的初始化,确保其能够对以太网接收中断处理函数进行定义,同时以实现以太网接收中断的初始化。初始化主要是针对以太网MAC数据帧而言,在IEEE802.3标准中,数据包的格式类型,如图1所示。

在系统中,以太网接收数据端为PHY_dv,在程序运行时,会首先判断PHY_dv是否置1,如果置1则可以进行数据帧的接收,接收完成后,MAC会自动进行自身目的地地址与数据帧目的地地址的对比,如果无法匹配,则地址无效,会将接收到的数据全部丢失,重新接收;如果匹配,MAC会针对数据帧进行CRC计算,并且继续与接收到的数据帧的帧校验序列FCS中的CRC进行比对,若匹配,完成数据接收,若不匹配,表明FCS错误,重新接收数据[2]。

MAC对于数据帧的发送主要是依照以太网CSMA/CD技术。

2.2.2 周期同步处理

在标准以太网中,数据发送采用的是CSMA/CD技术,当网络负荷不高时,很少发生冲突,基本上能够满足对于通信实时性的要求。但是,在工业现场,具有容量巨大、传输速率快、IO点众多的特点,网络的负荷通常都比较重,容易发生冲突问题,从而造成网络性能的下降。考虑到冲突和处理的随机性以及网络通信延时的不确定性,想要保证通信的实时性非常困难。

因此,在通信模块的设计中,将定时器定义在顶层应用程序,从主站定期向从站发送数据,从站在接收到数据后,立即向主站回发数据。如果主站在向从站发送数据局后,在设定好的时间内没有接收到从站回发的数据,则此次数据发送失败,产生错误,主站会在将错误的计数器加8后,继续进行下一个节点的数据传输、如果其中一个从站出现连续数据发送错误,在不断的累计错误会移出,主站就可以判定从站断线,发送相应的警报信息,通知工作人员进行处理。

2.2.3 以太网收发测试

以太网数据帧是以一种字节增序的方式存储在TX buffer中,AXI Ethernet Lite MAC接受到的以太网数据帧同样会以增序的方式存储其中。数据发送的主要程序如下:

int main()

{

Initialize();

u32 i;

while(1)

{

for(i=0;i<1000;i++)

{

EmacRegisterWrite(0x07fc,0x01);

while(EmacRegisterRead(0x07fc)﹠(0x01)){}

}

}

return 0;

}

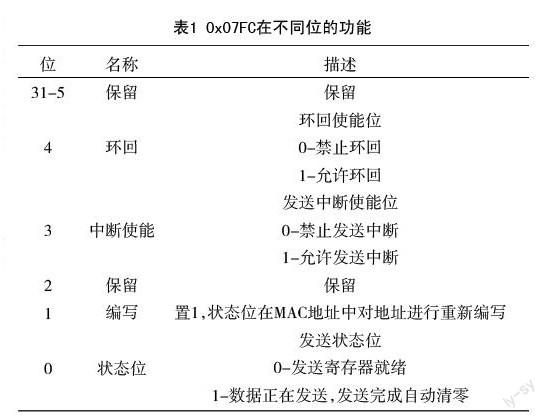

寄存器0x07FC是发送控制寄存器,上述程序中的EmacRegisterWrite(0x07fc,0x01)所表述的韩式是对0x07FC的第0位置1进行数据的发送,数据帧发送完成后,该位会自动置1。0x07FC在不同位的功能,见表1。

在程序中,对于MAC寄存器写入数据0a0a0a……即需要通过以太网发送的数据,可以对其进行任意赋值。这里将其赋值为1 038,包含了数据帧的头尾,实际数据长度为1 024.在程序中,对于目标地址的赋值为ff-ff-ff-ff-ff-ff-ff,源地址赋值00-00-5E-00-00-00。在FPGA中下载程序,结合wireshark抓包工具,就可以对发出的数据帧进行查看。

当PHY接收到一个数据帧后,会立即回发五帧数据,这里的寄存器0x17FC即为接收控制寄存器,其在不同位的功能如下:

0位即状态位,0-接收寄存器就绪,1-数据正在接收,接收完成自动清零;1-2位属于保留位,对接收的信息进行保留;3位为中断使能,0-禁止接收中断,1-允许接收中断;4-31位同样为保留位。

对程序进行编辑制定,同样结合wireshark抓包工具,可以看到接收一帧数据同时回发五帧数据的过程[3]。

3 结 语

综上所述,本文基于FPGA,针对工业实时以太网通信模块进行了设计和开发,利用以太网通信来取代传统PLC中的扩展总线CAN网,能够极大的提升PLC的通信速率,满足工业现场对于通信实时性的需求。经过测试,本文提出的方案具有良好的实践效果。

参考文献:

[1] 张伟.基于FPGA的通信接口模块设计与实现[J].电子科技,2012,25(7):

95-98.

[2] 王琦,徐潔,彭文才,等.基于FPGA的工业实时以太网通信模块设计[J].

水电自动化与大坝监测,2014,38(5):62-66.

[3] 贺永鹏,张向前,张凯,等.一种基于FPGA的嵌入式实时以太网[J].电气 传动,2015,45(7):70-73.