基于DDS的三角函数发生器的数字实现

尹自强(中国电子科技集团公司第四十七研究所,沈阳 110032)

基于DDS的三角函数发生器的数字实现

尹自强

(中国电子科技集团公司第四十七研究所,沈阳110032)

摘 要:函数信号发生器是一种常用的信号源,广泛应用于各种电子系统中,三角函数发生器是函数发生器中最为常用的一种。随着电子技术的发展,传统的函数发生器已经不能满足电子系统应用的需要,基于直接频率合成技术的函数发生器,由于可以获得很高的频率稳定度以及精确度,因此发展迅速。介绍了一种基于FPGA的三角函数信号发生器,具体分析了DDS算法原理,用verilog语言实现了相位累加器和波形存储器两个模块的设计,借助MATLAB软件生成了波形存储器中的三角函数波形数值,利用Synplify和ModelSim作为软件平台,对设计进行了综合和仿真。

关键词:DDS技术;三角函数;相位累加器;波形存储器;Verilog语言

1 引 言

三角函数数字发生器有多种实现方法,例如用分立元件实现,用单片集成芯片的函数发生器实现或者用基于DDS的函数发生器实现[1]。其中DDS技术是一种纯数字的频率合成方法[2],随着数字集成电路和微电子工艺技术的发展,DDS技术日益显露出它的优越性。与传统的函数发生器相比,DDS具有低功耗、高分辨率以及转换速度快等优点[3],同时方便在FPGA电路中实现,可以广泛应用于各类电子系统中。

2 DDS算法原理

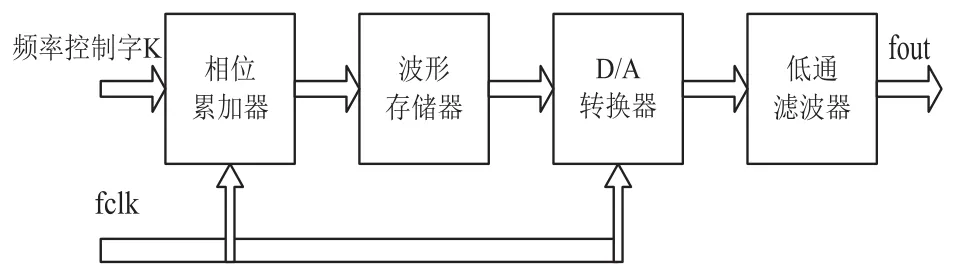

DDS主要由四个部分组成[4],如图1所示,分别为相位累加器、波形存储器、D/A转换器和低通滤波器。它的工作原理为:在时钟fclk驱动下,频率控制字K通过相位累加器进行累加,输出结果给波形存储器进行寻址,得到相应的输出幅度码,再经过模数转换器得到相应的阶梯波,最后再通过低通滤波器对波形进行平滑化处理,得到连续平滑的波形[5]。

图1 DDS原理框图

图1中的DDS算法,前两个部分可以在FPGA电路中实现,D/A转换器和滤波器一般在FPGA电路的外围电路来实现。D/A转换器是波形数据产生单元之后,将数字量形式的波形幅值转换成所要求的合成频率的模拟量信号形式。滤波器可以使有用频率信号通过,同时抑制无用的频率信号。主要讨论相位累加器和波形存储器在FPGA中的具体实现。

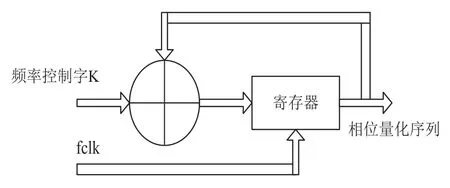

2.1相位累加器

相位累加器由N位加法器与N位寄存器级联组成[6],结构如图2所示,加法器将频率控制字和寄存器输出相加,一个时钟脉冲后,相加结果输入到寄存器中,同时加法器继续相加的操作。这样,相位累加器在时钟作用下,不断对频率控制字进行线性累加,输出一组相位量化序列。

图2 相位累加器框图

2.2波形存储器

相位累加器输出的相位量化序列作为波形存储器(ROM)的相位取样地址,通过地址读出ROM里存储的波形值,完成相位到幅值的转换,如图3所示。

图3 相位累加器框图

波形存储器所储存的幅度值和余弦信号有关[7]。一个N位的相位累加器对应2N个相位点,相位分辨率为Δφ=2π/2N。若N =4,则共有16种相位值与16种幅度值相对应,并将相应的幅度值存储于波形存储器[8]。余弦信号幅度值用MATLAB软件产生。

DDS模块的输出频率fout是系统工作频率fclk、相位累加器位数N以及频率控制字K三者的一个函数,其数学关系式为:

波形存储器的输出送到D/A转换器,将数字量形式的波形幅值转换为模拟量形式的信号,然后经过低通滤波,滤除不需要的取样分量。

3 三角函数发生器设计方法分析及具体实现

主要讨论了三角函数发生器在FPGA上的具体实现,也就是图1中前2个部分相位累加器和波形存储器的具体实现。

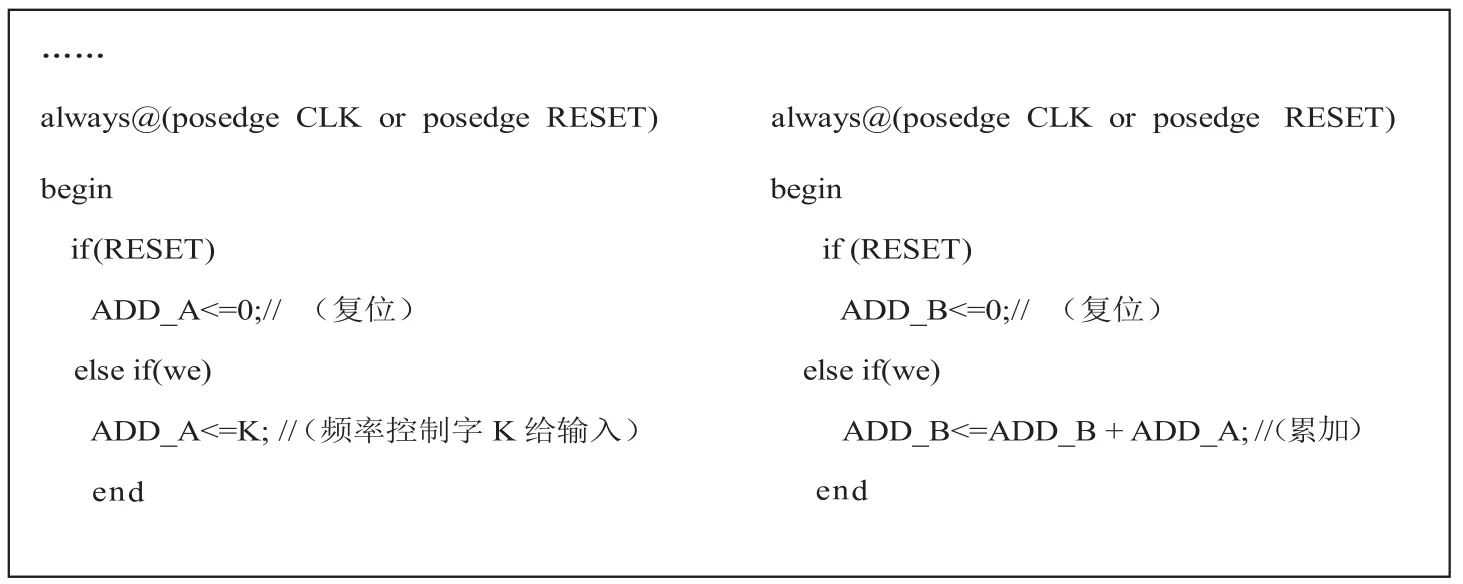

3.1相位累加器的实现

相位累加器可以认为是一个不断累加频率控制字的加法器。每来一个时钟脉冲CLK,加法器就将频率控制字K与累加寄存器输出相累加。相位累加器的溢出频率就是DDS的输出信号频率。这样就可以使DDS输出频率可调。

具体实现用verilog语言描述,如图4所示。

图4 相位累加器的verilog实现

3.2波形存储器的实现

波形存储器较为简单,首先用matlab软件生成正余弦的ROM文件,然后通过相位累加器产生的地址去ROM中寻址,将得到的值输出即为波形存储器的输出值。

具体实现用verilog语言描述,如图5所示。左边为对ROM寻址,右边为寻址得到的输出值(只给出了余弦,正弦类似)。

3.3整体电路的实现

用verilog语言实现了基于DDS技术的三角函数发生器中相位累加器和波形存储器两个模块的设计,如图6所示。设计共分为三个部分,一个顶层模块dds,实现DDS的主体功能,另外两个部分为rom_ cose和ron_sine,这两个模块是三角函数波形存储器,分别存储了余弦和正弦的波形幅度值。顶层模块调用另外两个模块。

图5 波形存储器的verilog实现

图6 DDS三角函数发生器的verilog实现

图7为程序经过软件综合后的RTL结构示意图。

图7 三角函数发生器的RTL结构图

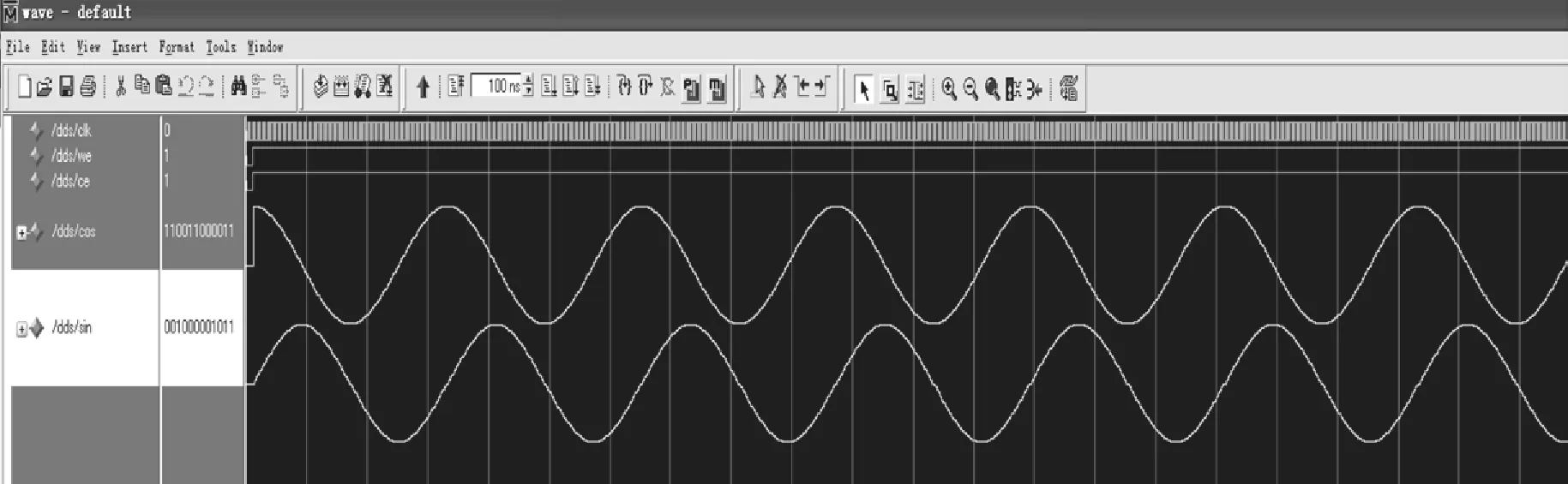

图8为在ModelSim中进行仿真得到的仿真结果,从图中可以看到,实现了输出正弦和余弦三角函数波形,证明了设计的三角函数发生器是正确的。

图8 DDS三角函数发生器的仿真结果

4 结束语

分析了DDS的算法原理以及各个部分的功能,进一步对三角函数发生器的数字模块进行了分析及实现介绍,在此基础上完成了基于FPGA的三角函数发生器设计,通过Synplify软件对设计进行了综合,用ModelSim软件对设计进行了仿真,验证了设计的正确性。

参考文献:

[1]张厥盛,曹丽娜.锁相与频率合成技术[M].成都:电子科技大学出版社,2000.ZHANG Juesheng,CAO Lina.Phase Locking and Frequency Synthesis Technology[M].Chengdu:University of Electronic Science and Technology Press,2000.

[2]田大方,祝忠明.一种基于FPGA的信号发生器的设计方法[J].电子质量,2012(4):27-30.TIAN Dafang,ZHU Zhongming.Design of Signal Generator Based on FPGA[J].Electronics Technology and Quality Engineering,2012(4):27-30.

[3]刘光辉.并行DDS频率源技术研究[D].成都:电子科技大学,2002.LIU Guanghui.Study of Coordinate DDSs Technology [D].Chengdu:University of Electronic Science and Technology,2002.

[4]陶益凡.基于DDS的信号发生器的研制[D].南京:南京信息工程大学,2006.Tao Yifan.Research about Signal Synthesizer Based on DDS[D].Nanjing:Nanjing University of Information Science and Technology,2006.

[5]屈新建,常义林.基于DDS + PLL频率合成源的设计[J].现代电子技术,2005(3):115-117.QU Xinjian,CHANG Yilin.Frequency Synthesizer of DDS Plus PLL[J].Modern Electronic Technique,2005(3):115-117.

[6]栾宝宽,方蕾,冯永浩.基于DDS的信号发生器的设计与实现[J].电子工程师,2005(10):38-39.LUAN Baokuan,FANG Lei,FENG Yonghao.Design and Implementation of Signal Generator Based on DDS[J].Electronic Engineer,2005(10):38-39.

[7]王晓升,沙胜贤.基于DDS的任意波形发生器实现[J].长春工程学院学报(自然科学版),2005(2):56-58.WANG Xiaosheng,Sha Shengxian.Realization of a ware Waves Generator Based on DDS[J].Changchun Inst.Tech.(Nat.Sci.Edi.),2005(2):56-58.

[8]薛文.DDS任意波形的设计与实现[D].南京:南京信息工程大学,2004.XUE Wen.Design and Realization of DDS Arbitrary Waveform[D].Nanjing:Nanjing University of Information Science and Technology,2004.

Realization of Trigonometric Function Generator Based on DDS

Yin Ziqiang

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

Abstract:The signal generator,as a common signal source,is widely used in electronic system.The trigonometric function generator,as one of the signal generators,is used commonly.With the development of electronic technology,traditional function generator doesn't meet the needs of electronic systems.The function generator based on DDS,because of the high stability and accuracy of frequency,is developed rapidly.This paper introduces a trigonometric function generator based on FPGA,concretely analyzes the algorithm of DDS,designs the phase accumulator and ROM with verilog language,uses MATLAB to generate wave value of trigonometric function in ROM,and applies Synplify and ModelSim as the soft platform to synthesize and simulate the design.

Key words:DDS technology;Trigonometric function;Phase accumulator;Wave memory;Verilog language

DOI:10.3969/j.issn.1002-2279.2016.02.004

中图分类号:TP346

文献标识码:A

文章编号:1002-2279(2016)02-0011-03

作者简介:尹自强(1983-),男,内蒙古包头市人,工程师,硕士研究生,主研方向:集成电路设计。

收稿日期:2015-09-16