基于Verilog的FIR数字滤波器设计与仿真

何蕴良,耿淑琴,汪金辉(北京工业大学电子信息与控制工程学院,北京 100022)

基于Verilog的FIR数字滤波器设计与仿真

何蕴良,耿淑琴,汪金辉

(北京工业大学电子信息与控制工程学院,北京100022)

摘要:设计一种基于Verilog的FIR数字低通滤波器。在结构上改变了以往乘法器和加法器的简单结合,利用分布式算法构造查找表进行乘累加运算,节约资源占用并且提高运算速率。利用Matlab工具设计和获取滤波器参数,并且进行仿真验证。滤波器参数量化后形成查找表,利用Verilog HDL语言对硬件电路模块进行设计描述,并且用ModelSim进行整个硬件电路系统的功能仿真,验证了设计的正确性。设计在速度和面积方面做了折中和优化,成功实现了数字滤波的功能。

关键词:Verilog;数字滤波器;分布式算法;FIR

从带有干扰的原始信号中提取有效信号并对其进行处理,几乎是所有科学技术领域都必然涉及的重要环节。信号处理的任务主要是对信号进行采样接收、频谱分析、域变换、综合和估值识别等[1]。现在的信号处理的系统主要分为两大类:模拟信号处理系统和数字信号处理系统。数字信号处理,主要是利用计算机或专用处理设备对数字信号进行分析、变换、综合、估计与识别等进行加工处理。数字信号处理的核心的内容主要是傅里叶变换和数字滤波。而其中数字滤波技术的主要任务是从带有噪声干扰的信号中提取所需要的有效信号,而抑制不需要的噪声信号。数字滤波器(Digital Filter)是用来对输入信号进行滤波的硬件或软件。它的输入和输出均为数字信号,并通过一定运算关系改变输入信号所含频率成分的器件[2]。与模拟滤波器相比,数字滤波器的处理的信号形式,实现滤波的方法不同,因此数字滤波器具有精度高、稳定,体积小、重量轻、灵活,不要求阻抗匹配等优点。数字滤波器在实验和现实的生产生活中起着广泛和重要的作用。

1 FIR数字滤波器原理及结构

1.1FIR数字滤波器原理和特点

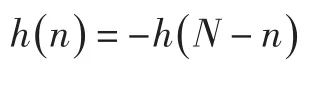

数字滤波器分为有限冲激响应(FIR)数字滤波器和无限冲激响应(IIR)数字滤波器两种,这两种滤波器均被广泛应用于数字信号处理系统中。IIR数字滤波器设计方便简单,但是它的相位具有非线性,所以要求全通网络进行相位的校正,而且它的稳定性难以保障。而FIR滤波器具有很好的线性相位特性,使得它越来越受到广泛的重视[3]。FIR数字滤波器是一个线性时不变系统,所以N阶因果有限冲激响应滤波器可以用传输函数H(z)来描述:

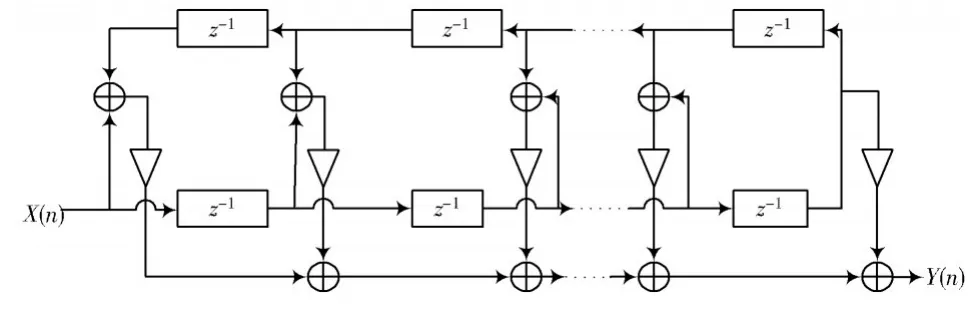

在时域中,上述有限冲激响应滤波器的输入/输出关系为:

式中:x(n)和y(n)分别是输入和输出序列。FIR滤波器的主要特点是:既具有严格的线性相位,又具有任意的幅度。它的单位抽样响应是有限长的,因而滤波器性能比较稳定。只要经过一定的延时,任何非因果有限长序列都能变成因果的有限长序列,因而能用因果系统来实现。它的单位冲击响应是有限长的,可用快速傅里叶变换来实现过滤信号,运算效率可以有很大提高。

1.2FIR数字滤波器结构

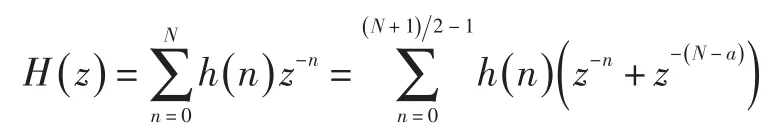

FIR数字滤波器的实现一般有直接型、转置型、线性相位型、级联和频率采样等[4]。乘法运算是实现滤波的关键方法,但是乘法运算占用电路资源很大,因此,在选择结构时,也要考虑到资源的占用。线性相位的FIR滤波器结构比一般直接型结构可以节省几乎一半的乘法次数,设计中选择了线性相位的FIR滤波结构。FIR滤波器的线性相位非常重要,数据的传输和图像处理都要求系统具有线性相位。由于FIR滤波器的冲激响应是有限长的,有可能做成严格线性相位。当冲击响应满足下列公式时,FIR滤波器具有对称结构,为线性相位滤波器;N阶线性相位的因果FIR系统的单位冲激响应滤波器的对称的冲激响应公式为:

或者反对称的冲激响应公式:

当N为偶数时:

当N为奇数时:

因此FIR线性相位系统的结构可转化成如图1和图2所示的电路图。

这样就实现了结构上的对称,因此减少了乘法次数。由于这种对称性,使得乘法器数量可以减半。乘法器的减少,意味着电路成本减少,可以提高电路的工作效率。

图1 FIR线性相位系统的结构(N为奇数)

图2 FIR线性相位系统的结构(N为偶数)

2 分布式算法

分布式算法是一项重要的FPGA技术,这种算法使得一般的乘积和计算在FPGA实施过程中不再需要通用乘法器[5]。分布式算法和传统实现乘累加运算的主要不同是:执行部分积运算的先后顺序不同。分布式算法完成乘累加功能是通过把输入数据每一个对应的位产生的部分积预先进行相加形成相应部分积,然后再对各部分产生的积相加起来得到最终结果。

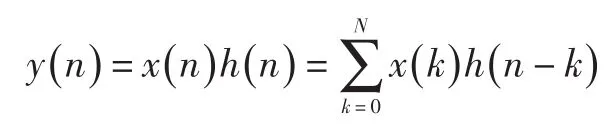

而传统的算法是在所有的乘积产生之后,再进行相加得到最后的结果。与传统算法相比,运用分布式算法之后可以极大地减少硬件电路规模,并且容易实现流水线处理,因而提高了电路执行的速度。对于FIR数字滤波器,基本结构是一个分节的延时线,每一节的输出加权累加,得到滤波器的输出。它的输出y就是输入x和系数h的内积:

输入数据x(n)可以采用B+1位补码来表示,即:

因为系数h(n)为已知常数,则内积y可以写成:

将上式中的第二部分展开,重新分别求和,这也是“分布式算法”名称的由来,可以得到:

化简为:

计算h(n)xb(n)的方法就是用查找表来实现一个映射,然后再将此映射得到的结果经过相应的二次幂加权,最后得到滤波器的输出。分布式算法在大规模集成电路实现中被广泛应用,它的显著优点包括可节约硬件资源,所实现硬件结构具有高度规整性,最小的传输延时和最少的跨区域连接等[6]。

3 滤波器参数提取和仿真

3.1滤波参数提取与量化

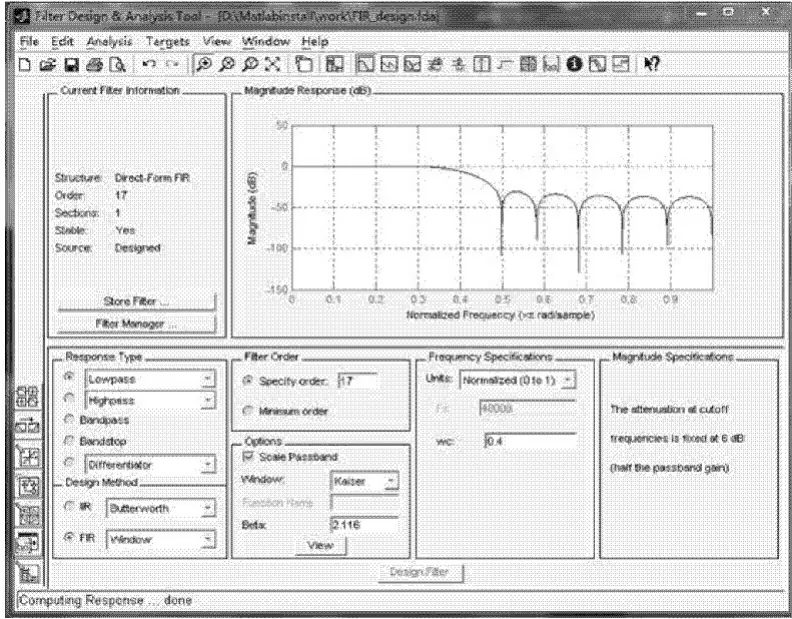

FIR滤波器系数计算是比较繁琐的,在设计时,可以借助Matlab工具箱,根据设计需求选择合适的窗函数,即可方便地计算滤波器系数,并分析幅频、相频特性[7]。采用Matlab中工具箱中的Filter Design来设计和提取滤波器参数。利用其中FDAtool工具可以设计出满足所需性能指标的滤波器。界面如图3所示。

图3 Toolboxes工具箱界面

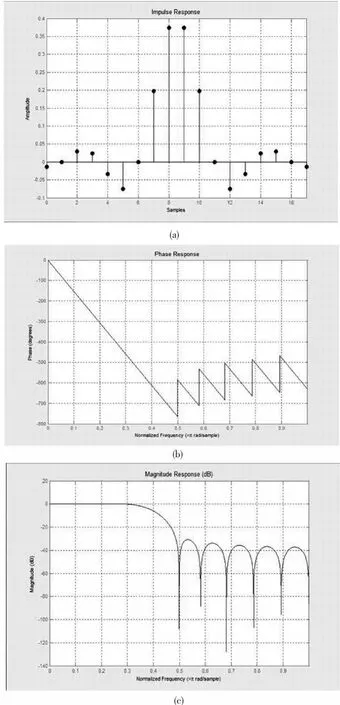

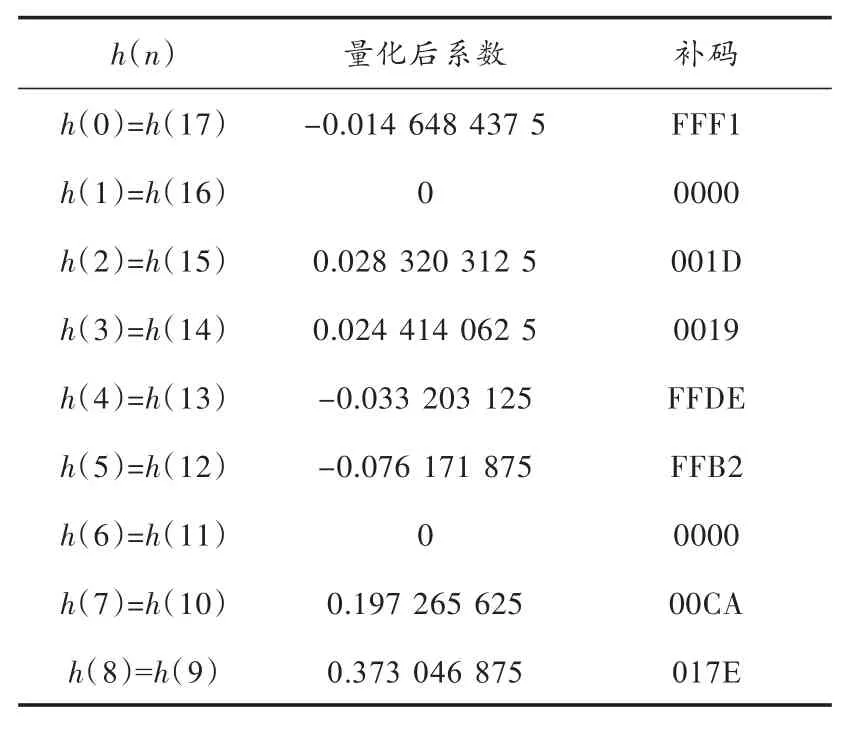

要设计的滤波器的参数如图3所示:设计低通滤波器,采用窗函数中的Kaiser窗来实现,Beta值为2.116,Wc为0.4。按照给定的参数设计数字滤波器,得到的冲击响应、线性相位和幅度响应如图4所示,可见第一旁瓣响应小于-30 dB,符合设计要求。由于Matlab计算得到的滤波系数均为有符号浮点值,但在后续利用硬件描述语言对数字滤波器进行RTL建模和功能仿真时,滤波系数都必须为定点值。因此,还需要将这些浮点形式的滤波系数定点量化[8]。将量化后转换成补码形式,得到的系数如表1所示。

3.2Matlab仿真和结果分析

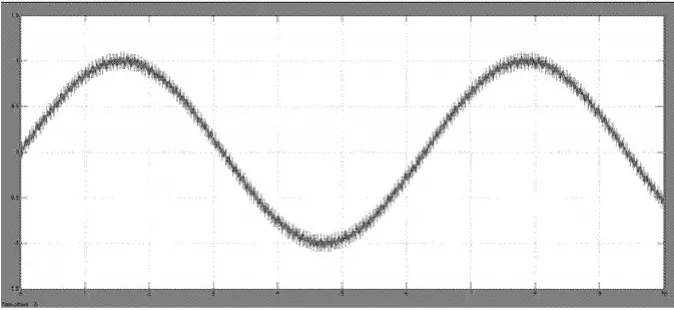

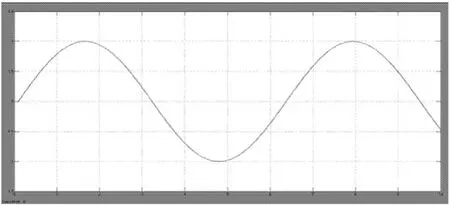

把设计的滤波器实例化,并在Matlab中Simulink工具下仿真,测试它是否可以完成滤波功能。搭建测试平台如图5所示。给定高频和低频两个测试信号,并将这两个测试信号混合,混合后的信号如图6所示。然后再通过滤波器,经过滤波器处理的信号如图7所示,观测输出信号是否可以成功地滤掉高频信号,保留理想的低频信号。

图4 滤波器的冲击响应、线性相位和幅度响应

表1 量化系数和补码表

图5 测试平台

图6 混合后的信号

图7 经过滤波的信号

4 模块描述和仿真

4.1模块描述

上文中证实了该数字滤波器功能的正确性,开始把整个设计划分成各个功能模块,并且定义各个模块的功能,然后对滤波器的各个功能模块进行硬件语言描述,形成各个模块的实例。

移位寄存模块的功能是将输入的数据在时钟的上升沿依次进行移位寄存,即就是产生一次数据延迟的过程。因为抽头系数的对称性,所以可以把首尾的输入系数预先进行相加处理,然后对这个预相加的结果再进行数据的处理,合二为一,这样可以节省芯片面积和运算时间。串并转换模块,把并行的数据转化为串行的数据,然后输入到查找表中进行查找。查找表模块,该模块的作用是对输入的数据进行查找,输出查找表结果。查找表结构相加模块的功能是把查找表中输出的数据进行相加。

计算模块的功能是把相加后的数据进行加或者减操作,输出最终的结果。整合好的电路顶层连接如图8所示。

图8 电路顶层连接框图

4.2电路仿真

将测试数据依次送到输入端,观察输出数据的结果,经过计算,输出结果和计算应得结果一致,准确无误,说明滤波器仿真功能正确,输入和输出信号见图9。

图9 电路仿真结果

5 结 语

本文设计实现了FIR数字低通滤波器,整个设计分成滤波器系数设计提取和滤波电路的Verilog实现。滤波系数设计提取利用Matlab工具,并用其进行仿真验证,证明该滤波算法原理的正确性。采用自顶向下的设计方法,将FIR滤波器系统划分为若干电路的模块,分别对各个模块进行Verilog设计实现,最后整合成整个滤波器电路,经过仿真验证了其功能的正确性。

参考文献

[1]戴明祯.数字信号处理的硬件实现[M].北京:航空工业出版社,1998.

[2]刘朋全.基于FPGA的FIR数字滤波器的设计和实现[D].西安:西北工业大学,2006.

[3]王旭东,潘明海.数字信号处理的FPGA实现[M].北京:清华大学出版社,2011.

[4]刘福泉.基于FPGA的FIR数字滤波器实现[D].北京:北京邮电大学,2012.

[5]王一海,俞筱楠,姜志鹏.并行分布式算法FIR滤波器的FPGA实现[J].电子器件,2012,35(5):545⁃548.

[6]王天云.基于分布式算法FIR滤波器的FPGA实现[J].舰船电子工程,2005,25(5):107⁃110.

[7]孙耀奇,高火涛,熊超,等.基于Matlab和FPGA的FIR数字滤波器设计及实现[J].现代电子技术,2008,31(11):89⁃92.

[8]王赟松.FIR数字滤波器设计[D].西安:西安电子科技大学,2012.

Design and simulation of FIR digital filter based on Verilog

HE Yunliang,GENG Shuqin,WANG Jinhui

(College of Electronic Information & Control Engineering,Beijing University of Technology,Beijing 100022,China)

Abstract:A FIR digital low⁃pass filter based on Verilog was designed and changed in its the structure. It isn’t a commonly used simple combination of multipliers and adders,but the distributed algorithm was used to construct a lookup table to achieve the multiply⁃accumulate operation. Resource occupation was reduced and the operating rate was improved by this way. The Mat⁃lab was used to obtain parameters of the filter. The look⁃up table is formed by quantification of the parameters. The hardware cir⁃cuit modules are designed and are described with Verilog HDL. The functional simulation of the whole hardware circuit system was conducted to verify correctness of the design by ModelSim. A compromise and optimization in speed and area were made,by which the functions of digital filtering were achieved successfully.

Keywords:Verilog;digital filter;distributed algorithm;FIR

中图分类号:TN713⁃34

文献标识码:A

文章编号:1004⁃373X(2016)10⁃0001⁃04

doi:10.16652/j.issn.1004⁃373x.2016.10.001

收稿日期:2015⁃09⁃06

基金项目:国家自然科学基金(61204040;60976028);教育部博士点基金(20121103120018);北京市教育委员会科技计划面上项目(JC002999201301);北京市自然科学基金资助(4152004)

作者简介:何蕴良(1991—),男,河北秦皇岛人,硕士研究生。研究方向为集成电路设计与系统。耿淑琴(1970—),女,山西运城人,博士。研究方向为集成电路设计与系统、无线传感网络等。汪金辉(1982—),男,河北唐山人,副教授,博士。研究方向为集成电路设计、嵌入式系统等。