基于FPGA的频率采集电路和逻辑设计

陈奎 孙沛 郭警涛 邓道杰

摘 要:机载机电系统中频率采集是机电参数采集中关键技术之一,针对系统频率采集不准会导致机电系统电源保护、动力系统工作状态不稳定的情况。本文提出一种新的方法进行系统频率采集,首先,将被测频率信号经过E3防护、滤波、限幅、比较等硬件电路进行波形的转换,其次,在FPGA中对输入信号进行同步和滤波,最后,使用周期计数法完成频率测量。该频率采集电路和逻辑设计技术具有集成度高、测频范围广、精度高和可靠性高的特点,目前已成功应用于机载产品中。

关键词:频率采集;同步滤波;周期计数法测频

随着机电综合的发展,机电系统对频率采集的要求越来越高,不仅要采集电源系统的交流电源频率,还要采集动力系统的发动机转速信号的频率采集。急需研制一种电压接口范围广、采集频率范围宽以及抗干扰能力强的高精度频率采集电路和逻辑设计技术。

传统的频率测量电路一般采用模拟电路或处理器直接捕获的方法实现,这种方法的缺点为:采集精度低、相应周期长,抗干扰能力差以及增大处理器开销等缺点。

本设计能有效的提高信号采集抗干扰能力、提高采集精度、減小处理器开销等特点,并具备接口电压范围广、采集频率范围宽等特点。

1 频率采集电路设计

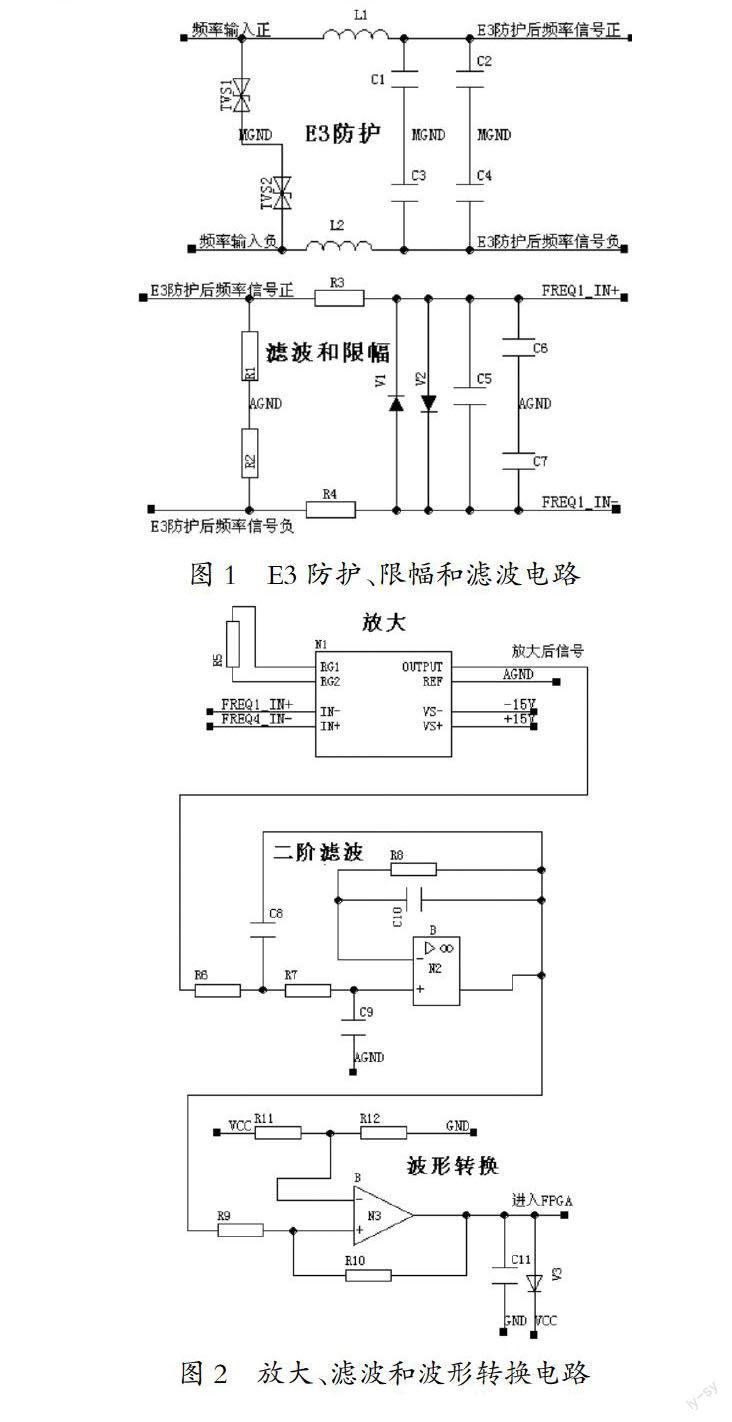

机载机电系统频率采集电路共分为:E3防护、限幅、滤波、放大、二阶滤波、波形转换等功能模块。E3防护、限幅和滤波电路如图1所示,放大、二阶滤波和波形转换电路如图2所示。

1.1 E3防护电路设计

如图1所示,在E3防护电路中首先采用两个瞬态抑制二极管TVS1、TVS2将正负信号线对地连接,根据不同的闪电能量要求可以选择不同功率的瞬态抑制二极管。当外界有瞬时高电压时,TVS1、TVS2迅速开启,对地导通,将能量传递到产品外壳,完成对后电路的防护。

在瞬态抑制二极管后面,分别在输入信号的正负线上串入电感L1、L2。在输入信号瞬时突变时,形成“短路”效应,配合瞬态抑制二极管完成对后级电路的保护。

在电感的后级,分别在输入信号的正负线对地并联两个不同容值的电容,主要完成高频干扰信号的能力吸收,防护后级电路。

1.2 限幅和滤波电路设计

如图1所示,在限幅和滤波电路中首先在频率信号的正负端对地之间设置两个兆欧级的电阻R1、R2,通过这两个电阻将暂时存储在C1、C2、C3、C4高频干扰能力释放掉,避免因能量积累对输入信号质量产生的影响。

然后分别在频率信号的正负线上串入千欧级的电阻R3、R4,并在该电阻后配置两个正反互异的二极管V1、V2。在该设计下,当输入频率为正半波时,R3、V2、R4形成回路,二极管V2两端被限幅到0.7V左右,二极管V1不工作,其余电压被分压到电阻R3、R4。当输入频率为负半波时,R3、V1、R4形成回路,二极管V1两端被限幅到-0.7V左右,二极管V2不工作,其余电压被分压到电阻R3、R4。

在该电路中R3、R4和C5形成差模滤波电路,截止频率为:fdiff=1/[2π((R1+R2)C5)],其中电阻和电容的值可以根据需要进行调整。R3、R4、C6、C7形成共模滤波电路,截止频率为:fcm=1/(2πR3+C6)=1/(2πR4+C7),其中电阻和电容的值可以根据需要进行调整。

1.3 放大电路设计

如图2所示,在放大电路的输入端频率信号被限幅到-0.7V到+0.7V之间,在该放大电路中采用差分放大器件,放大倍数设置为12倍,放大后的信号幅值范围为:-8.4V到+8.4V之间,便于后级对信号处理,其中差分放大器的放大倍数具备可配置性,可以根据需要通过设置R5的阻值来设置放大倍数,以满足不同的信号处理需求。

1.4 二阶滤波电路设计

如图2所示,在放大电路后级配置二阶滤波电路,其中R6、R7、C8、C9、N2构成二阶滤波电路,主要完成对放大后的信号进行滤波,截止频率为:f=1/(2π■,其中R6、R7的阻值相同,C8、C9的容值相同。根据输入频率信号的范围,选取合适电阻和电容值,配置成不同截止频率的二阶滤波电路,满足系统设计需求。

1.5 波形转换电路设计

如图2所示,在二阶滤波电路的后级设置波形转换电路,其中R9、R10、R11、R12、N3构成波形转换电路,将输入的正弦信号转化方波信号,并通过二极管V3进行限幅,通过电容C11进行滤波处理,将处理后的方波输入到FPGA中采集。

在该电路中通过电阻R11、R12对VCC进行分压,将分压后电压值作为比较的基准,通过电阻R9、R10对二阶滤波后的信号进行分压处理,再和基准进行比较,通过N3形成方波。在该比较电路中设置了门限比较,该设计能够过滤掉输入信号中夹杂的低幅值杂波,避免过零比较电路中出现的信号采集不稳定。

2 频率采集逻辑设计

在FPGA内部,逻辑采用VHDL语言实现,通过周期计数器的方法完成频率测量。周期计算法的原理为:利用基频对被测信号的一个周期进行计数,得到一个周期内的计数值,并根据计数值计算出被测信号频率,计算公式为:被测信号频率等于计数值和基频周期的乘积倒数,也可换算为:基频时钟周期除以计数值的商。计数值可根据精度需求配置不同的位数,一般可设置为16位或32位。

在捕获被测信号周期时,由于前面采用非过零比较电路,则输入到FPGA的方波占空比非50%,需要将输入的频率信号FRE1200进行二分频处理,变为FRE1200/2信号,并对FRE1200/2信号进行测量,从该信号的上升沿开始计数,并在高电平内保持计数,在FRE1200/2信号的下降沿锁存当前计数值,完成对被测频率一个周期的计数。传统二分频的逻辑实现如下:

FRE1200_DIV:process(SYSCLK,RESET_L)

begin

if RESET_L = '0' then

div1200 <= '0' ;

elsif fre1200'event and fre1200 = '1' then

div1200 <= not div1200 ;

end if;

end process FRE1200_DIV;

通过测量发现,在该逻辑实现中,由于被测频率信号有时会存在毛刺,该毛刺被逻辑捕获,被误判一个频率周期,导致频率测试结果不准确,影响采集结果。

为了解决这一问题,在传统的二分频逻辑中增加了两个延时信号,对被测信号的毛刺进行两次滤波,从而将毛刺消除,确保测频结果准确,逻辑实现方法如下:

process

begin

wait until SYSCLK'event and SYSCLK

= '1' ;

fre1200_sync0 <= fre1200 ;

fre1200_sync1 <= fre1200_sync0 ;

end process ;

FRE1200_DIV:process(SYSCLK,RESET_L)

begin

if RESET_L = '0' then

div1200 <= '0' ;

elsif SYSCLK'event and SYSCLK = '1' then

if (fre1200_sync0 = '1') and (fre1200_sync1 = '1') then

div1200 <= not div1200 ;

end if ;

end if;

end process FRE1200_DIV;

采用優化后的逻辑算法有效的解决了信号毛刺对采集精度的影响。

3 结语

本文在从频率采集的硬件实现和逻辑实现的基础上,通过对硬件电路设计的优化研究,在硬件电路设计中配置了E3防护电路,使该电路具备了放雷电功能;在电路设计中配置了前级滤波、二阶滤波等电路,使该电路具备了抗干扰能力;在电路设计中配置了限幅电路,使得该电路具备更宽的电压接口能力。

目前使用这种集E3防护、抗干扰能力强、电压接口宽和抗毛刺能力强的频率采集电路和逻辑设计,已在某重点科研项目中成功运用,同时可以推广应用到其他领域中。

参考文献:

[1] 白勇,李玉忍,李瑞琴.基于FPGA的飞机轮速测量系统设计[J].微处理机.2011(03).

[2] 张华林.双偏振调制大范围高分辨率瞬时微波频率测量 [J].中国激光.2014(11).

[3] 范启亮.一种简易数字频率计的设计与实现[J].科技风.2014(20).

作者简介:

陈奎(1985-), 男, 安徽阜阳人,本科,工程师,研究方向:机载机电系统计算机;

孙沛(1984-), 男,陕西宝鸡人, 硕士,工程师,研究方向:机载机电系统计算机;

郭警涛(1981-),男,陕西礼泉人,硕士,工程师,从事计算机测量与控制;邓道杰(1991-),女,湖北荆门人,硕士,助理工程师,主要从事机载嵌入式设计。